半導体の全てをカバーしたSEMICON Japan報道が相次ぐ

先週は半導体関係最大のイベントであるSEMICON Japanの記事が相次いだが、日本経済新聞と日刊工業新聞の切り口が全く違った。また、Micron Technologyは最新技術を展示していた一方で、本社から決算発表があり、メモリビジネスの好調さをいち早く見せた。ラピダスへの民間融資の8割を政府が債務保証する方針だと12月19日の日経が報じた。 [→続きを読む]

先週は半導体関係最大のイベントであるSEMICON Japanの記事が相次いだが、日本経済新聞と日刊工業新聞の切り口が全く違った。また、Micron Technologyは最新技術を展示していた一方で、本社から決算発表があり、メモリビジネスの好調さをいち早く見せた。ラピダスへの民間融資の8割を政府が債務保証する方針だと12月19日の日経が報じた。 [→続きを読む]

SEMICON Japanにやってきた(図1)。その内容は、大きく変容している。元々、半導体装置及び材料メーカーが出展して、半導体プロセス技術者がバイヤーとなる展示会であったが、2025年のSEMICON Japanでは半導体メーカー、EDAベンダー、産業機械メーカーも出展しており、大きく変化している。OEMとサプライヤ、ユーザーが出展しており、それぞれの関係が崩れている。参加者は極めて多い、という印象だった。 [→続きを読む]

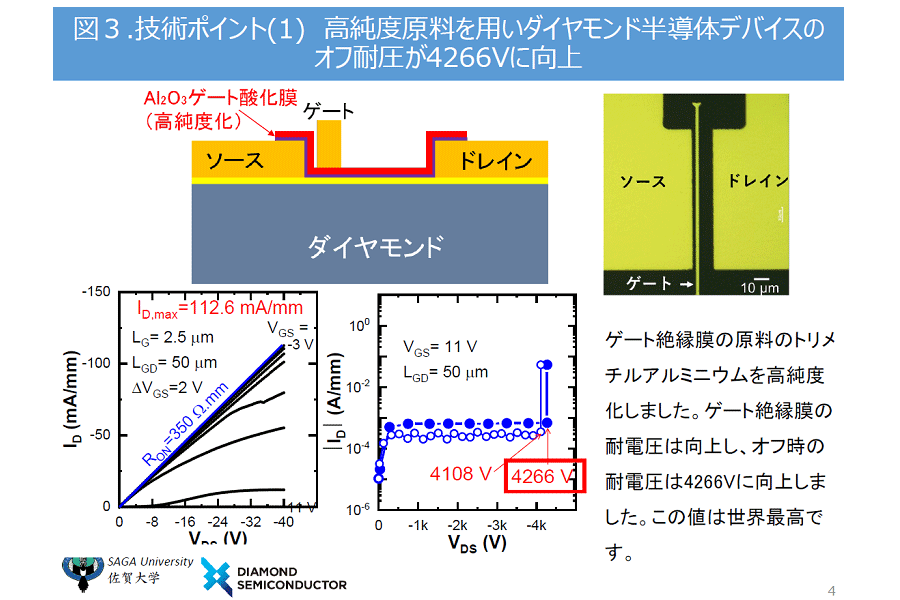

佐賀大学の嘉数誠教授らのグループは、ダイヤモンド結晶を使って半導体としてMOSトランジスタを試作し、その高周波特性を測定したところ、遮断周波数fMAXが120GHzを示した。ダイヤモンドはバンドギャップがシリコンの4.9倍もあり耐圧が高いため、パワー半導体への応用が期待されている。とはいえ、実際のトランジスタを形成することは簡単ではない。ゲート絶縁膜、n型/p型の形成などシリコンとは難しさが違う。 [→続きを読む]

ラピダスに民間企業22社が新規に出資、これまでの株主に加えて合計30社が株主になると12月13日の日本経済新聞が報じた。ラピダスはこれまでと同様、「当社が発表したものではない」とコメントを出している。TSMCが熊本第2工場に4nmプロセスを導入する検討をしている。Broadcomの評価が高まっている。AIチップ最大手のNvidiaのH200が中国輸出を認められたことに対して米国内で反発する声が高まっている。 [→続きを読む]

先週、セミコン台湾2025が開催され、AIがけん引する先端パッケージが注目されたようだ。9月11日の日本経済新聞は先端パッケージの講演が連日のように開かれたと報じた。特に3DICAMA(3DIC Advanced Manufacturing Alliance:先端製造アライアンス)を、TSMCとASEがリードして立ち上げた。日本でも広島大学がAIの普及で半導体需要が増えることから半導体システムを教えるプログラムを新設した。 [→続きを読む]

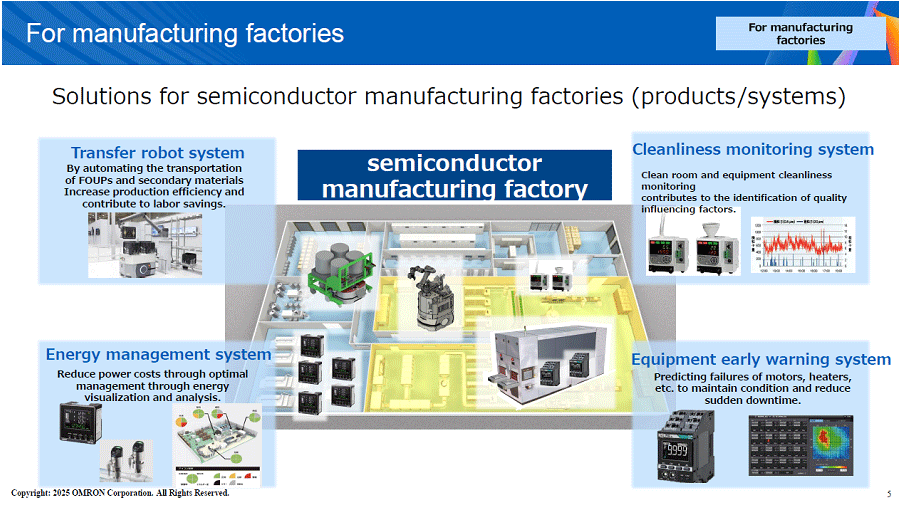

工業用のセンシングや制御機器に強いオムロンが半導体分野に力を入れる。会社として本格的に参入するため、半導体に特化した組織としてセミコンダクタ&インキュベーションセンタを2025年4月に設立した。同社は2021年、所有していた半導体工場をミネベアミツミに売却している。今なぜ半導体分野に再び進出するのだろうか。 [→続きを読む]

米中対立から、サプライチェーンをできる限り自国に持ってこようとする米中の動きが顕著になってきた。米アリゾナ州のTSMC工場は第2工場がすでに動き出し、第3工場への投資も出ているという。テキサス州でもIT各社による「スターゲート計画」と呼ぶAIデータセンターの街を作る計画がある。中国の自動車は国産半導体を100%に上げる方向にある。国内でもソニーが22nmのラインを動かし始める。 [→続きを読む]

東京大学とTSMCが共同のラボを浅野キャンパスに設けると発表した。TSMCと台湾以外の大学との共同ラボは初めて。東大にはこれまで材料や半導体物理、電子回路などで豊富な研究者がおり、TSMCにとっては共同できることが1.4nm以下のプロセスノードとなると東大とのコラボは心強い。東大にとってもVDECを通してチップ試作を依頼してきた。今回の特長は何か。 [→続きを読む]

米Intelがファウンドリをビジネスとして確立するためのパートナーとのエコシステムを、新CEOであるLip-Bu Tan氏が、このほど開催したIntel Foundry Direct Connectで明らかにした。同氏はIntelを、技術、カスタマフォーカスだけではなく企業文化も変えることを訴えており、ファウンドリとしてのパートナーとして、EDAトップ3社に加え、PDF Solutionsを紹介した。 [→続きを読む]

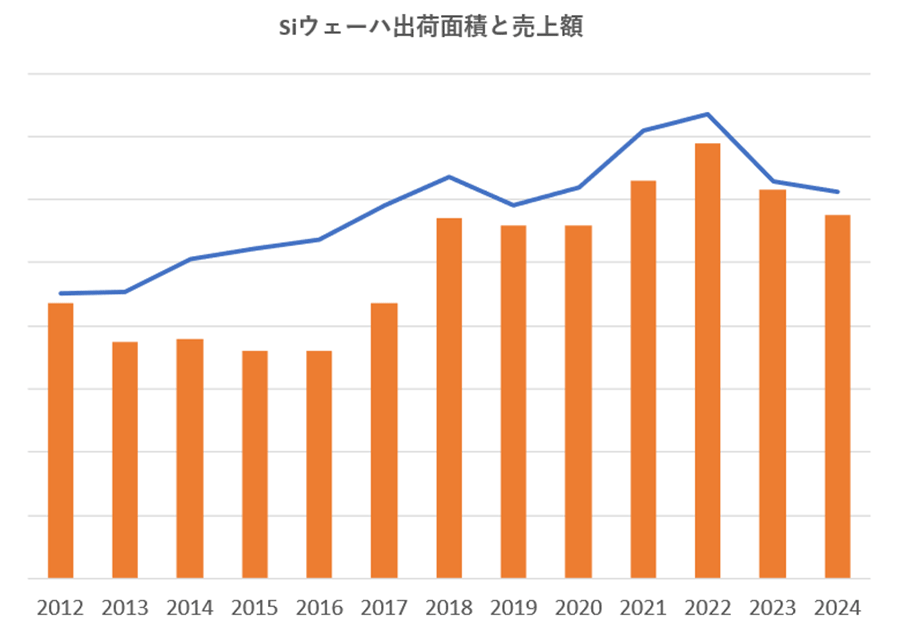

2024年におけるシリコン半導体ウェーハの出荷面積が前年比2.7%減の122億6600万平方インチだったとSEMIが発表した。その年のウェーハ売上額は同6.5%減の115億ドルだった。出荷面積の減少よりも出荷売上額の減少の方が大きいということは、在庫調整がゆっくりで、ファブの稼働率を上げるような大量生産品目のデバイス需要が弱かったことを意味する。 [→続きを読む]