2024年12月23日

|週間ニュース分析

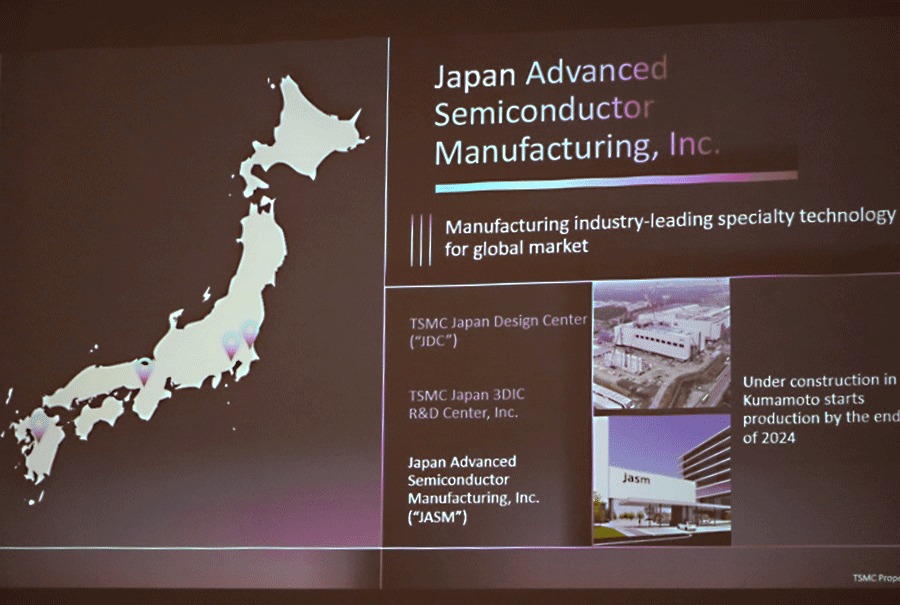

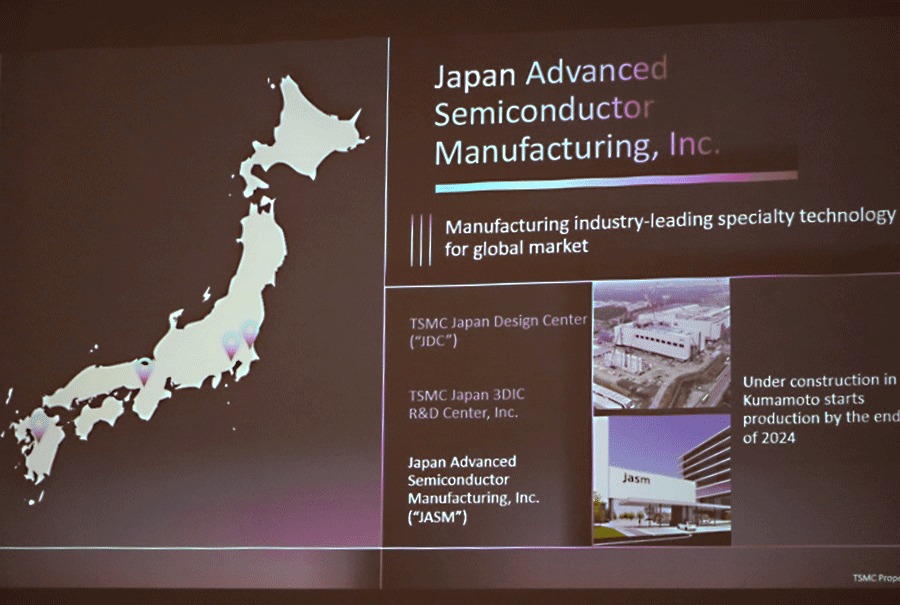

JEITA(電子情報技術産業協会)が12月19日に発表した世界の電子機器とソフトウエアやソリューションを合わせた電子情報産業の市場は、2025年に前年比8%増の3兆9909億ドルになる。TSMCの熊本工場が稼働し始めているが、九州に続々半導体プロセスに使う装置や材料の企業が続々集まっている。ラピダスにEUV装置が入り始め、関連企業もEUVに備えている。キオクシアは18日、東京証券取引所の東証プライム市場に上場した。

[→続きを読む]

2024年10月28日

|週間ニュース分析

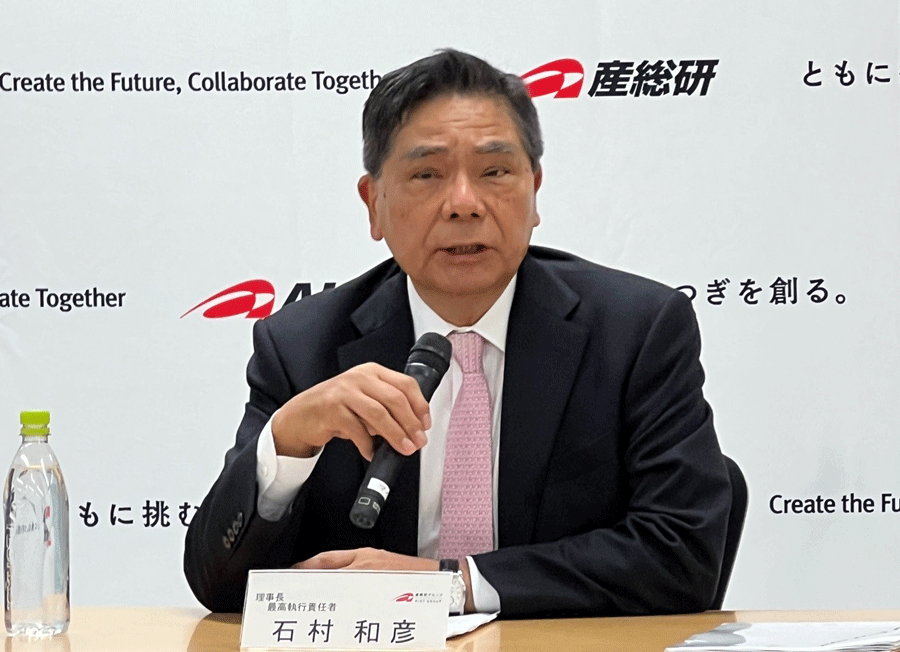

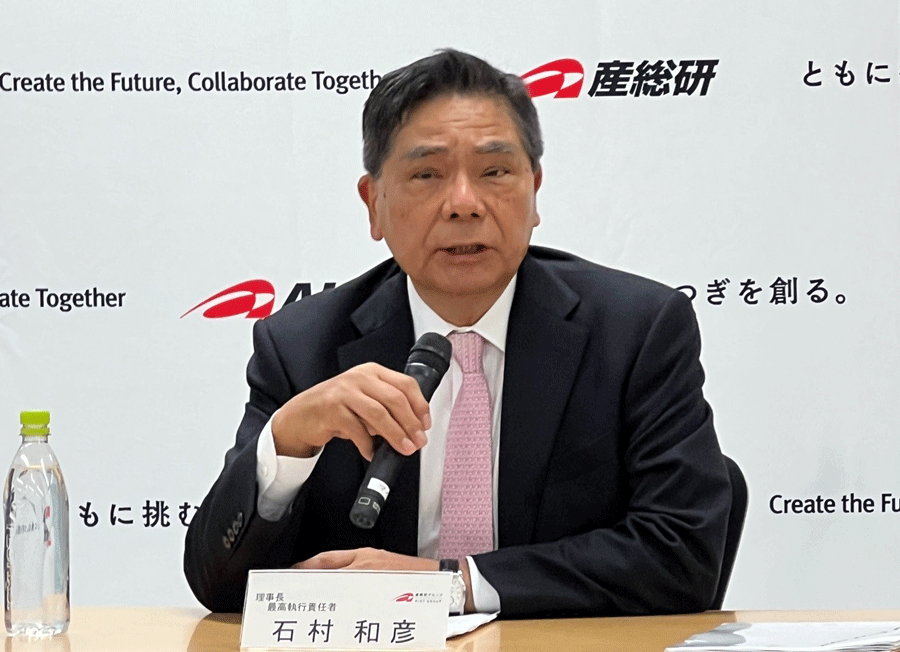

産業技術総合研究所がEUVリソグラフィを導入して5nm以下のプロセス開発を支援する、と22日の日本経済新聞が報じた。これはIntelとの共同で整備する先端半導体の研究開発拠点に導入する。1000億円を投じるという。一方、日本にファウンドリ工場を新設するとしていた台湾のPSMCがSBIとの提携解消について理由を述べている。また、QualcommとArmとの係争が激化している。

[→続きを読む]

2024年10月11日

|産業分析

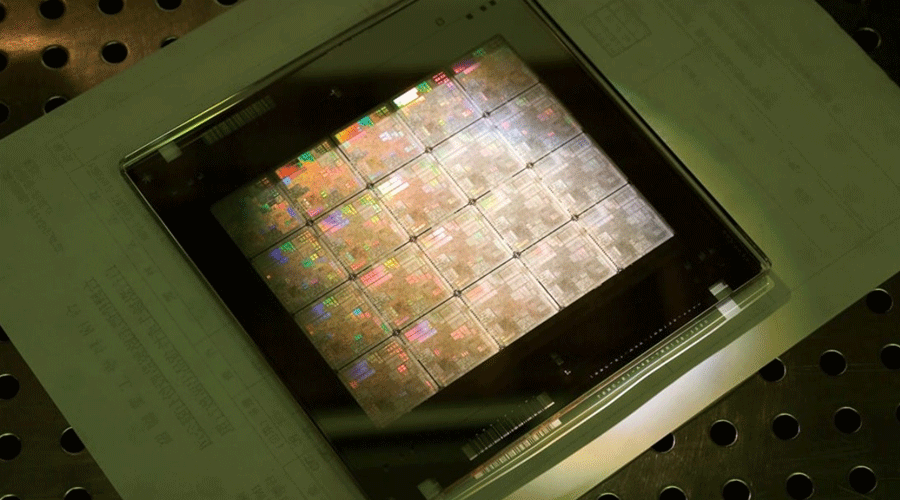

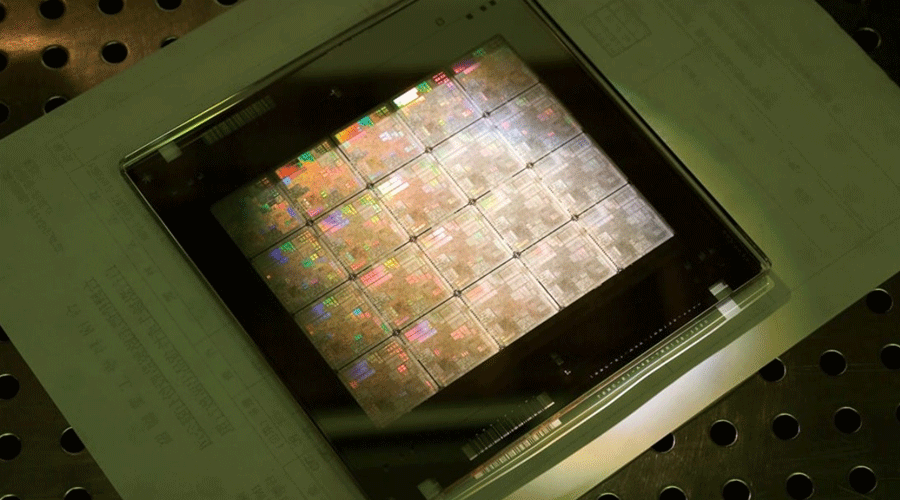

メーカーとサプライヤとの関係がひっくり返る事例がNvidiaとTSMCとの間に見られる。これまではファブレス半導体としてのNvidiaが設計したチップをTSMCが製造するという関係だった。今度はTSMCがメーカーとなり、プロセス中によく使うリソグラフィ工程でより正確なマスクを作製するための計算に、サプライヤであるNvidiaのGPUを利用するのだ。

[→続きを読む]

2024年10月10日

|会議報告(プレビュー)

IEDM(International Electron Devices Meeting)2024の内容が明らかになった。70周年を迎える今年は、「明日の半導体技術を形作る」という全体テーマで、基調講演、一般講演だけではなく、フォーカスセッションやチュートリアル、ショートコースなど270件の講演が予定されている。例年通り米サンフランシスコのヒルトンホテルで12月7日から開催される(図1)。

[→続きを読む]

2024年10月 9日

|技術分析(製造・検査装置)

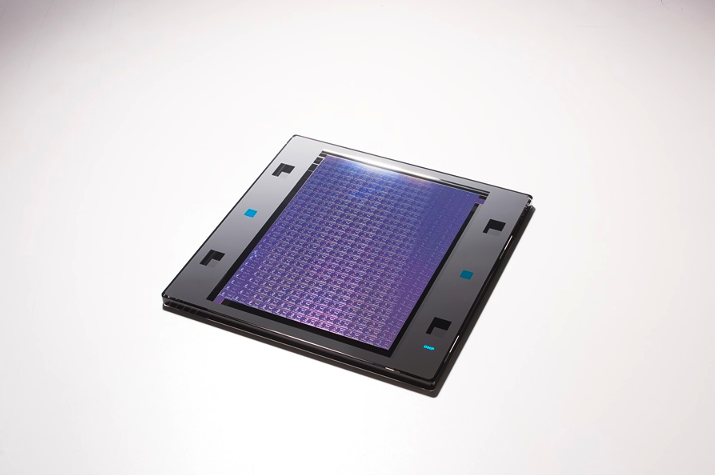

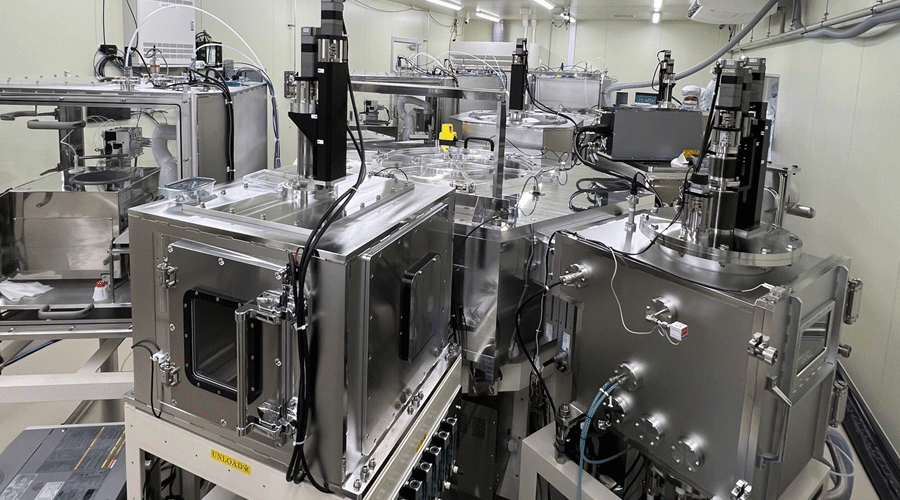

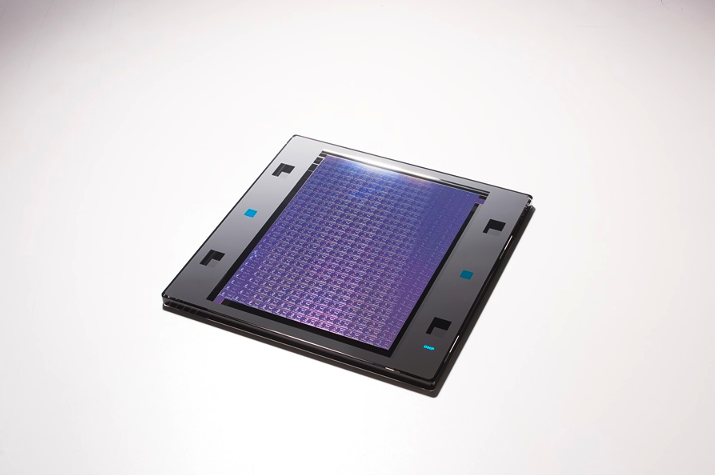

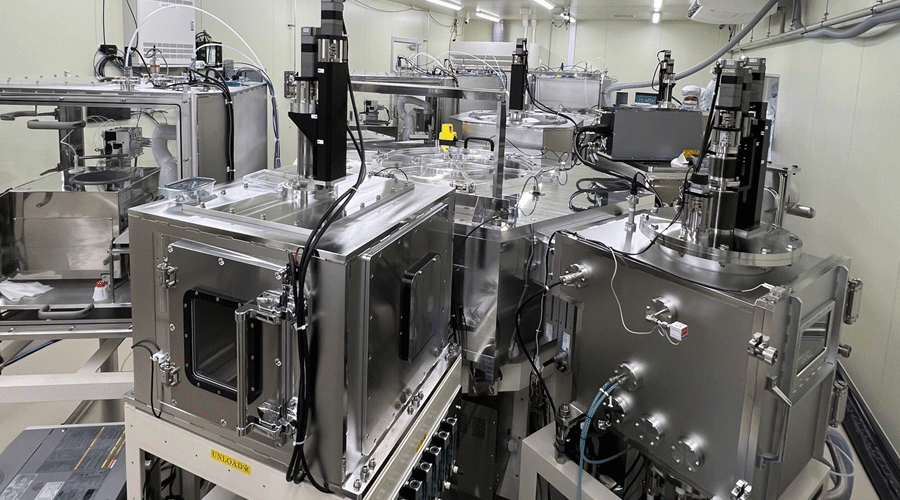

産業技術総合研究所は、ペロブスカイト構造の太陽電池の実用化に向け、自動作製システムを試作した。ペロブスカイト太陽電池は、変換効率がシリコン以上の高い効率を示す試作は多いが、バラつきが大きいと共に、経時変化が大きく劣化しやすい、大面積が難しいなどの問題が山積み。少しでも手作業による作製ではなく自動機によってバラツキを減らす狙いで装置を開発した(図1)。

[→続きを読む]

2024年6月13日

|産業分析

リソグラフィ最大手ASMLはIntelのオレゴン工場にHigh-NA(Numerical Aperture:開口数)のEUV装置を初出荷したが、海外複数のメディアによると、早くも次のHyper-NAのEUV装置開発が始まりそうだ。従来のEUV装置のNAは0.33でHigh-NA装置は0.55、そしてこれから開発するHyper-NAは0.75となり、これまで以上に微細加工が可能になる。

[→続きを読む]

2024年5月14日

|会議報告(レビュー)

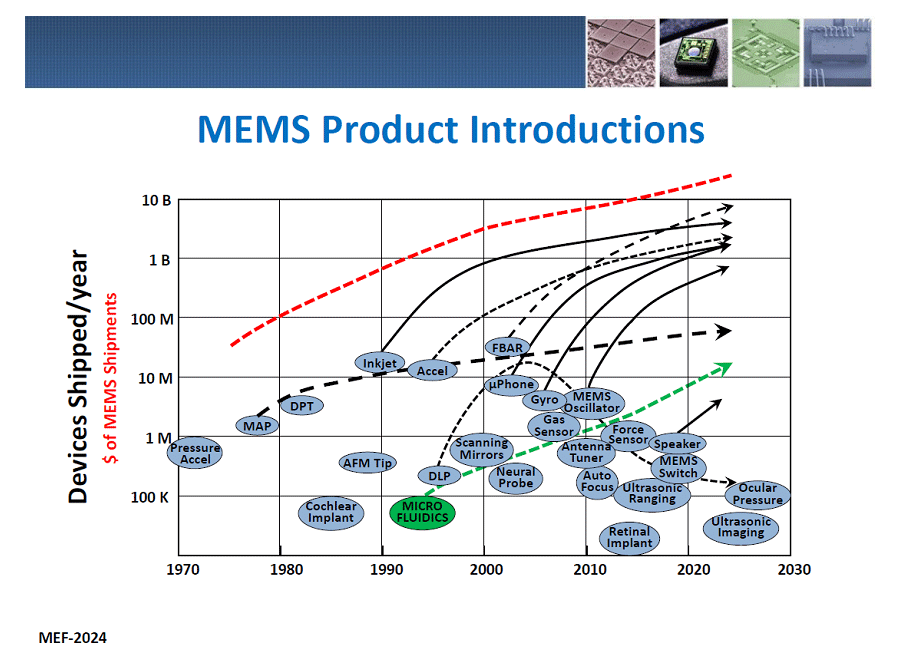

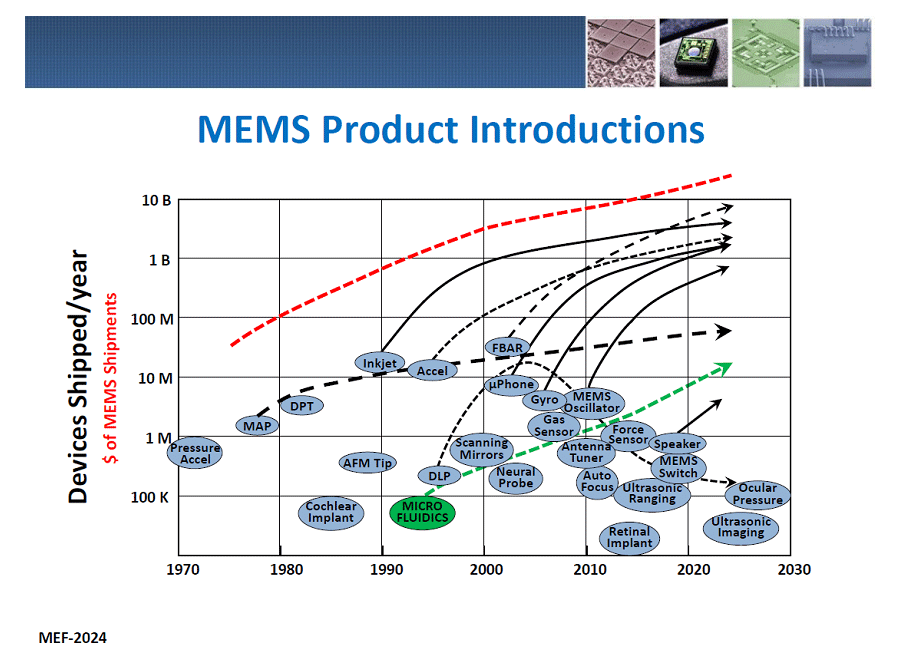

MEMS(Micro Electro-Mechanical Systems)の国際会議「The 15th MEMS Engineer Forum」が先月、東京で開催された。MEMSデバイスは、加速度センサ・圧力センサからマイクロフォン、RFフィルタ、超音波トランスデューサなどさまざまな応用に使われてきた。欧州勢は、自動車市場やスマホ市場などでMEMSデバイスを発展させた。次のMEMSデバイスは何か。

[→続きを読む]

2024年4月30日

|週間ニュース分析

TSMCは2024Technology Symposiumをカリフォルニア州サンタクララで開催、2nmの次の1.6nmに相当する技術を発表した。先週、2024年第1四半期(1Q)における各社の決算が発表された。Intel、SK hynix、ルネサスエレクトロニクス、ソシオネクストなどが決算を発表。生成AI向けの学習ソフトを軽くするという動きもあり、AIプロセッサを集積するSoCへの期待が膨らむ。

[→続きを読む]

2024年4月26日

|会議報告(プレビュー)

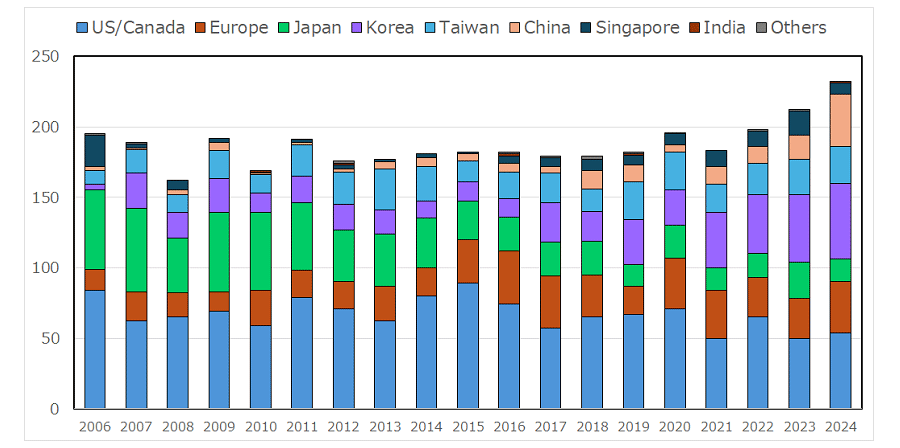

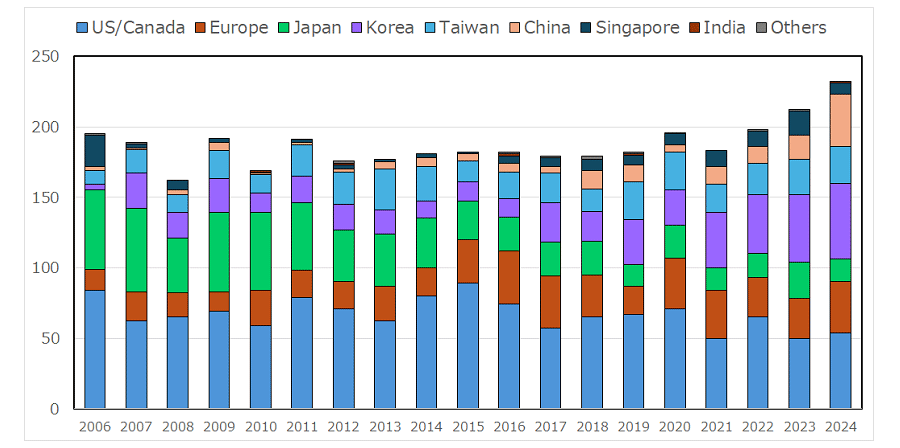

VLSI Symposium(正式名称:2024 Symposium on VLSI Technology and Circuits)2024の概要が決まった。今回の特長は、投稿論文数、採用論文数ともここ10年で最も多いことだ。特に韓国からの採用論文が最も多く、Technology、Circuitsを合わせた全採用論文232件の内、54件と北米と同数になった(図1)。次に多いのが中国(37件)、そして欧州(36件)、台湾(26件)、日本(18件)、シンガポール(8件)、インド(1件)となった。

[→続きを読む]

2024年3月18日

|週間ニュース分析

前工程でも後工程でもない「中工程」と言われる先端パッケージング技術を、つくばにあるTSMCジャパン3DICセンターが徐々に明らかにしている。またToppanがサブストレート基板の工場をシンガポールに新設する。2.5D/3D-ICなどの先端パッケージはクルマでも採用されそうだ。ASRA(自動車用先端SoC技術研究組合)の狙いはチップレット。

[→続きを読む]