2025年7月 2日

|技術分析(半導体応用)

STMicroelectronicsは、ToF(Time of Flight)センサとAIで、人の近づきや遠ざかりを検出したり、複数人を検出したりすることで、パソコンのセキュリティを高めるといった新しい応用に力を入れている。PCから離れるとすぐにパソコン画面を消去、消費電力を削減する。人が戻ってくると起動し始める。複数人が覗いていると、画面をぼやけさせ警告する。頭の向きを検出して画面を見ていなければ画面を暗くし、消費電力を下げる。

[→続きを読む]

2025年6月 5日

|技術分析(半導体応用)

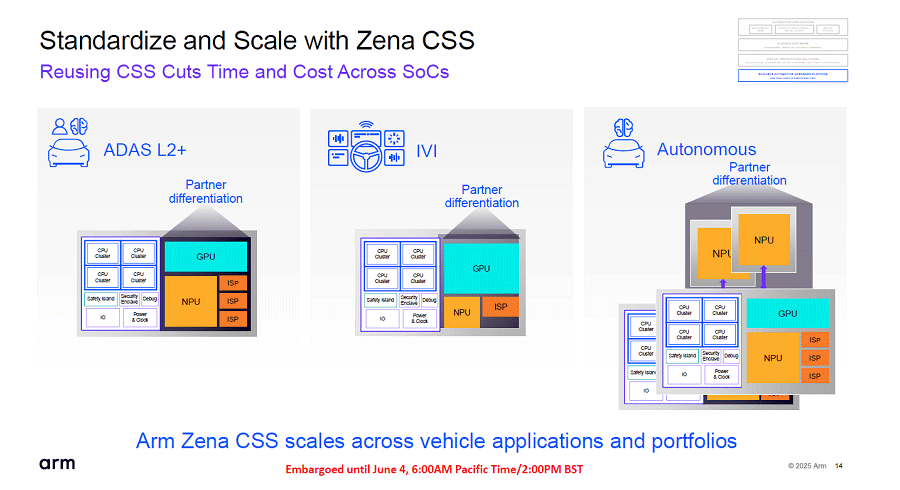

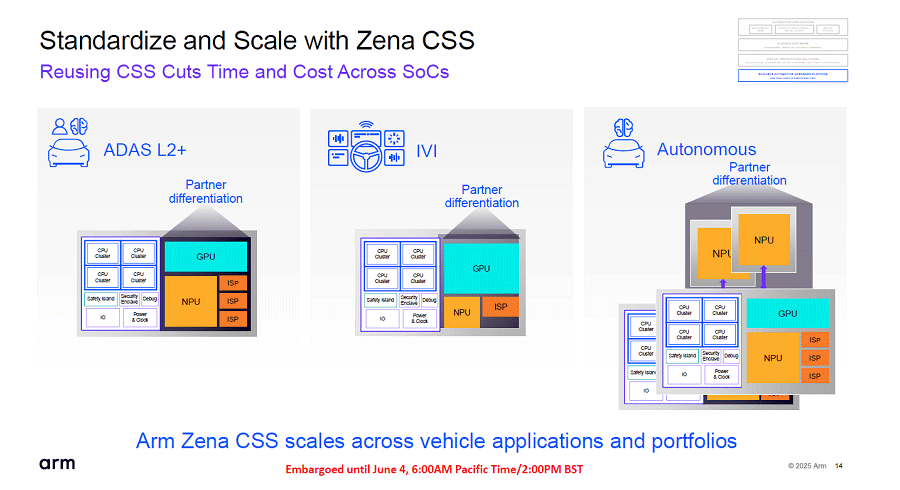

Armがますます高集積のIPを開発している中、16個のCPUコアにセキュリティIPや安全性IP、I/O(入出力)などを基本の標準品とする新しいCSS(Compute Sub-System)IPコア「Zena」(ジーナと発音)を発表した。ここにGPUやNPU(ニューラルプロセッシングユニット)などを拡張するバージョンも提供する。スケーラブルなCSSコアとなる。

[→続きを読む]

2025年5月28日

|技術分析(半導体応用)

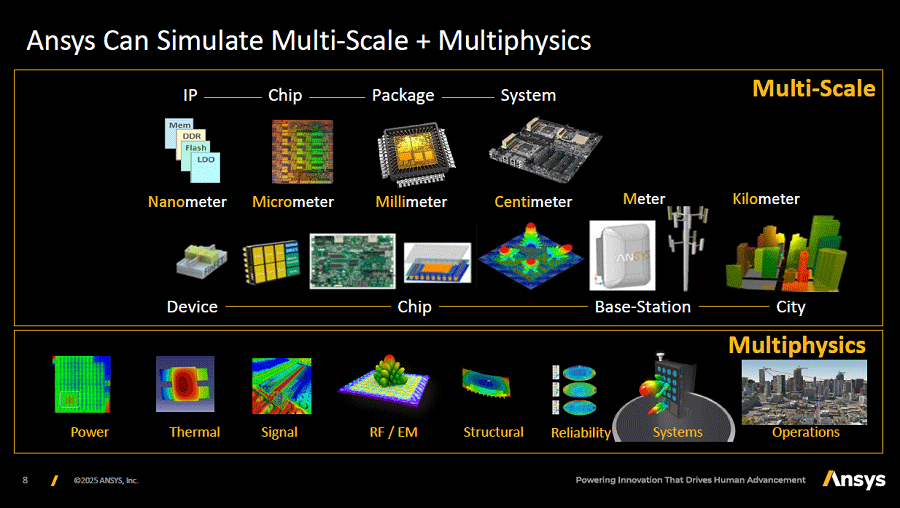

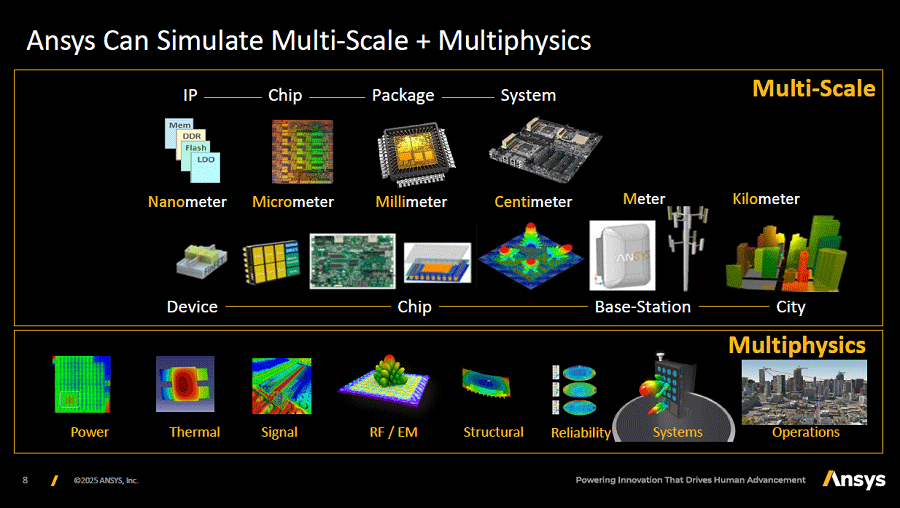

クルマが今後、SD-V(ソフトウエア定義のクルマ)になるにつれ、ますます半導体の出番が増えてくる。SD-Vでは頭脳となるSoCと、センサとなるイメージセンサやレーダー、LiDARなどのセンサが増えてくると共に、システム上のセキュリティやセンサフュージョンなど新しい半導体はますますシステムに近づく。シミュレーションメーカーのAnsysは、半導体の世界にもシミュレーションが不可欠になることを訴求している。

[→続きを読む]

2025年4月24日

|技術分析(半導体製品)

Infineon TechnologiesがこれからのSD-V(ソフトウエア定義のクルマ)時代を迎え、CPUコアとしてRISC-Vを採用することを明らかにした(図1)。RISC-Vコアは米カリフォルニア大学バークレイ校の教授らが開発した、オープンソースのCPUコアであり、誰でも利用できる。とはいえ、非常にシンプルな命令セットなので自分で開発する場合には必要な命令セットやパイプライン構造、マルチコア対応などを作り込む必要がある。なぜInfineonはRISC-Vに力を入れるのか。

[→続きを読む]

2025年4月23日

|技術分析(製造・検査装置)

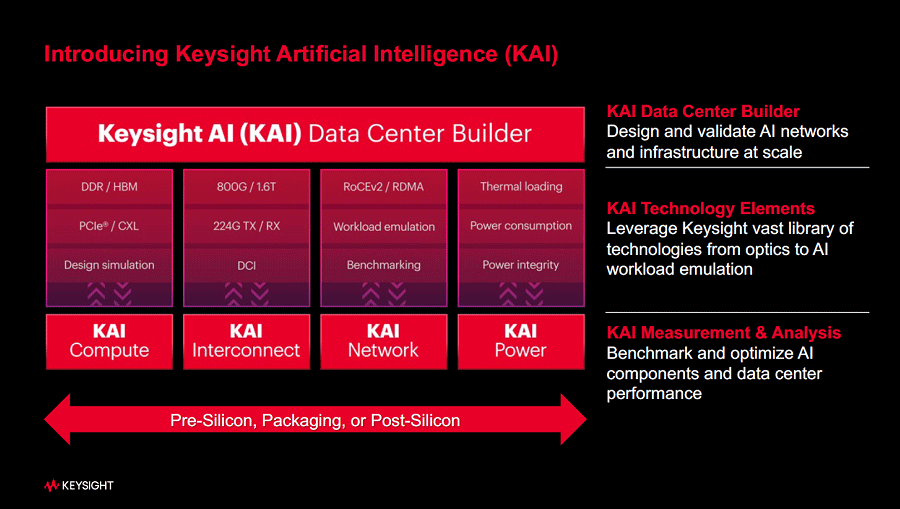

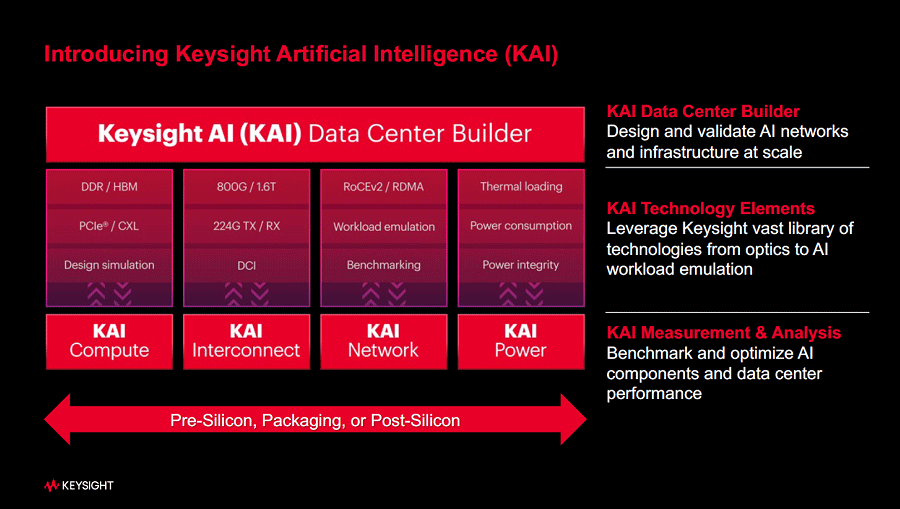

測定器メーカー大手のKeysight Technologyは、成長し続けるAIデータセンター向けの測定技術KAI(Keysight Artificial Intelligence)アーキテクチャを提唱(図1)、具体的な製品群も発表した。このアーキテクチャは、超並列に演算するGPU(グラフィックスプロセッサ)などのワークロードをエミュレーションによって検証するもので、AIデータセンターをさらに拡張する場合に支援できる。

[→続きを読む]

2025年4月 9日

|技術分析(半導体製品)

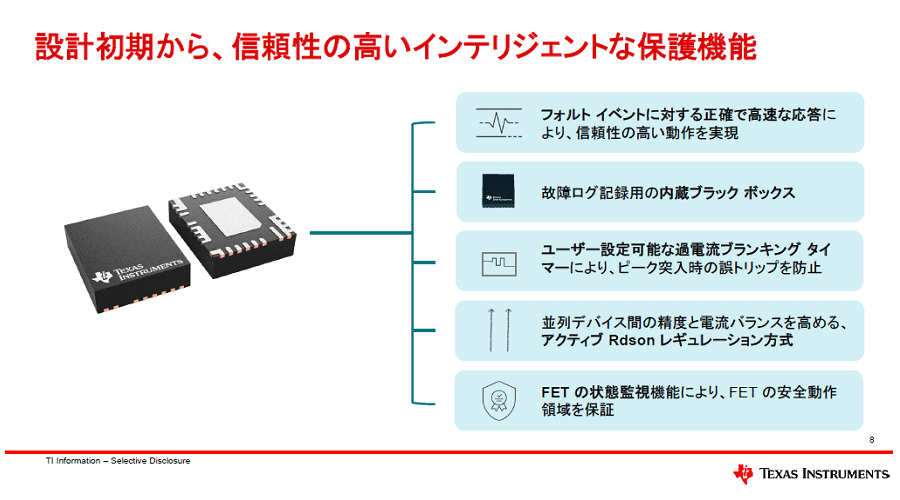

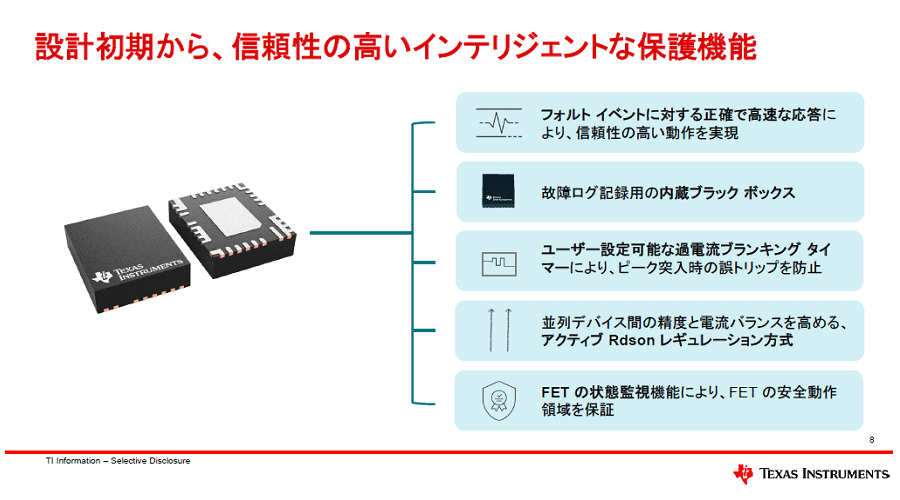

Texas Instrumentsは、並列接続により最大6kWまでの電力を扱うことのできる電子フューズ(eFuse)IC、「TPS1685」を開発した。これによりますます電力を消費するデータセンターの電源を確保できるようになる。一般のeFuseをただ単に並列にしても、MOSFETのオン抵抗や配線パターンの抵抗やコンパレータのしきい電圧のバラつきなどによって、弱い部分に電流集中が起こりやすくなる。しかしこれを防いだ。

[→続きを読む]

2025年3月27日

|技術分析(半導体応用)

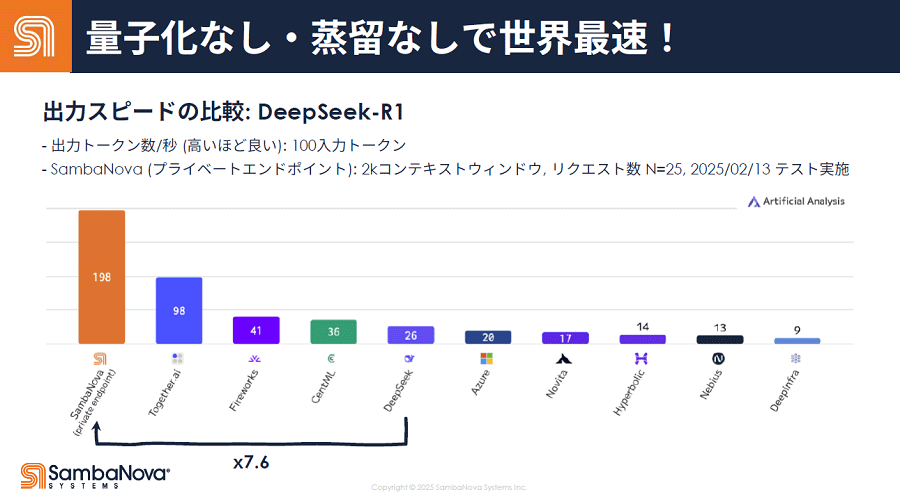

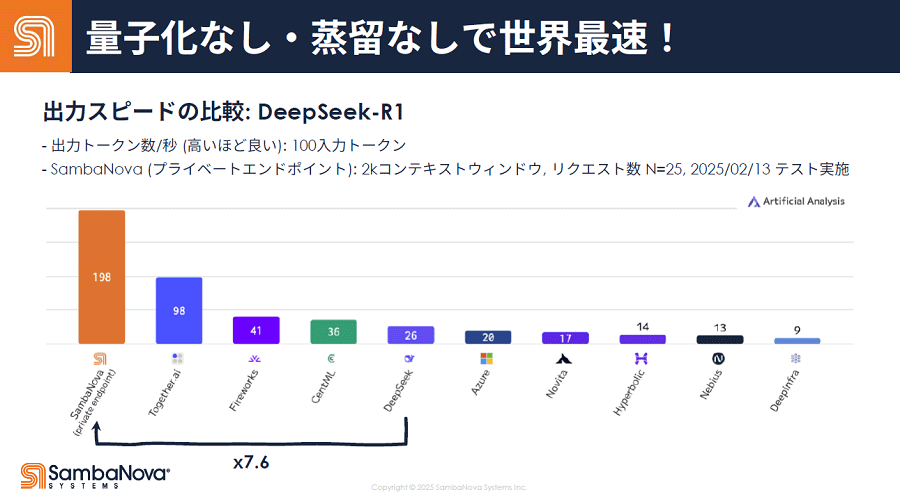

高効率で消費電力当たりのAI処理性能が高いAIチップの中で、NvidiaのGPUと張り合えるチップはそう多くない。データフローコンピューティングアキテクチャであり、さらにダイナミックにエージェントがジョブを切り替えられる方式のSambaNovaのチップはその候補の一つ。推論性能で他社を圧倒する結果をこのほど発表している。

[→続きを読む]

2025年3月18日

|技術分析(半導体製品)

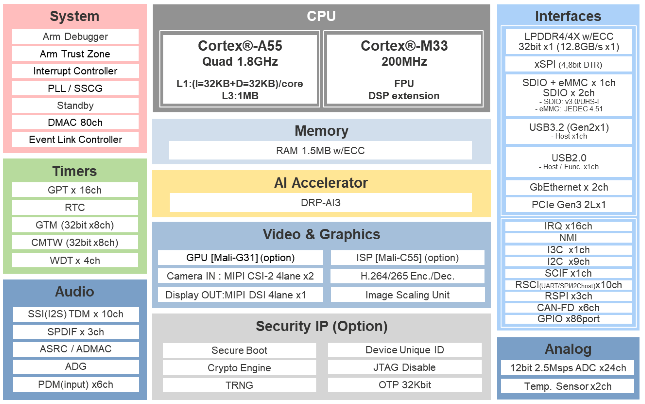

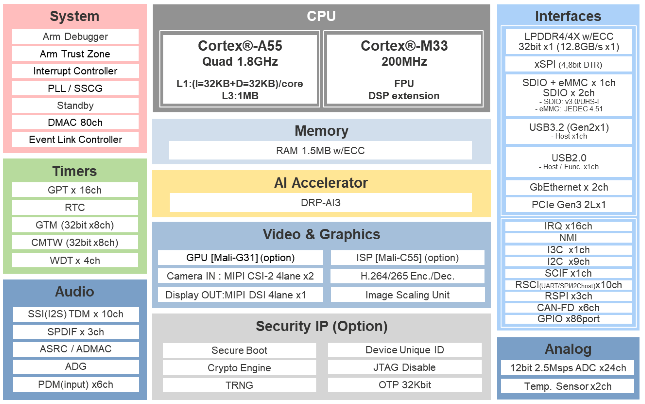

ルネサスエレクトロニクスは、手ごろな価格で画像認識AIが使える新しいAIアクセラレータを集積したミッドレンジのプロセッサ「RZ/V2N」をドイツのニュルンベルグでのEmbedded World 2025で展示した。2台のカメラ画像を取り込める上に、クルマのドライブレコーダーや自動走行ロボットのカメラ、監視カメラなどコンピュータビジョンに対応する。3月19日に発売する。

[→続きを読む]

2025年3月 4日

|技術分析(半導体製品)

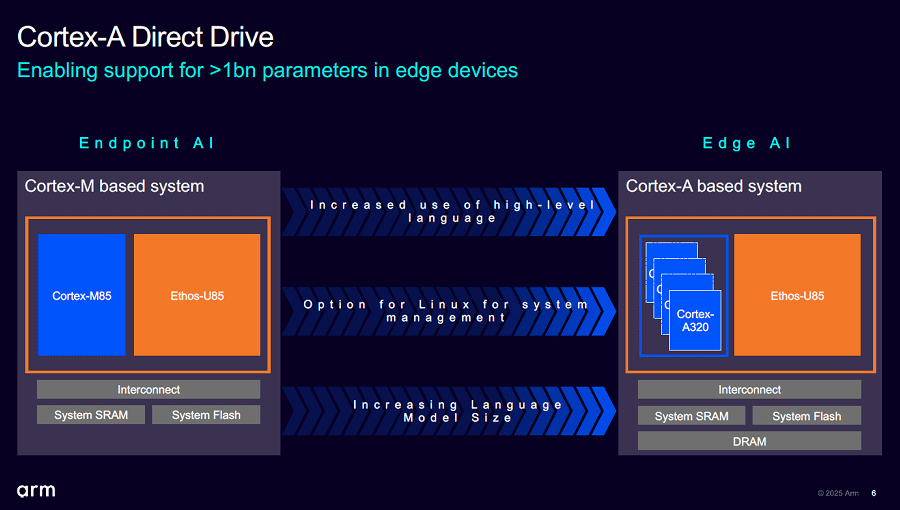

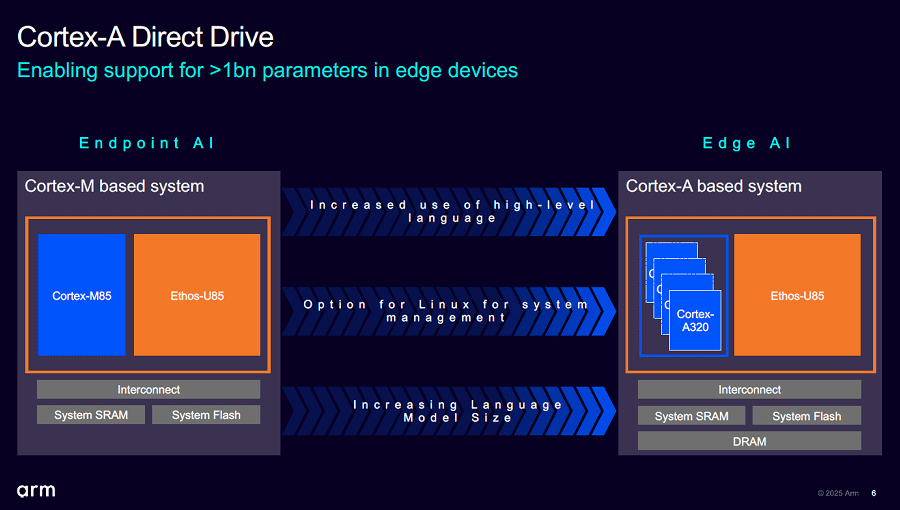

高性能なCPUとAI専用のNPU(ニューラルプロセッシングユニット)を集積したIP(知的財産)コアをArmが開発した。高性能ビデオ伝送をはじめとする高速IoT(Internet of Things)に対応するIPコアである。高性能な技術であるArmv9をエッジAIのプラットフォームとして使う用途が早くも生まれたために、このような高性能IoT向けのIPを開発した。具体的にはどのような用途だろうか。

[→続きを読む]

2025年2月28日

|技術分析(プロセス)

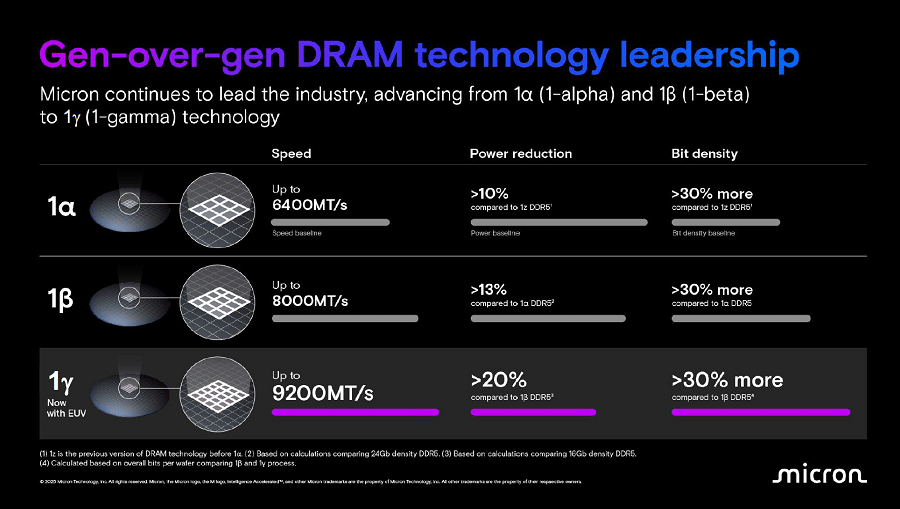

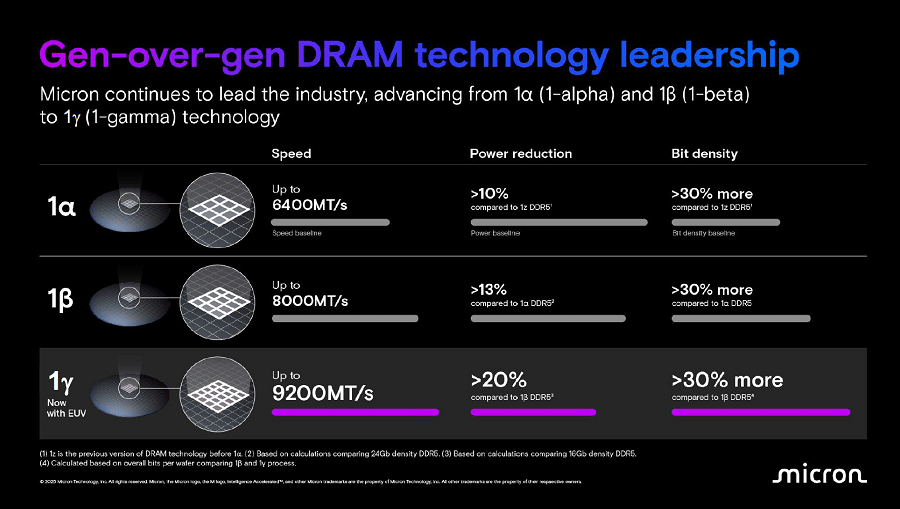

Micron Technologyが1γnmノードのDDR5DRAMをサンプル出荷した。1γnmというサイズは10nmクラスのようで、EUV装置の導入が必須になる。Micronの微細な技術によって、スピードは現世代の1βnmノードのDRAMと比べ、8Gbpsから9.2Gbpsと高速になり、消費電力は20%削減され、集積度は30%上げることができる(図1)。

[→続きを読む]