Micronが1γnmノードのDRAMをサンプル出荷、その実力は?

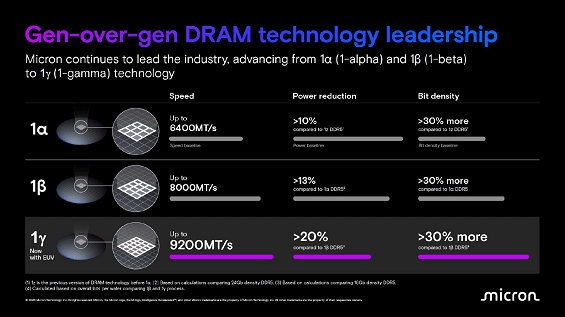

Micron Technologyが1γnmノードのDDR5DRAMをサンプル出荷した。1γnmというサイズは10nmクラスのようで、EUV装置の導入が必須になる。Micronの微細な技術によって、スピードは現世代の1βnmノードのDRAMと比べ、8Gbpsから9.2Gbpsと高速になり、消費電力は20%削減され、集積度は30%上げることができる(図1)。

図1 1γDRAMの性能、消費電力 出典:Micron Technology

DRAMビジネスは、ロジックと違い、20nm以下になると正直ベースで19〜18nmを1xnm、17〜16nmを1ynm、15〜14nmを1znmなどと刻んできて、さらに1αnm、1βnm、1γnmへと少しずつ刻んで微細化してきた。ロジックは28nm、20nmまではプレーナで正直ベースだが、16/14nmでFinFETを使いだしたことで、3次元化させ、微細化寸法から離れていった。7nmと言っても最小の実寸法は16〜14nm程度だった。

ロジックでは、配線やトランジスタの3次元化を進めることで、実際のトランジスタの集積度で何nmという寸法で表現した。例えば7nmは1mm2あたり1億個前後のトランジスタが集積されたICを表現していた。中国製のICチップで7nmプロセスノードを実現した、という発表があったときも1mm2あたりトランジスタ数が9400万個程度あったため、7nmプロセスと認定した。

今回DRAMで1γnmプロセスは10nm程度の最小配線幅になった模様で、そのように表現していたが、さらなる微細化を1δ/εnm(デルタ/イプシロン)と表現しているため、そこまで微細化しても、まだ10nmを切っていないのかもしれない。

ただし、配線幅がここまで微細になると、リソグラフィ装置がArF液浸のレーザーリソグラフィからEUV(極端紫外線)に代わってくる。Micronは競合メーカーと比べてEUV導入には慎重だった。「これまでの技術を徹底的に使い倒すことでコストを下げ、利益を生む方向に進んできた」と日本法人のマイクロンメモリジャパンでDRAM Technology Development部門のシニアVPの白竹茂氏は語る。EUVの導入が遅くてもコストを優先して従来技術を使い倒すという考え方であり、最新の4Q決算ではSamsungよりも利益率は高い。

図2 マイクロンメモリジャパンでDRAM Technology Development部門のシニアVPの白竹茂氏

今回の1γDRAMのDDR5メモリのサンプルは広島工場で開発したものだが、EUVリソを使わなくてはならない部分の加工のみを、EUVが導入されている台湾の工場にウェーハを送り、加工処理後に広島に戻して次の作業に入ったという。1γnmDRAMと言っても全ての工程にEUVを使ったわけではない。最も微細でしかも実験的にも使いやすいのはおそらくコンタクト部分の加工ではないか、と想像される。

まだ広島工場にEUVは入っていないが、広島工場の投資には日本版CHIPs法案による補助金があるため、25年度中に入ることは間違いない。白竹氏も25年中には入るだろうと答えている。台湾では台北と台中に工場があり、台中の工場にEUVが導入されている。

今後、DRAMは3D-DRAMへと進む道筋がある。これは、NANDフラッシュのようにモノリシックに積んでいくわけだが、これまで縦方向に円筒状のキャパシタ部分を横方向に倒し、トランジスタとキャパシタを縦方向に積んでいく構造である。Applied Materials社のホームページ(参考資料1)にその構造が掲載されている。Micronは3D-DRAMに対しても従来技術を使い倒していくことになる。ただしその研究開発は怠らない。

参考資料

1. “DRAM”、Applied Materialsホームページ内