高集積なSoCの設計を巨大IPで支援する、Armがクルマ用CSS Zenaを発表

Armがますます高集積のIPを開発している中、16個のCPUコアにセキュリティIPや安全性IP、I/O(入出力)などを基本の標準品とする新しいCSS(Compute Sub-System)IPコア「Zena」(ジーナと発音)を発表した。ここにGPUやNPU(ニューラルプロセッシングユニット)などを拡張するバージョンも提供する。スケーラブルなCSSコアとなる。

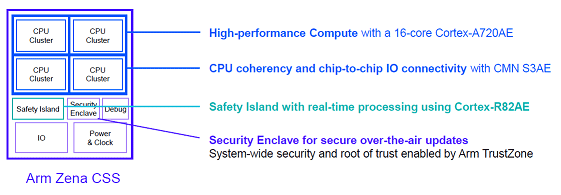

図1 SD-V時代のArmの巨大IP「Zena」 出典:Arm

Zenaは、16コアのCPU「Cortex-A720AE」をコンピュートコアとし(図1)、さらにそれらのCPUコアやアクセラレータなど間とのデータ転送をスムーズに行うためのコヒーレントなメッシュネットワークで接続する回路「CMN S3AE」も含めている。さらにリアルタイム制御する安全性回路「Safety Island」や、OTA(Over the air)によってソフトウエア更新する場合のセキュアなデータを提供する「Security Enclave(飛び地の意味)」なども集積した巨大なIPである。

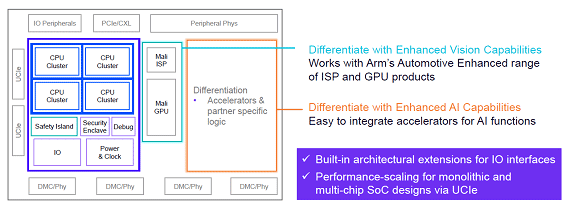

この基本的なIPは拡張性があり、基本IPをさらにいくつかを集積するSoCを設計したり、あるいは基本IPにAI用のNPU(Nural Processing Unit)やGPUなども追加・集積したりすることも図2のようにできる。

図2 Arm ZenaはNPUやGPUを拡張することも可能 出典:Arm

これらのコアをスケーラブルに拡張可能にするために、Coherent Mesh Network (CMN)と呼ぶネットワーク制御回路は非常に重要であり、コアの数を増やしたり、チップ間のデータ転送をスムーズに行ったりするための回路である。「S3AE」のAEは自動車向けという意味を含んでいる。

Arm CSS (Compute Sus-Systems) は、データセンター用のHPC(High Performance Computing)を出発点として、自動車向けにもZena CSSを開発したが、ここまで大規模なIP回路を開発したのはなぜか。SoCが複雑になり、それを使うユーザーは半導体企業だけではない。システムベンダーや、データセンターなどのHPCユーザーも多い。SoC設計に手慣れた大手ユーザーと話をしても集積度が上がり、回路が複雑になるにつれ設計は難しくなってきているとArmは同意する。ましてや、中小の半導体メーカーやシステム設計企業にはもはや複雑なSoCの設計は極めて難しいという。

Arm CSSの全てのCPUやマルチコアなどはすでにシリコンで実証された回路ばかりで、それらをつないだマルチコアでもすでにシリコンで実証されている。このため、ユーザーはすぐ使えるため、もっと集積度の高く、スケーラブルでキャッシュコヒーレントな巨大IPを求める声は強まっているという。マルチコアにする場合でさえ、大手半導体以外は難しいとの声がある。ある半導体メーカーはCPUコアのIPにNPUを拡張することは大変な作業を要するためCSSの製品IPは大変良いと言われたという。

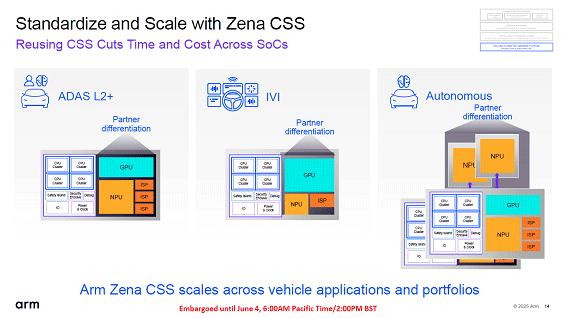

図3 Arm Zenaの拡張性を利用する応用事例 出典:Arm

回路のスケーラビリティは、使う用途によって決まる。例えば、ASDAS(先進ドライバ支援システム)やIVI(車内インフォテインメント)コックピット用途などは基本IPのNPUなどの回路を追加したIPになるが、クルマ用の中央コンピュータとなれば、複数のIPになる(図3)。

一つのIPに集積する回路がどれほど複雑になりIPが巨大化しようとも、Armのビジネスモデルは、従来と変わらずIPライセンスとロイヤルティのビジネスであり、RTL(register transfer level)レベルで提供する。決してファブレス半導体にはならないとArm Automotive事業部門GTM・アライアンス担当VPのBruno Putman氏は述べている。