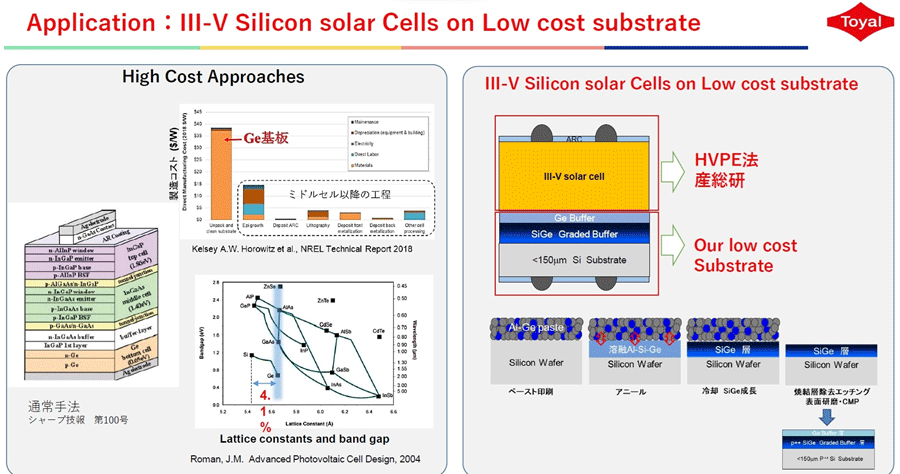

低コストのGe-on-Si半導体基板技術を東洋アルミが開発、GaAs半導体を安価に

Si基板上にGe層を短時間で安価に作製する方法を東洋アルミニウムが開発した。Ge層の厚さを自由に変えられるだけではなく、ストイキオメトリ(化学組成)も制御できる。今のところ高価なGaAs系半導体向けの基板としての道を提案している。安価な太陽電池やSiフォトニクス、スピントロニクスなどの基板材料への応用を狙っている。 [→続きを読む]

» セミコンポータルによる分析 » 技術分析

Si基板上にGe層を短時間で安価に作製する方法を東洋アルミニウムが開発した。Ge層の厚さを自由に変えられるだけではなく、ストイキオメトリ(化学組成)も制御できる。今のところ高価なGaAs系半導体向けの基板としての道を提案している。安価な太陽電池やSiフォトニクス、スピントロニクスなどの基板材料への応用を狙っている。 [→続きを読む]

半導体チップからコンピュータラック、基盤モデルまでフルスタックでAIを提供するスタートアップ、SambaNova(サンバノバ)が日本オフィスを開設、そのチップアーキテクチャにデータフローコンピューティングを採用していることがわかった。AIの基本的なモデルであるニューラルネットワークもデータフロー方式であるため、AIとは相性が良い。古くて新しいデータフローコンピュータ時代がやってくるかもしれない。 [→続きを読む]

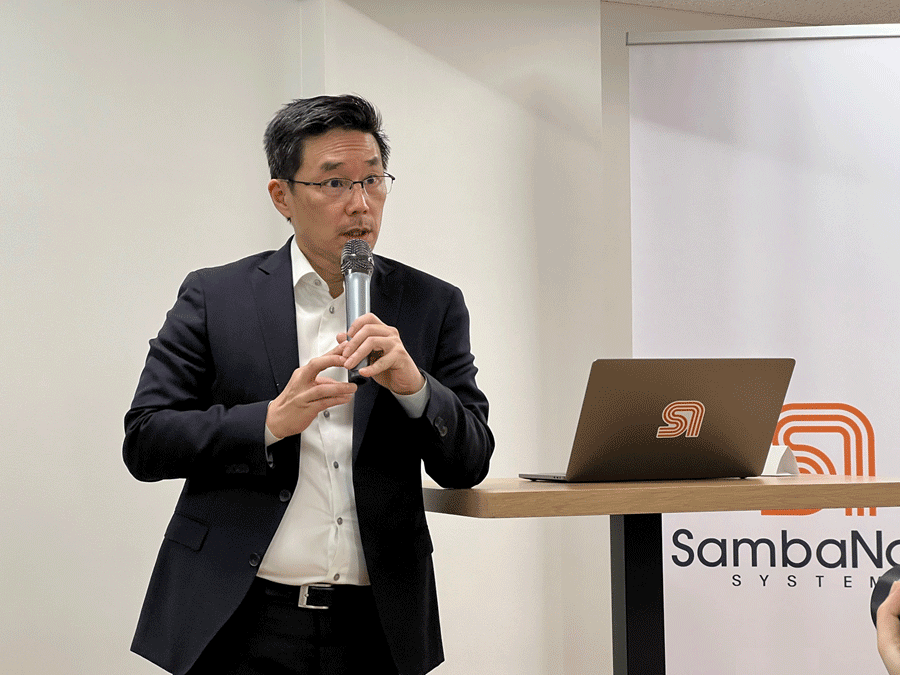

HDD(ハードディスク装置)の記録密度向上は、一段違うレベルに達した。Seagate Technologyが開発したHAMR(熱補助方磁気記録:ハマーと発音)は、実際の製品に適用されたもので、これまでは提案止まりだった。今回の新技術は、ディスク側の超格子構造と、読み取り/書き込み側の量子アンテナ、という謎めいた言葉がキーワードだ。 [→続きを読む]

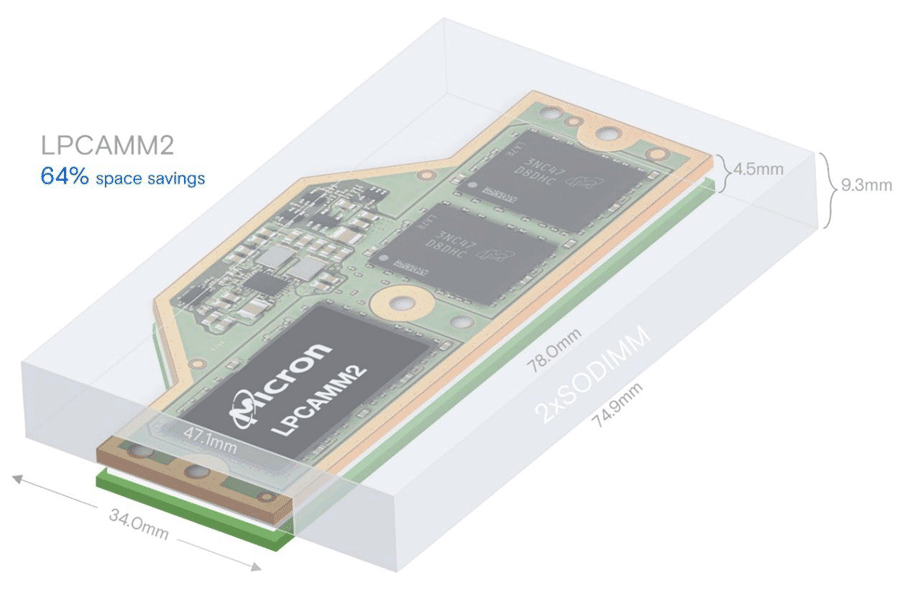

いよいよメモリモジュールで性能や消費電力が律速される時代がやってきた。長い間、標準となってきた、ソケットに挿し込むタイプのDIMM(Dual Inline Memory Module)やSO(Small Outline)DIMMの交替時期に差し掛かる。これからのAIパソコンやさらなる高性能・低消費電力が要求されるコンピュータ向けに押さえつける接続方式のCAMM(Compression Attached Memory Module)をMicronがサンプル出荷した。 [→続きを読む]

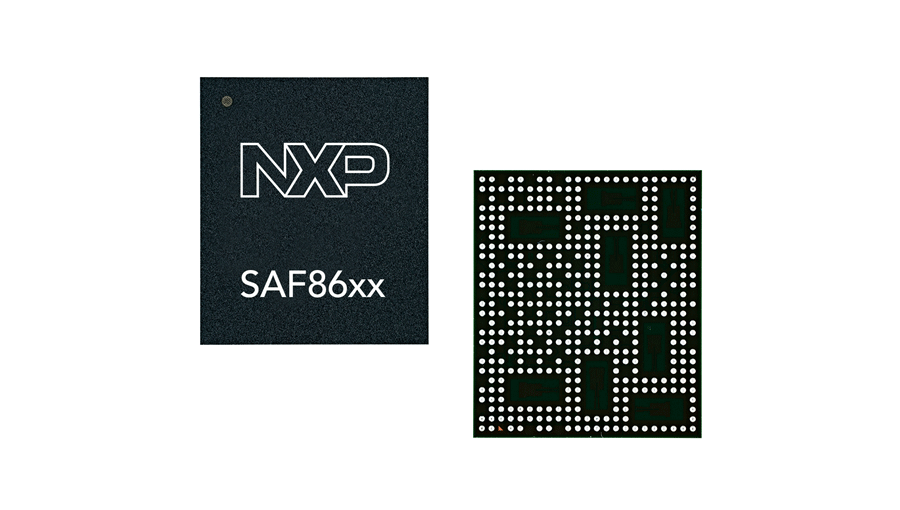

クルマの機能をソフトウエアで拡張するSD-V(ソフトウエア定義のクルマ)が今後のカーコンピューティングの主流になると見込まれているが、NXP Semiconductorはこのほどレーダーセンシング技術をSD-Vに一歩近づけるSoC「SAF86xx」シリーズ(図1)を開発した。この技術はソフトウエアの更新によりレーダーセンシング機能を拡張するという技術で未来の方向を示している。 [→続きを読む]

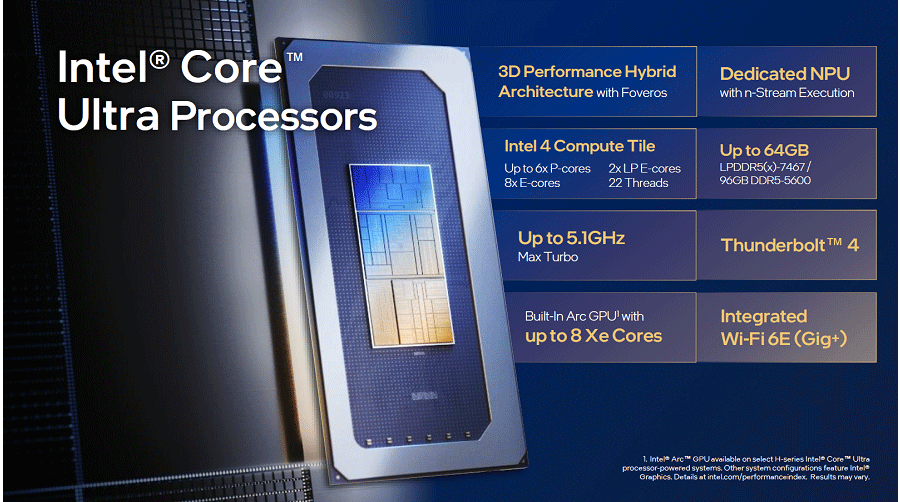

Intelは、AI Everywhere戦略を採ることを宣言した。その代表的な例としてAIエンジンを集積したパソコン向けCPU「Core Ultra(コード名Meteor Lake)」(図1)を発売するとともに、サーバー向けのCPU「第5世代のXeonプロセッサ」にもAIエンジンを集積した。さらにAI専用チップ「Gaudi 3」を2024年に発売することも明らかにした。 [→続きを読む]

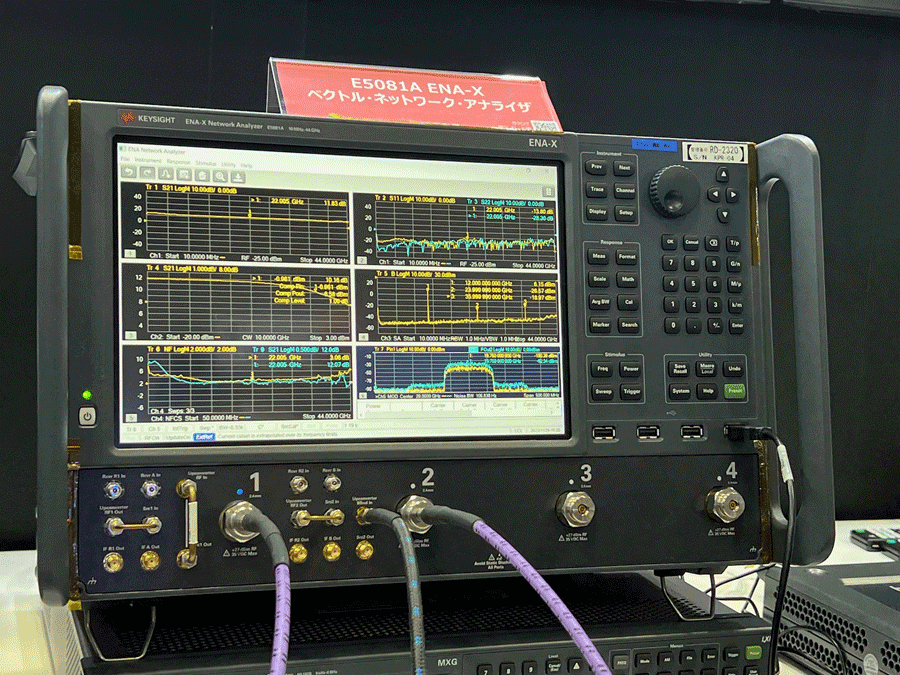

5Gやミリ波などRFチップの高周波特性の測定では時間がかかることが多い。Keysight Technologyが先週、マイクロ波関係の展示会MWE2023で見せたENA-Xベクトルネットワークアナライザ(VNA)は、最大44GHzまでのsパラメータと変調歪解析、NF測定を1度の接続で全て測れる便利な測定器だ。日本初の公開である。 [→続きを読む]

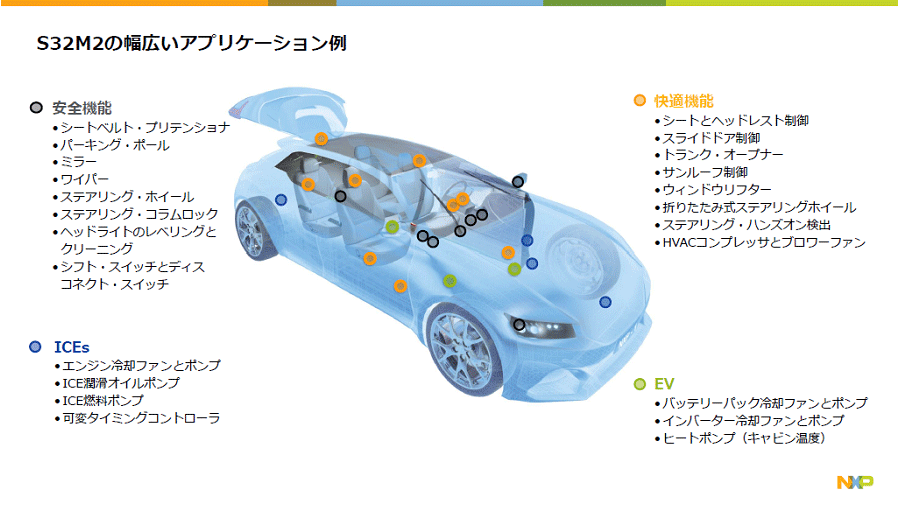

パワートランジスタは、ゲートをドライブするためのドライバICやドライバICに指令を送るための制御用マイコンまでを一つのソリューションとして使われている。1パッケージにドライバICとマイコンなどを収容したモータ制御IC「S32M2」をNXP Semiconductorが製品化した。最終段のパワートランジスタに直結して使える。 [→続きを読む]

これからの半導体産業はどうなるか。生成AI登場で膨大なコンピュート能力が求められる一方で、製造だけではなく設計も複雑になりコストが増大する。求められるカーボンフリーの持続可能社会を実現できる技術には半導体しかない。しかし、余りにも複雑になりすぎる半導体チップをどう作るか。ベルギーの半導体研究所imecはこの大きな課題を解決する取り組みを始めた。 [→続きを読む]

ルネサスエレクトロニクスは、クルマ向けのマイコン(MCU)とSoCの総称である「R-Car」シリーズのこれからの第5世代のR-Carシリーズを発表した。MCUからSoCまでCPUコアは全てArm系のIPを活用、ハイエンドのSoCでは5nm,4nmなどの先端プロセスノードや、チップレットを駆使する先端パッケージを採用していく。 [→続きを読む]