Micron、24GビットのDRAMダイをTSVで8枚スタックした24GB HBM3を出荷

Micron Technologyがメモリ容量24GB(ギガバイト)で、転送レート(バンド幅)1.2TB/sという巨大なHBM(High Bandwidth Memory)メモリを開発、サンプル出荷を開始した。このHBM3 Gen2を開発した理由は、生成AIの学習に向け、学習時間の短縮を狙ったためだ、と同社コンピュート&ネットワーキング事業部門 VP 兼 ゼネラル・マネージャーのPraveen Vaidyanathan氏は言う。

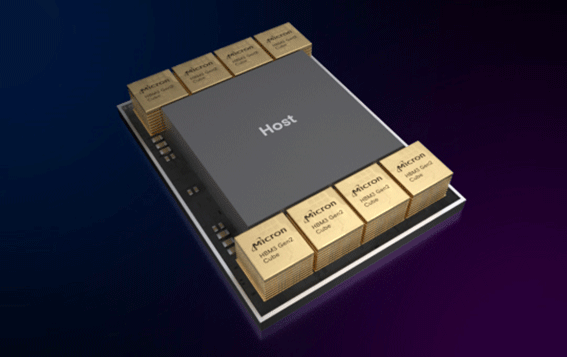

図1 開発したHBM3 Gen2メモリはプロセッサとセットで使うことが多い 出典:Micron Technology

同氏によると、大規模言語モデル(LLM)の学習に、巨大な容量で高速の転送レートを持つこのメモリを使えば、学習時間を30%短縮できるため、これまで3カ月かかっていた学習が2カ月で済むようになる。生成AIに必要なLLMは、何千億という巨大なパラメータを使うため、それに合わせたプロセッサだけではなく、メモリもそれ相応の製品が求められる。つまり、巨大なニューラルネットワークの演算データを処理するプロセッサと巨大なメモリは、一緒に基板に構成されるようになる(図1)。

Micronは、生成AIによってHBMの需要はますます高まり、2022年から2025年までの間に年平均成長率CAGR50%以上で成長すると予測する。サーバーなどのコンピュータはこれまでの汎用ではなくAIに注力したコンピュータとなり、メモリおよびストレージ容量は大きく成長するだろうと見ている。

開発した24GBの大容量は、現在量産中のHBMの容量よりも50%大きく、1.2TB/sの転送レートも同様に現在量産中のHBMよりも50%速い。また、消費電力当たりの性能は現在同社のHBM2eと比べて2.5倍以上だとしている。

図2 HBMメモリの外形は内部で8枚スタックしても一般のメモリ製品とそう変わらない 出典:Micron Technology

メモリ容量を増やすため、1β nmプロセス(参考資料1)で製造した24GビットのDRAMダイを8個スタックし、制御用のロジック1個をスタックして構成した。ダイ同士を接続するためにTSV (Through Silicon Via) 技術を用いた。従来のHBM3と比べ、TSVの数は約2倍、パッケージの配線や配線間隔などを25%縮小したという。24GB製品のパッケージサイズは従来のHBM3と同じ11mm×11mm(図2)。1β nmプロセスによる製造は東広島工場で(参考資料2)、TSVによるパッケージングは台湾で行っている。

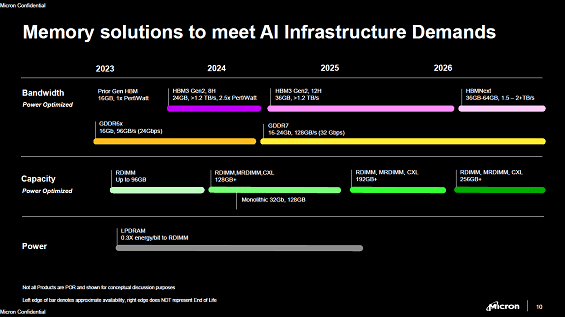

図3 HBM3 Gen2のロードマップ 出典:Micron Technology

Micronは今後のHBMのロードマップも発表しており(図3)、来年にはHBM3 Gen2製品でスタックした8個のDRAMダイのスタックから12個のダイをスタックする36GBのHBM3 Gen2を開発、リリースを予定している。HBM3の次はHBM3Eになるだろうと、Vaidyanathan氏は語っている。

参考資料

1. 「Micron、1β nmノードの64GビットのDDR5x-DRAMをサンプル出荷」、セミコンポータル (2022/11/08)

2. 「Micronの広島工場、1β nm製品の量産出荷を祝う」、セミコンポータル (2022/11/22)