2024年8月 5日

|週間ニュース分析

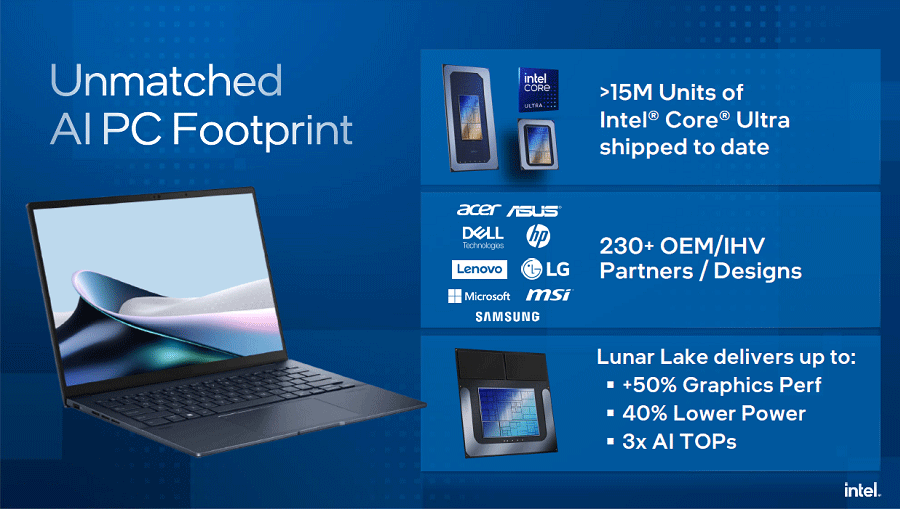

先週、IntelおよびSamsungの2024年度第2四半期(4〜6月期)の決算がそれぞれ発表された。Intelは、売上額が前四半期、前年四半期とほぼ同じ128億ドルだったが、営業利益はほぼゼロという結果であった。Samsungの半導体部門の売上額は、前年同期比ほぼ2倍、前期比でも23%増の28兆5600億ウォン(1ウォン=0.00073ドル)で、営業利益は6.45兆ウォンだった。

[→続きを読む]

2024年7月29日

|週間ニュース分析

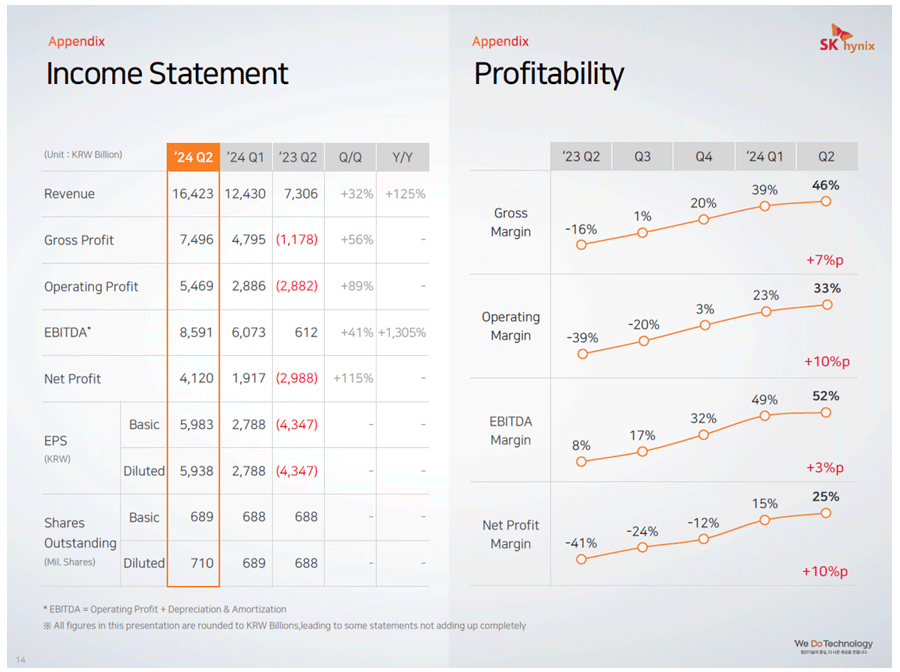

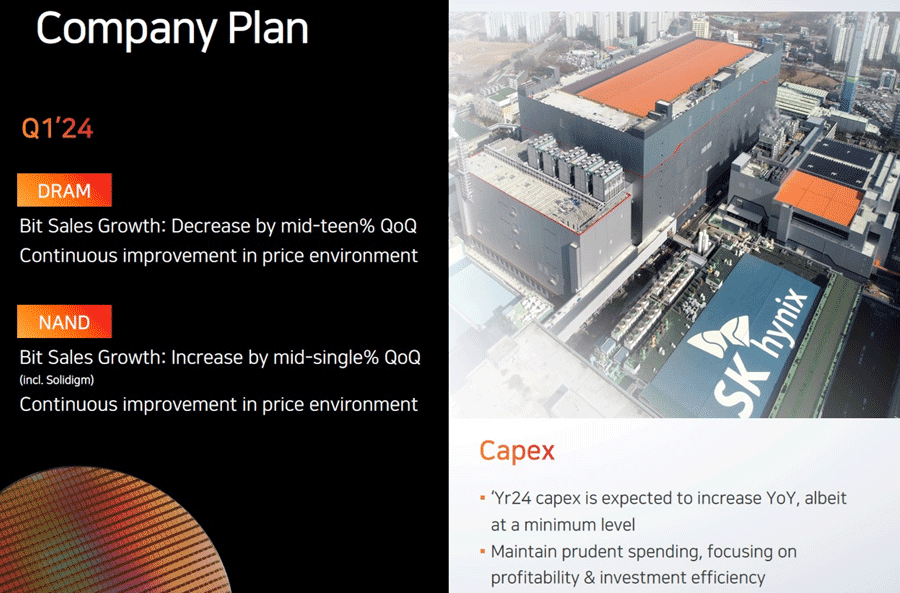

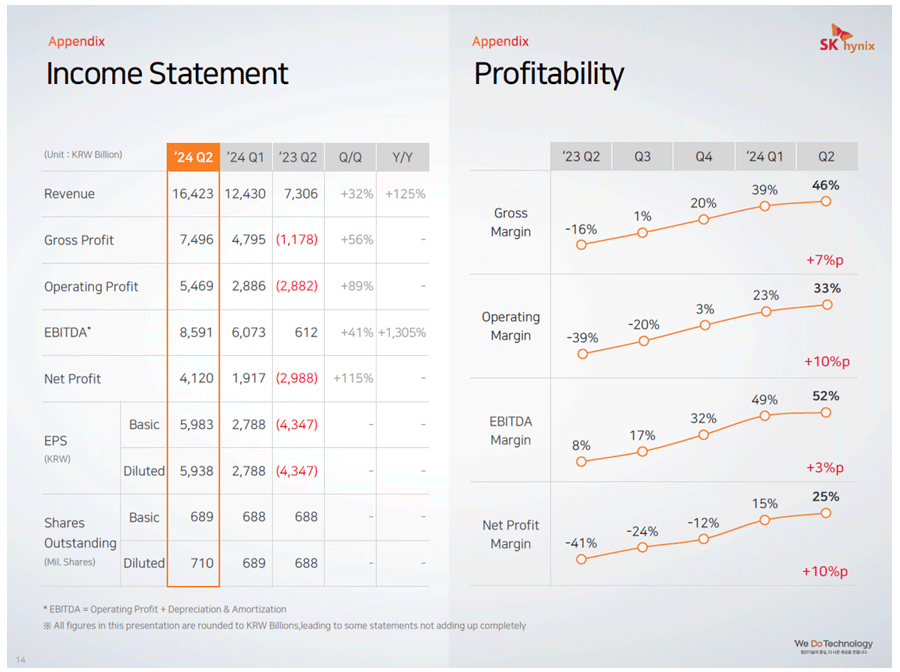

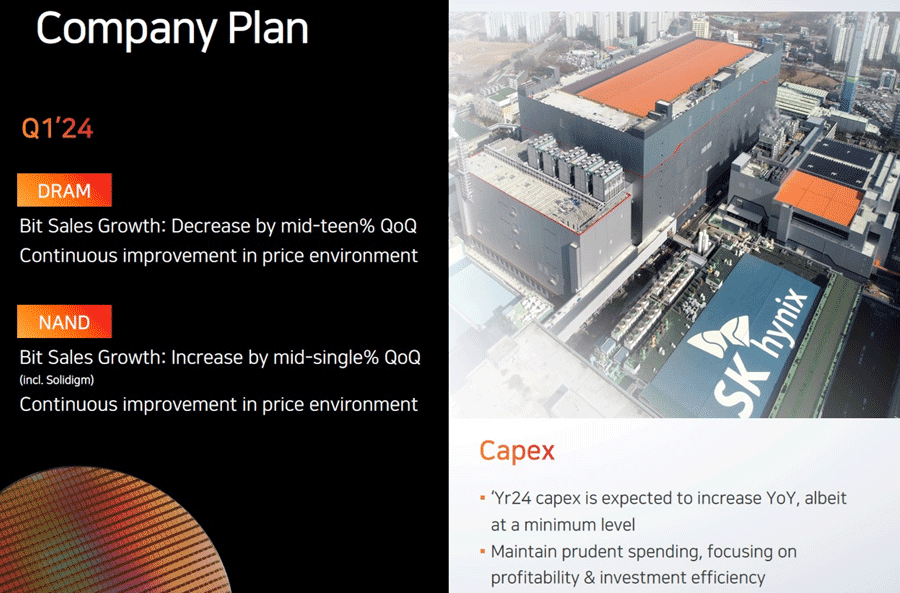

メモリビジネスは好調、産業向け非メモリビジネスはまだ不調。このようなビジネス状況が浮かび上がった。2024年第2四半期(4〜6月期)におけるメモリの韓国SK hynixの売上額は、前年同期比(YoY)2.25倍の16兆4230億ウォン(1ウォン=0.11円)と好調だったのに対して、マイコンとSoC、アナログのルネサスエレクトロニクスの売上額は同2.7%減の3588億円となった。

[→続きを読む]

2024年7月23日

|産業分析

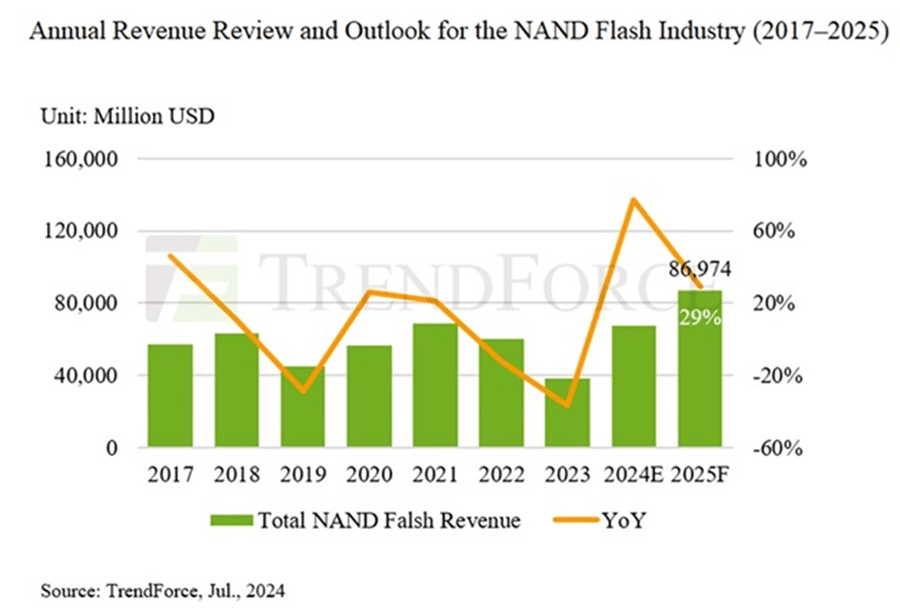

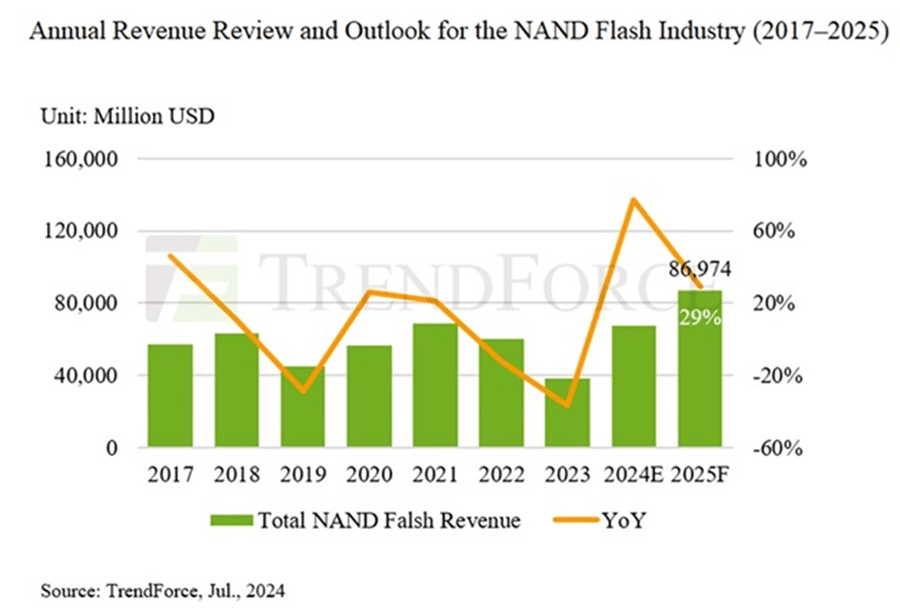

2024年におけるNANDフラッシュとDRAMのメモリの売上額は前年比でそれぞれ77%、75%と大きく伸びるだろうと、TrendForceが発表した。在庫がほぼ一掃され需給状況が改善、平均単価も上がってきたためだ。メモリはようやく回復が本物になり、来年は大きく成長すると見込んでいる。

[→続きを読む]

2024年7月 8日

|週間ニュース分析

米国のテキサス州が半導体産業に14億ドル(約2300億円)を補助すると7月6日の日本経済新聞が報じた。Samsung電子は2024年4~6月期の営業利益が10兆4000億ウォン(約1兆2100億円)だったと発表した。メモリ市況は回復しつつあり、SK Hynixは2028年までの5年間に12兆円を投資すると発表、キオクシアも新技術開発により2Tビット品をサンプル出荷した。

[→続きを読む]

2024年5月10日

|産業分析

SK hynixは、次世代スマートフォン向けのストレージとなるNANDフラッシュの新規格Zoned UFS(あるいはZUFS 4.0)製品を開発した。エッジAI向けのストレージとして、2024年第3四半期に量産する計画である。経時劣化を改良し製品寿命は40%長くなるという。SK HynixはHBMの成功に続き、NANDでもAI応用メモリでの成長を狙う。

[→続きを読む]

2024年5月 7日

|週間ニュース分析

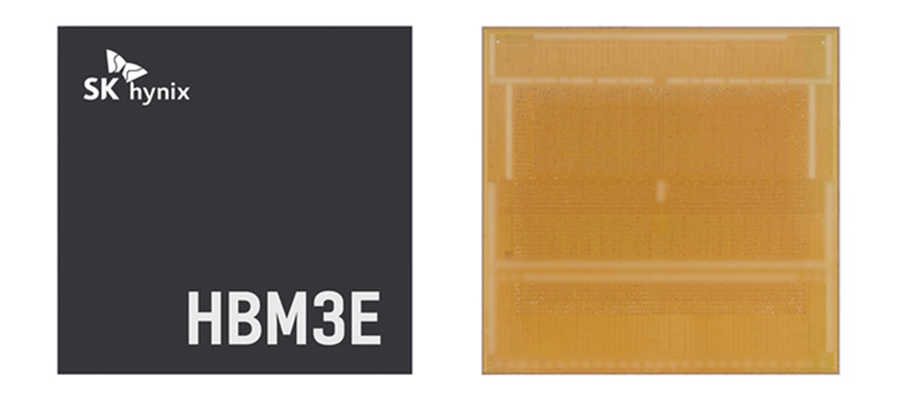

長いゴールデンウィークが開け、その間DRAMメーカーのHBM(High Bandwidth Memory)への開発が続々発表された。これまで圧倒的にリードしてきたSK Hynixに続きSamsung、さらにMicron TechnologyなどがHBM製品をサンプル出荷している。2日にはファウンドリPSMCが新工場を台湾に設立、半導体産業は攻めの姿勢を見せた。

[→続きを読む]

2024年4月25日

|技術分析(半導体製品)

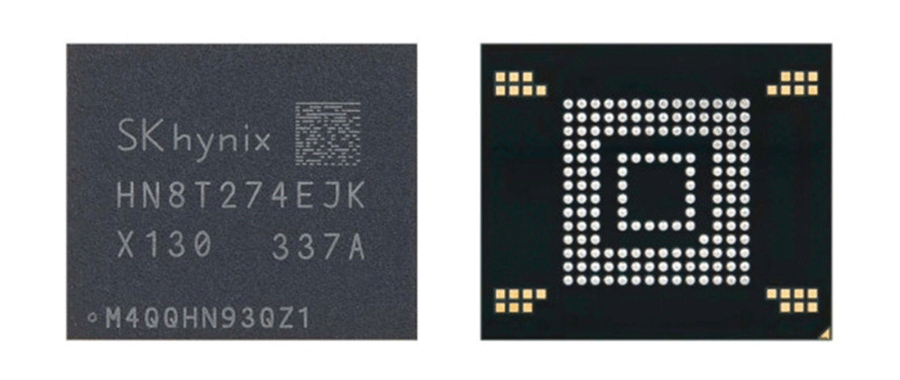

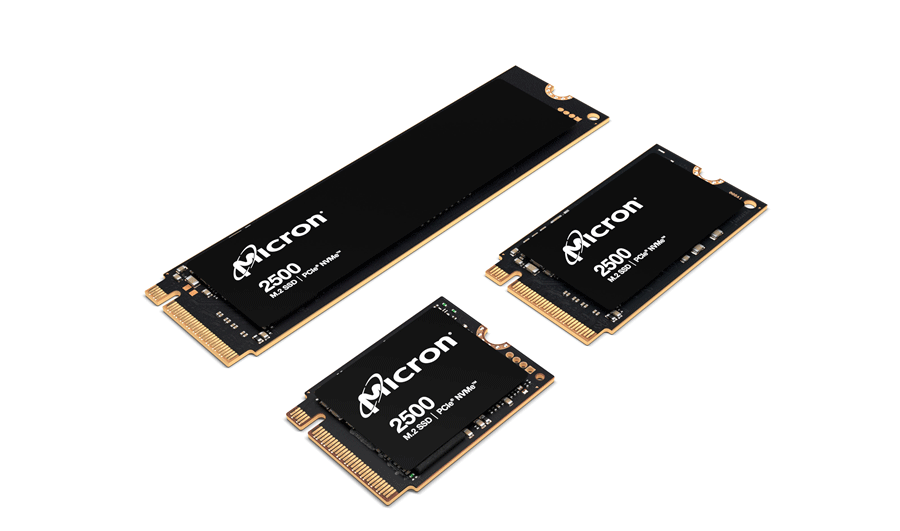

Micron Technologyは、512GBから2TBまでの容量を持つ、クライエントSSD(半導体ディスク)「Micron 2500 NMVe」のサンプル出荷を開始した。このSSDには232層でQLC(Quad Level Cell)を持つNANDフラッシュ(図1)を搭載している。また、このNANDフラッシュを搭載した企業向けストレージ顧客向けの「Crucial SSD」は量産を開始した。

[→続きを読む]

2024年4月 5日

|産業分析

台湾地震に遭われた方々にお見舞い申し上げます。

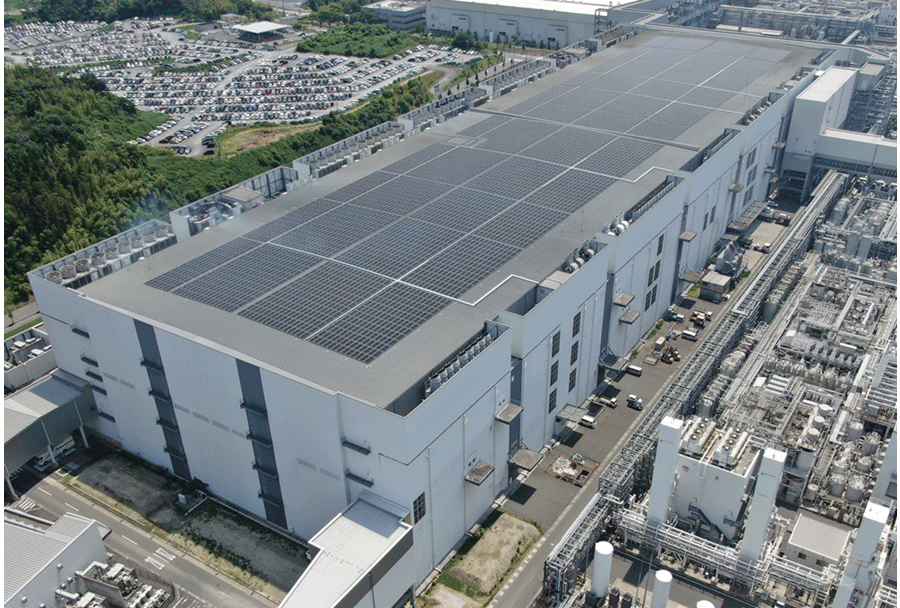

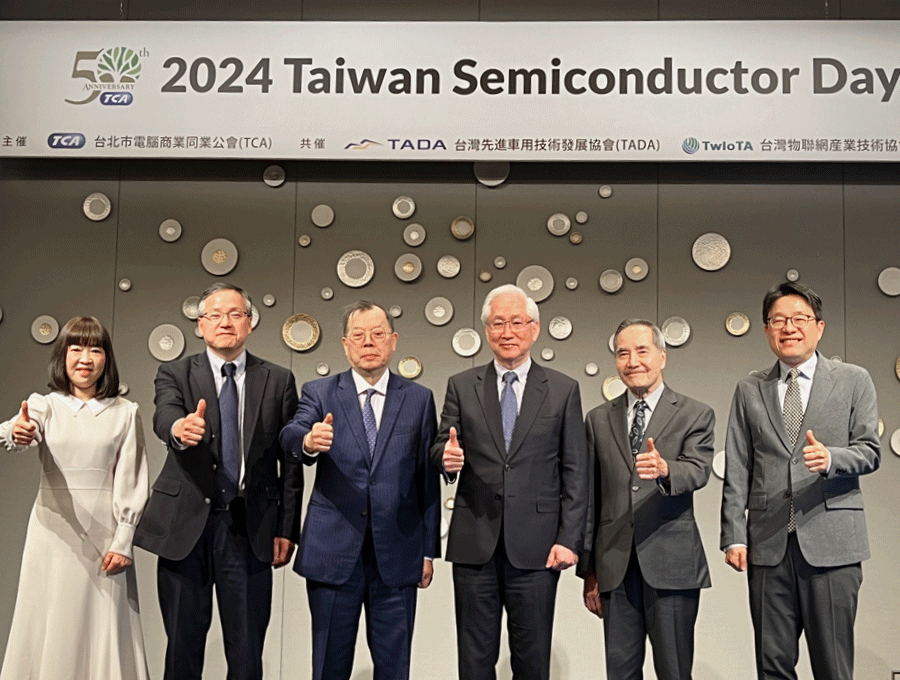

その前日(4月2日)、東京で「2024年台湾半導体デー」が開催された。台湾のPSMC(Powerchip Semiconductor Manufacturing Corp.)は宮城県に日本のSBIと共同でファウンドリ工場を建設する予定であり、そのPSMCの会長兼CEOのFrank Huang氏がこのイベントで講演した。

[→続きを読む]

2024年2月28日

|技術分析(プロセス)

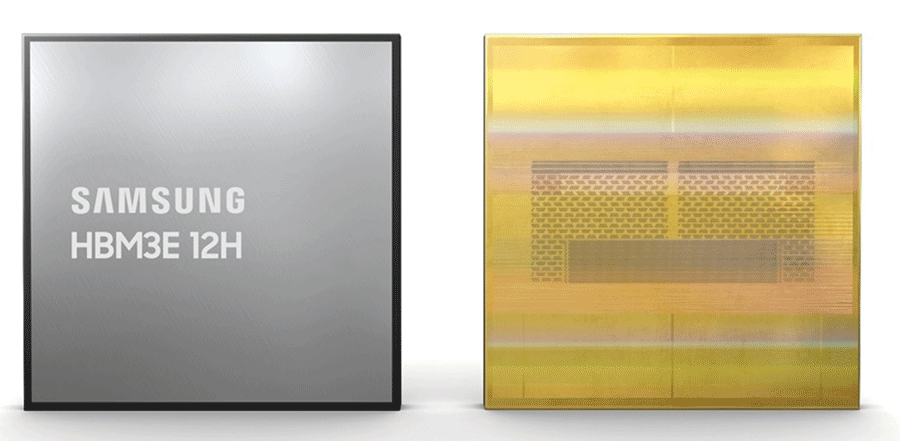

Micron、Samsungが3D-IC技術を使ったDRAMメモリであるHBM3Eを相次いで製品化した(図1)。HBMメモリは大容量のメモリを一度に大量に並列読み出しできるデバイスであり、AIチップやSoCプロセッサと一緒に使われる。SK hynixがこれまでHBM1や2、3のメモリ製品に力を入れてきたが、コストがかかるため他社はあまり力を入れてこなかった。

[→続きを読む]

2024年2月 5日

|週間ニュース分析

先週、2023年第4四半期(4Q)におけるSamsungの決算発表があり、SK hynixと共にメモリトップ2社の4Q業績が明らかになった。これによるとSamsungのDRAMはすでに黒字に転換したと述べ、NANDフラッシュはまだ赤字のままのようだ。DRAMはAIチップとセットで使われるため、生成AI向けに需要の回復が早い。NANDの回復は遅れているようだ。

[→続きを読む]