2025年9月 9日

|技術分析(半導体製品)

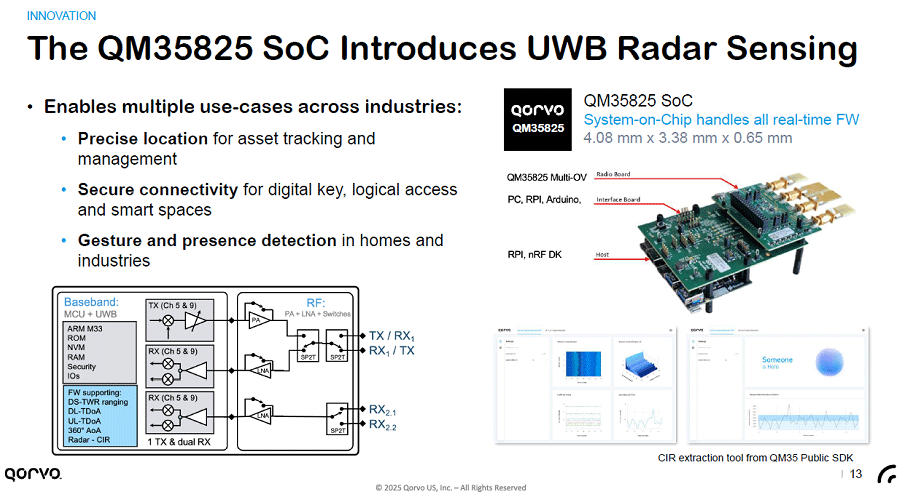

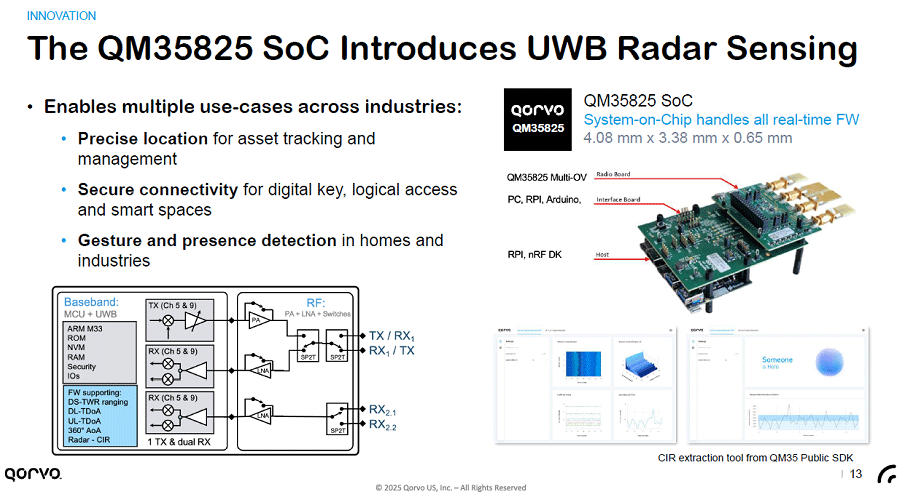

かつて超高速のデータレートを誇ったUWB(Ultra-Wide Band)通信が復活する兆しを見せている。UWBは中心周波数6GHzあるいは8GHzで周波数帯域が500MHzあるいは1.5GHzを利用し、480Mbpsの高速通信する技術だったが、Wi-Fiの高速化に押され姿を見なくなった。しかし、高周波・高データレートの通信用途ではなく、位置検出やレーダー応用(図1)として再登場しそうなのだ。

[→続きを読む]

2025年8月14日

|技術分析(半導体製品)

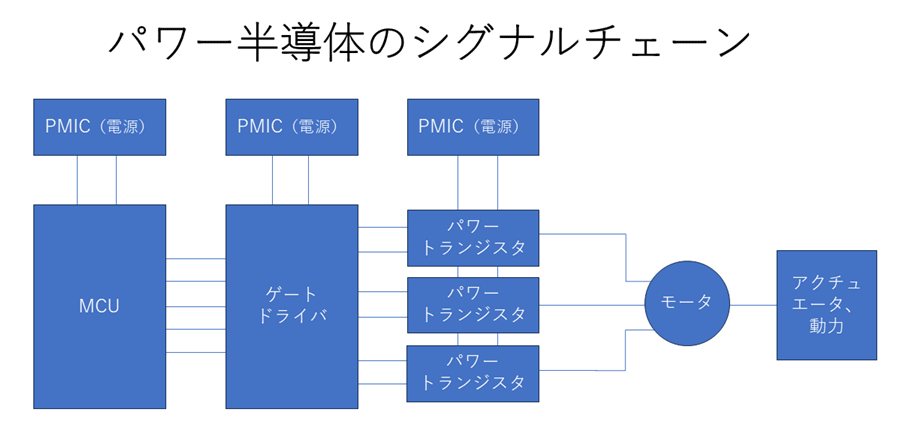

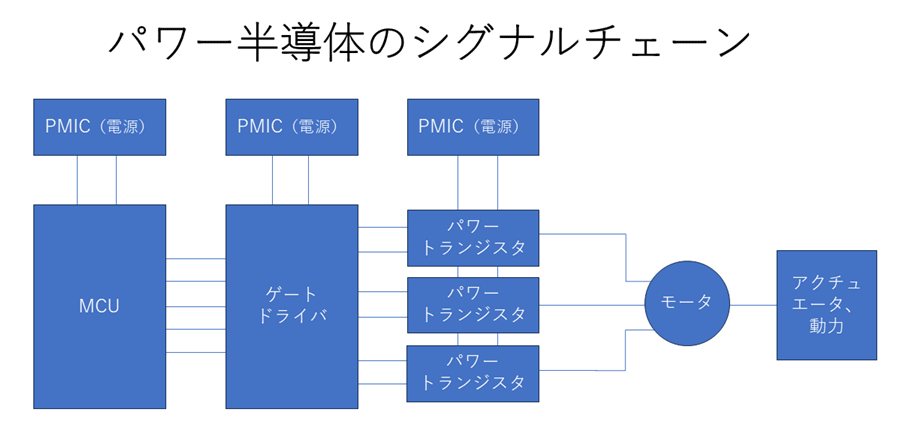

STMicroelectronicsがパワー半導体のシグナルチェーンにおいて、SiP(システムインパッケージ)手法を用いて、モータドライブ用の半導体開発に活かしている。パワー半導体がシリコンのMOSFETからGaN HEMTやSiC MOSFETなどに変わっても、このシステムは変わらない。SiPは、小型、インテリジェント、高性能、低コストなどメリットは多い。

[→続きを読む]

2025年8月 8日

|技術分析(半導体製品)

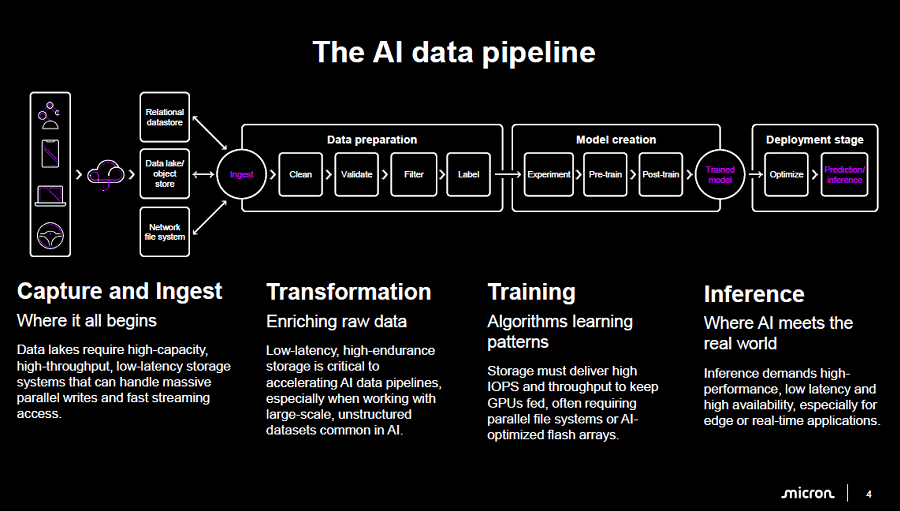

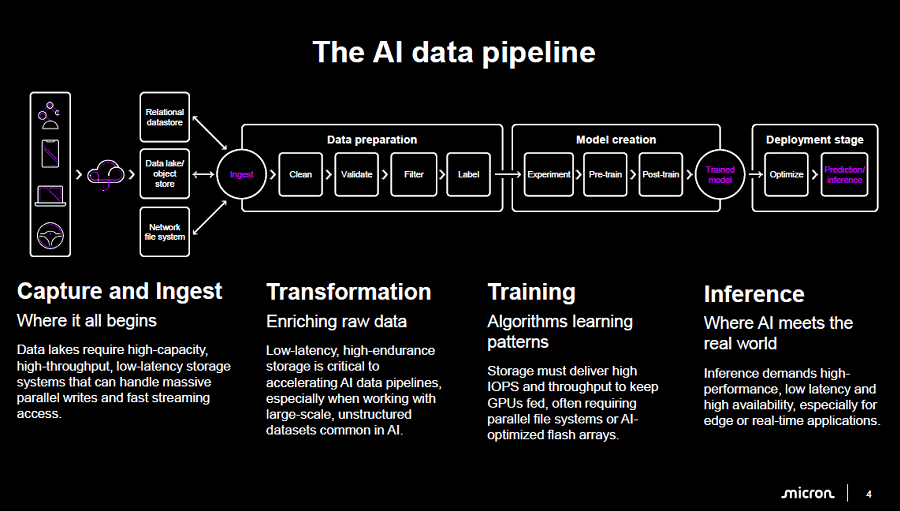

Micron Technologyは、昨年7月に発表した第9世代(G9)のNANDフラッシュ技術を用いてAIデータパイプラインに沿ったストレージのあり方として、新型SSD(半導体ディスク)の「Micron 6600 ION」、「Micron 7600」、「Micron 9650」を発表した。それぞれAIの学習・推論の処理工程に使う。G9の最大の特長はIO速度であり、AI利用では層数争いではなく、スピード競争になりそうだ。

[→続きを読む]

2025年7月10日

|技術分析(半導体製品)

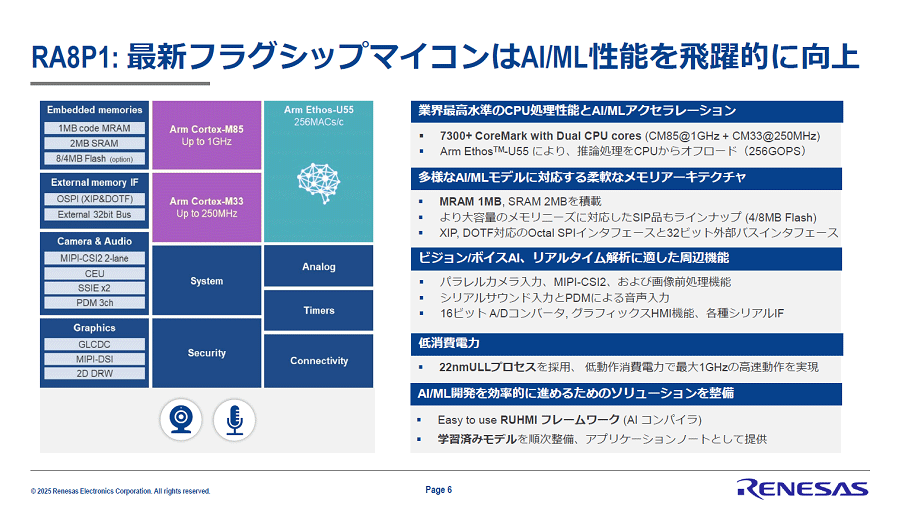

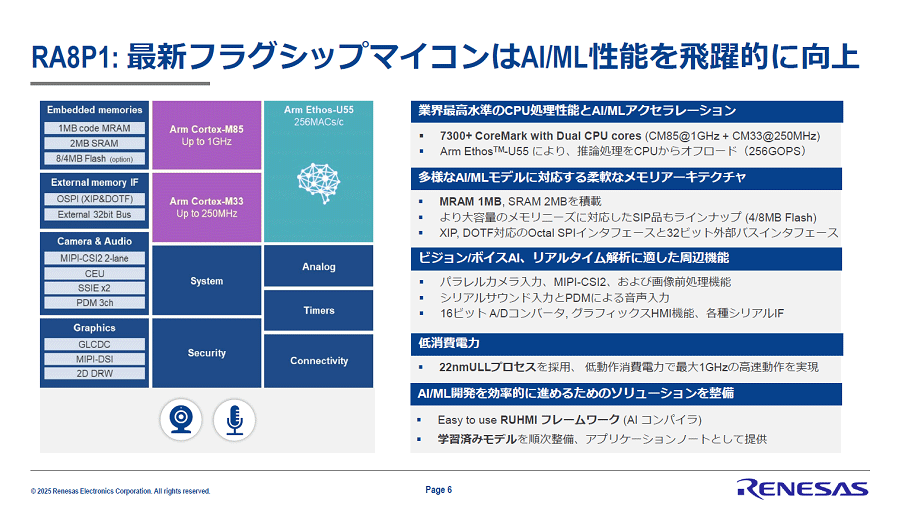

ルネサスエレクトロニクスは、マイクロコントローラ(MCU)の微細化を進めるために従来のNORフラッシュに代えてMRAMで22nm以降に対応する。微細化するのは、高集積化のためだが、従来のマイコンCPUに加え、AI専用のNPU(ニューラルプロセッサ)コアも集積しているのが特長だ。このほど第1弾としてAIoT向けの次世代マイコン「RA8P1」をサンプル出荷している。

[→続きを読む]

2025年4月24日

|技術分析(半導体製品)

Infineon TechnologiesがこれからのSD-V(ソフトウエア定義のクルマ)時代を迎え、CPUコアとしてRISC-Vを採用することを明らかにした(図1)。RISC-Vコアは米カリフォルニア大学バークレイ校の教授らが開発した、オープンソースのCPUコアであり、誰でも利用できる。とはいえ、非常にシンプルな命令セットなので自分で開発する場合には必要な命令セットやパイプライン構造、マルチコア対応などを作り込む必要がある。なぜInfineonはRISC-Vに力を入れるのか。

[→続きを読む]

2025年4月 9日

|技術分析(半導体製品)

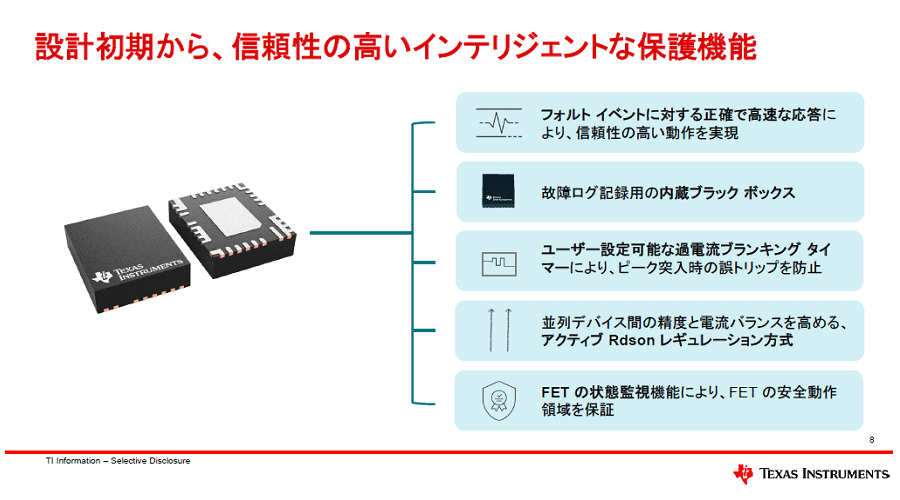

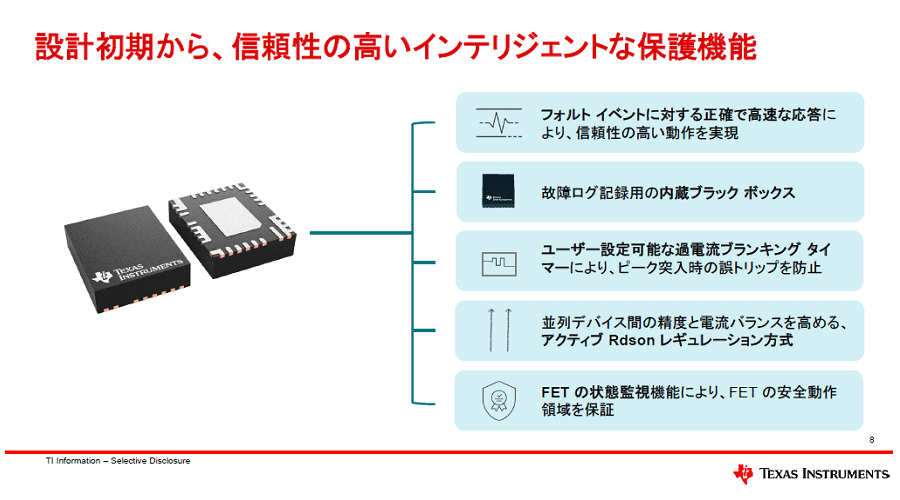

Texas Instrumentsは、並列接続により最大6kWまでの電力を扱うことのできる電子フューズ(eFuse)IC、「TPS1685」を開発した。これによりますます電力を消費するデータセンターの電源を確保できるようになる。一般のeFuseをただ単に並列にしても、MOSFETのオン抵抗や配線パターンの抵抗やコンパレータのしきい電圧のバラつきなどによって、弱い部分に電流集中が起こりやすくなる。しかしこれを防いだ。

[→続きを読む]

2025年3月18日

|技術分析(半導体製品)

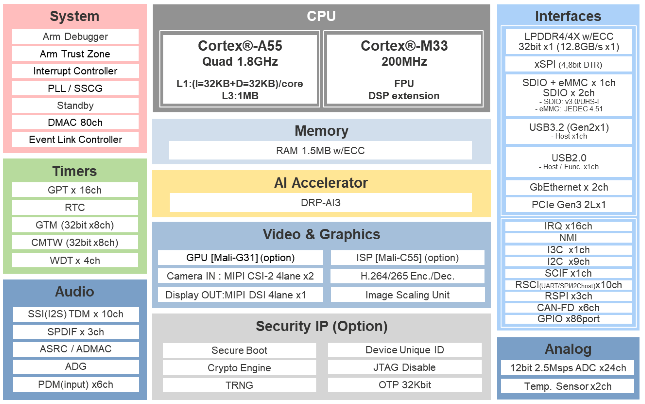

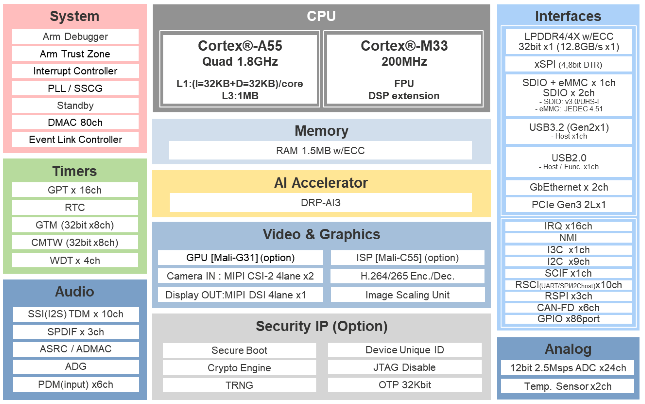

ルネサスエレクトロニクスは、手ごろな価格で画像認識AIが使える新しいAIアクセラレータを集積したミッドレンジのプロセッサ「RZ/V2N」をドイツのニュルンベルグでのEmbedded World 2025で展示した。2台のカメラ画像を取り込める上に、クルマのドライブレコーダーや自動走行ロボットのカメラ、監視カメラなどコンピュータビジョンに対応する。3月19日に発売する。

[→続きを読む]

2025年3月 4日

|技術分析(半導体製品)

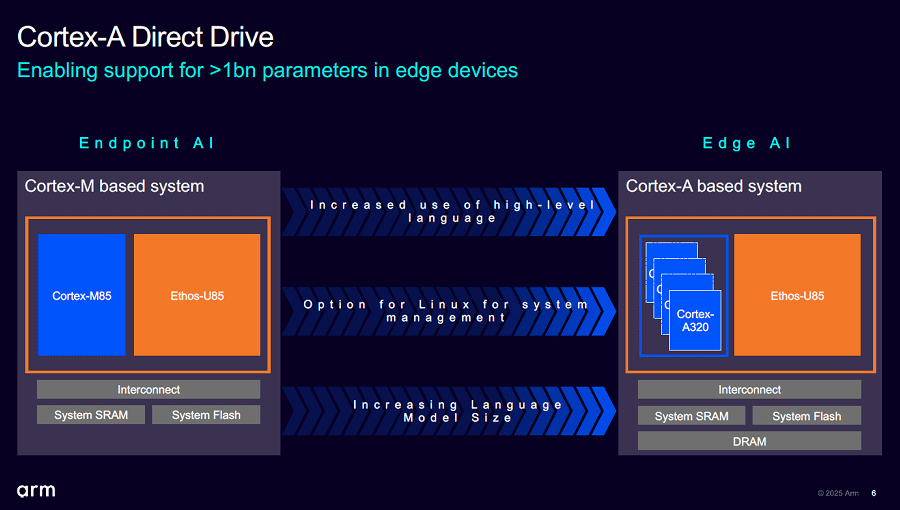

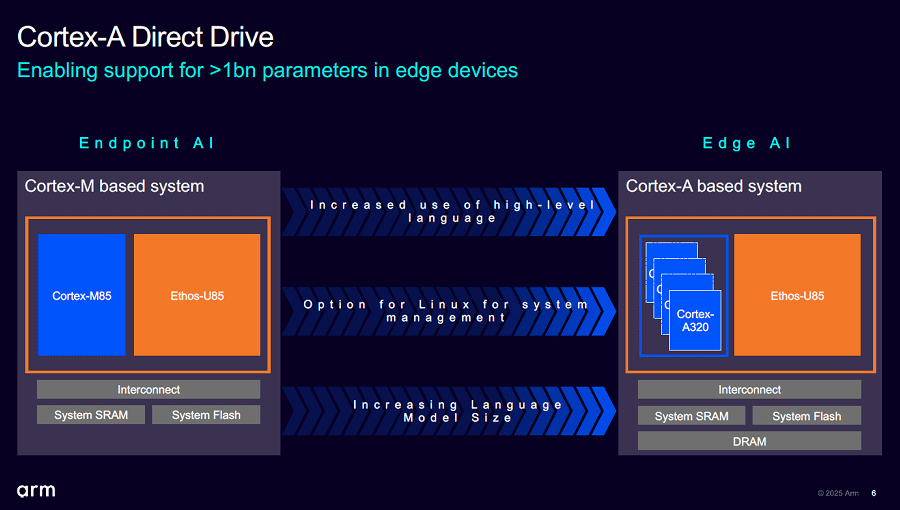

高性能なCPUとAI専用のNPU(ニューラルプロセッシングユニット)を集積したIP(知的財産)コアをArmが開発した。高性能ビデオ伝送をはじめとする高速IoT(Internet of Things)に対応するIPコアである。高性能な技術であるArmv9をエッジAIのプラットフォームとして使う用途が早くも生まれたために、このような高性能IoT向けのIPを開発した。具体的にはどのような用途だろうか。

[→続きを読む]

2025年2月14日

|技術分析(半導体製品)

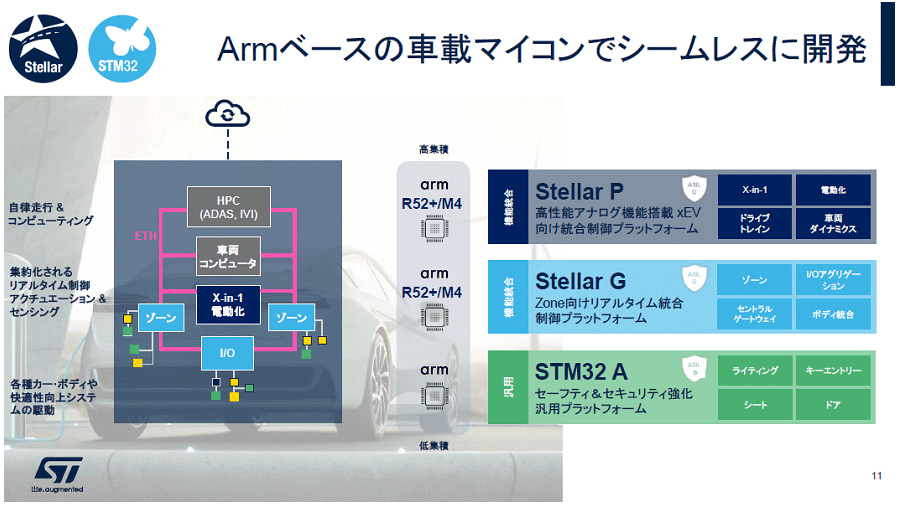

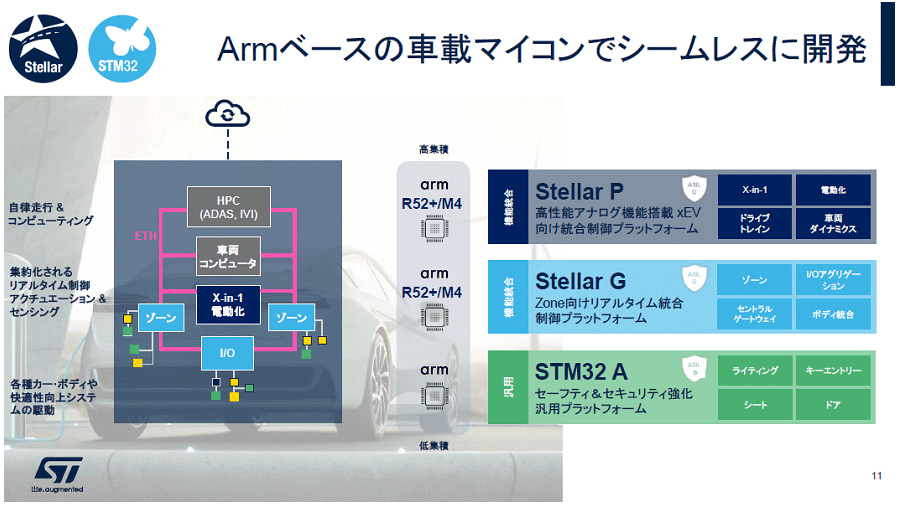

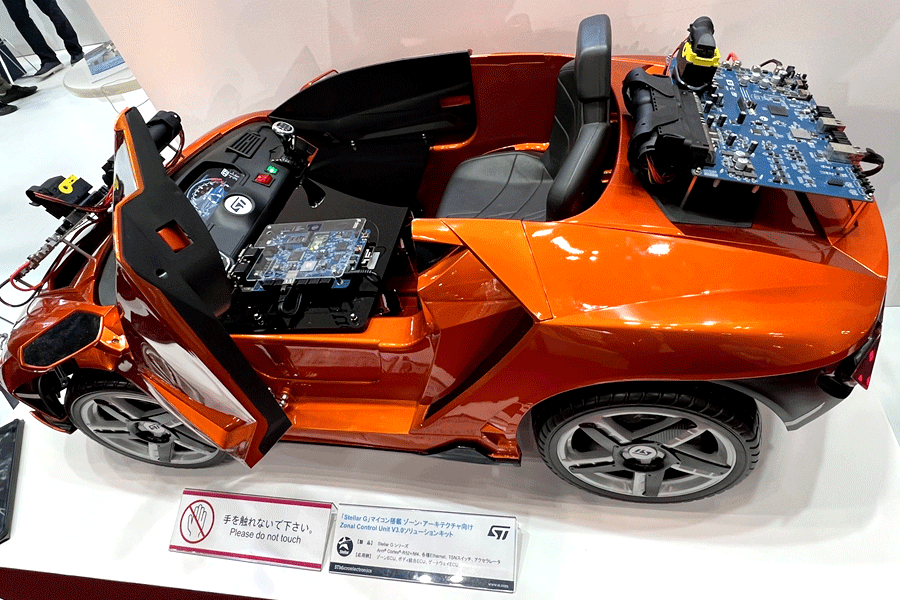

STMicroelectronicsは、ゾーンアーキテクチャに向いたMCU(マイコン)「Stellar」のシリーズを明らかにした。先行して販売していたStellar Eシリーズに対して、Armマルチコアによる仮想化技術を採り入れている。その高集積化のためNORフラッシュメモリに代わりPCM(相変化メモリ)を用い28nm、18nmへと微細化で対応する。

[→続きを読む]

2025年2月 5日

|技術分析(半導体製品)

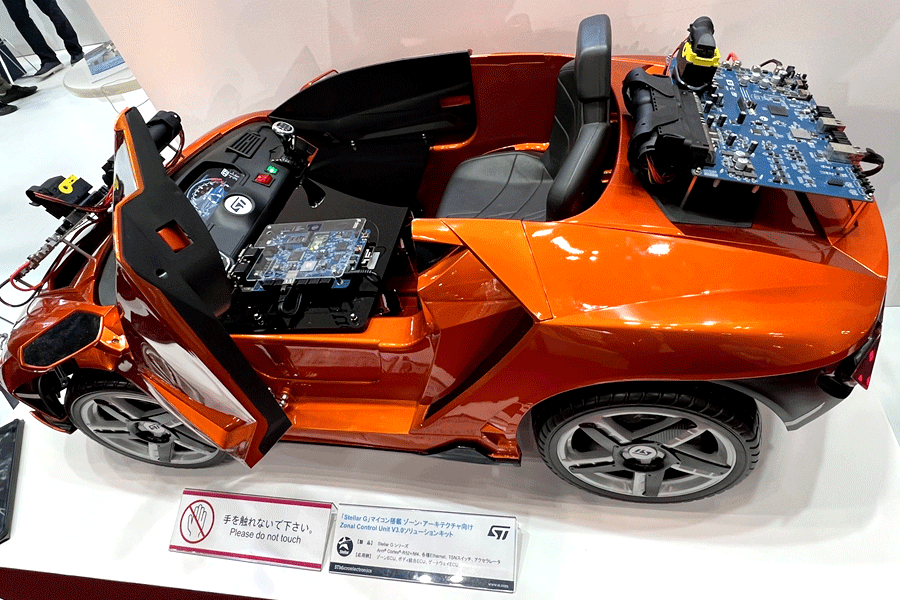

オートモーティブワールド2025では、半導体メーカーが単なるパワー半導体を展示するのではなく、実際のEV(電気自動車)に組み込む装置の能力を示すというブースが目立った。これからのクルマのテクノロジーに使えるレベルの能力を見せつけた。その中から事例としてSiCパワー半導体のスイスのSTMicroelectronics(図1)と、8Gbpsと高速のSerDesを開発したイスラエルのValensを紹介しよう。

[→続きを読む]