2026年2月 4日

|産業分析

2026年2月3日、Intel Connection Japanが東京虎ノ門ヒルズで開催された。Intelは新型メモリを開発するというソフトバンク100%子会社のSaimemory(サイメモリ)と協業すると発表した。しかし、その中身についてはほとんど話していない。共同で次世代メモリを開発し2029年に実用化を目指すとしている。どのようなメモリなのか、これまでの米国DoE(エネルギー省)傘下の国立研究所とIntelとの協業から探ってみよう。

[→続きを読む]

2026年1月13日

|週間ニュース分析

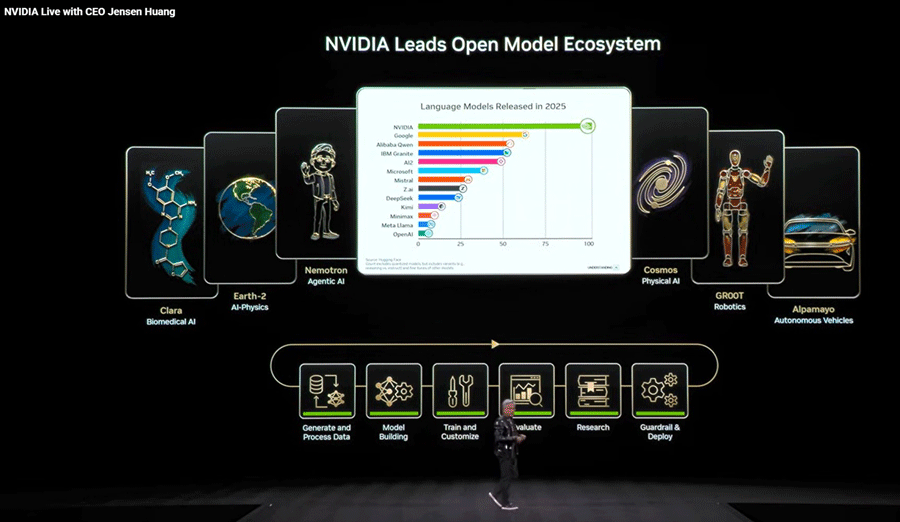

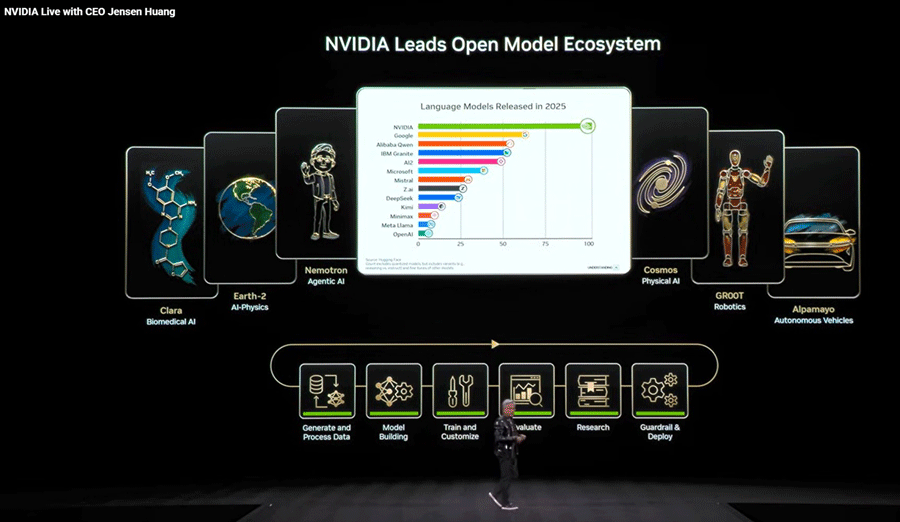

先週、米国ラスベガス市で開催されたCES 2026では、事前のメディア向けの展示会では「フィジカルAI」というキーワードが注目されるとのことだった。基調講演を聴く限り、フィジカルAIといえるほど賢いロボットはなかったようだ。むしろ地に足を付けた、生成AIを超える数々のテクノロジーをNvidiaのJensen Huang CEOが講演で示した。

[→続きを読む]

2026年1月 9日

|技術分析(半導体製品)

フィジカルAIが注目される中(参考資料1)、やはりCESでも高性能なエッジAIチップが発表された。発表したのは、画像処理ICとしてスタートした企業から今やエッジAIチップのファブレス半導体に成長したAmbarella社。AIを搭載したドローンや自動運転車、ロボットなどフィジカルAIに向けたビジョンSoC「CV7」は8K画像の認識や分類などを行うエッジAIチップである。

[→続きを読む]

2026年1月 7日

|技術分析(半導体製品)

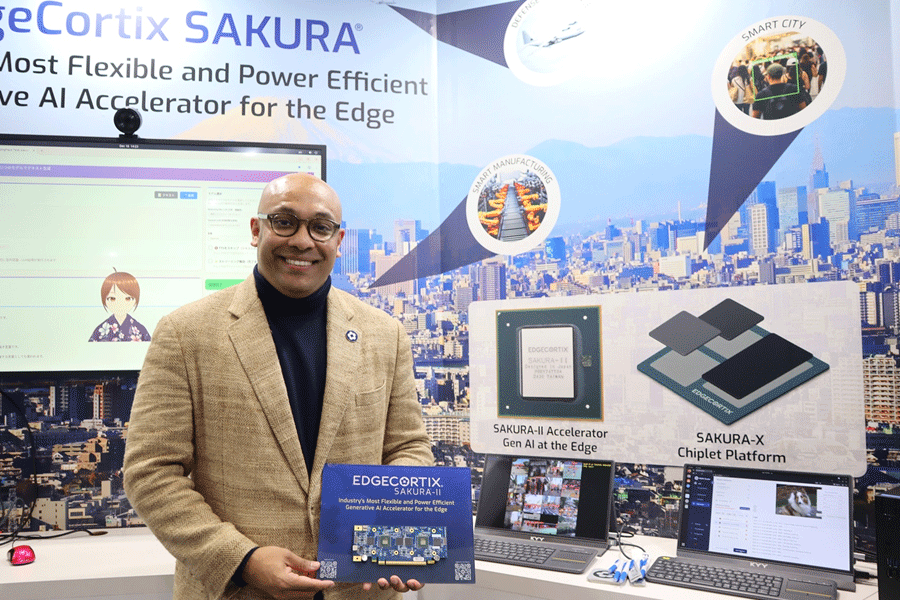

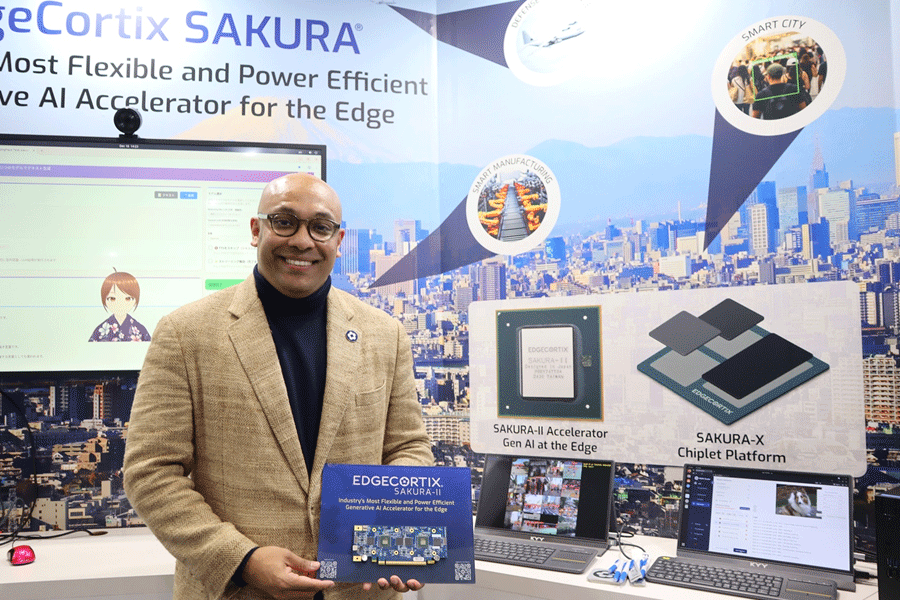

エッジAI市場よりもクラウド向けのAIデータセンターへの投資がすさまじいが、本格的なAIロボットや自動運転、AIドローンなどフィジカルAIが次世代AI技術の一つとして注目が集まってきた。フィジカルAIはエッジで使われることの多いAIであり、エッジAIチップの性能向上やソフトウエア開発にも力が入る。SEMICON JapanではスタートアップのEdgeCortix、Texas InstrumentsがそれぞれエッジAIの応用をサポートし始めた。

[→続きを読む]

2026年1月 6日

|技術分析(半導体製品)

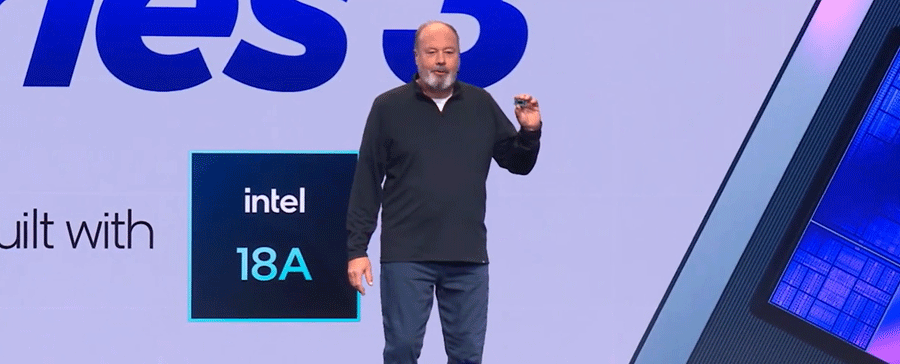

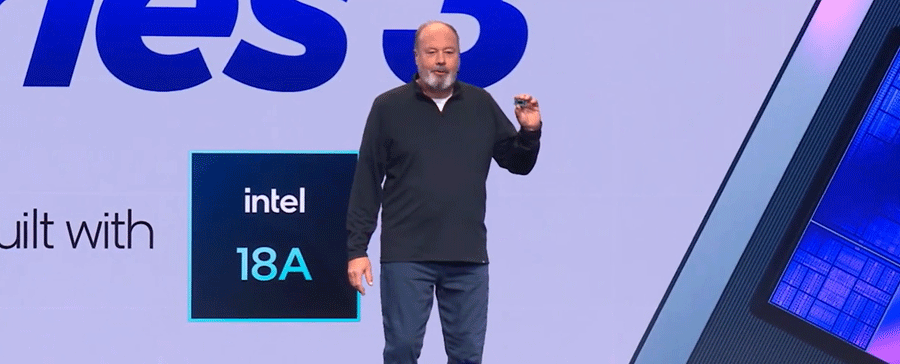

Intelが2nmプロセスの相当するIntel 18A技術を使った、パソコン向けの新しいSoC「Core Ultra シリーズ3(コード名Panther Lake)」の実性能・電力効率をCES 2026で発表した。セミコンポータルでも2025年11月にPanther Lakeの設計値などを公表していた(参考資料1)。Intelはさまざまなパートナーと共に評価・改良を続け、その基本的な実際の性能について発表した。

[→続きを読む]

2025年12月15日

|週間ニュース分析

ラピダスに民間企業22社が新規に出資、これまでの株主に加えて合計30社が株主になると12月13日の日本経済新聞が報じた。ラピダスはこれまでと同様、「当社が発表したものではない」とコメントを出している。TSMCが熊本第2工場に4nmプロセスを導入する検討をしている。Broadcomの評価が高まっている。AIチップ最大手のNvidiaのH200が中国輸出を認められたことに対して米国内で反発する声が高まっている。

[→続きを読む]

2025年12月12日

|産業分析

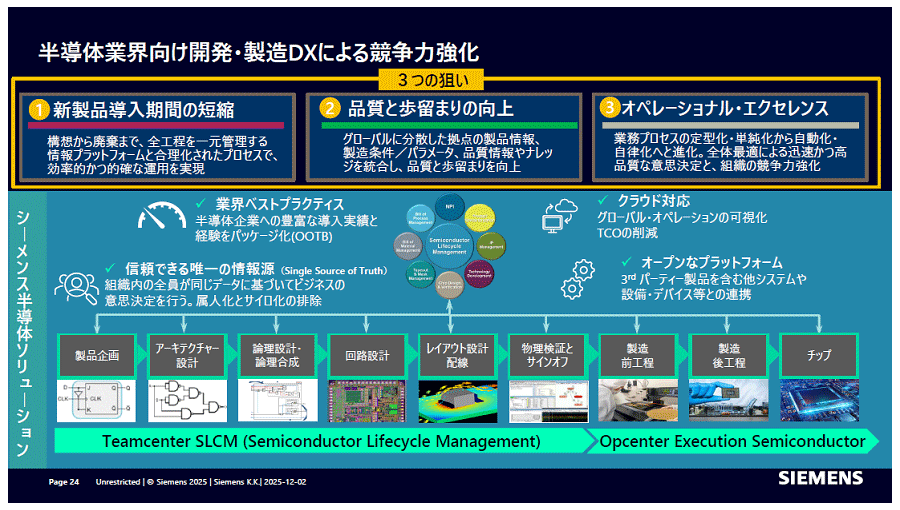

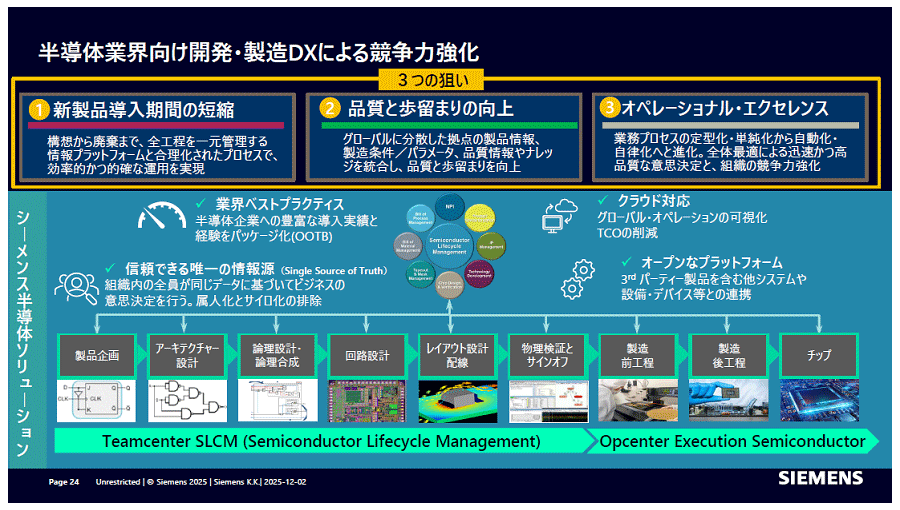

Siemens Digital Industries SoftwareがMentor Graphicsを2016年に買収して10年。AI時代に入り、半導体が注目され、機械系のソフトウエアと、半導体やプリント基板回路のEDAツールがつながり、モノづくりの総合EDAツールが揃ってきた。旧MentorはSiemens EDAの名称が定着、ものづくりツールとの連携がAI時代に進化を深めることになってきた。

[→続きを読む]

2025年12月 9日

|技術分析(半導体応用)

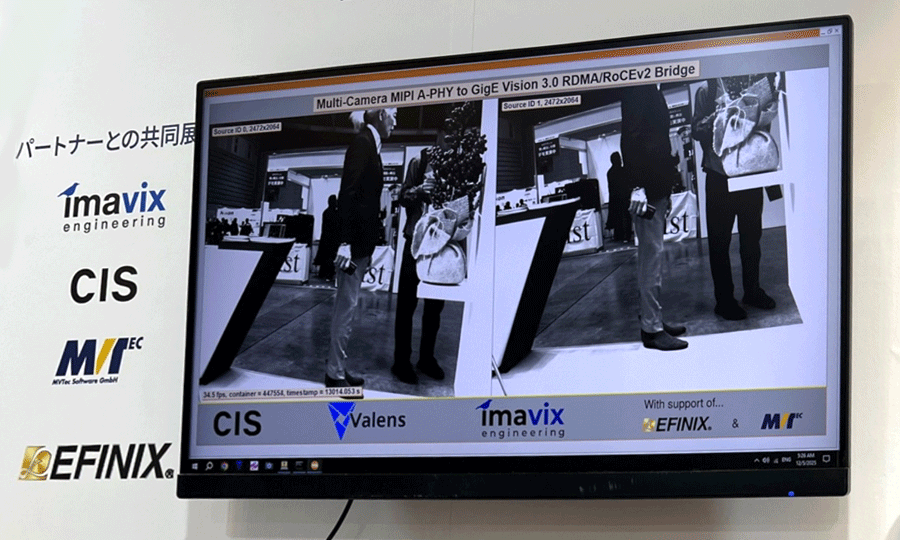

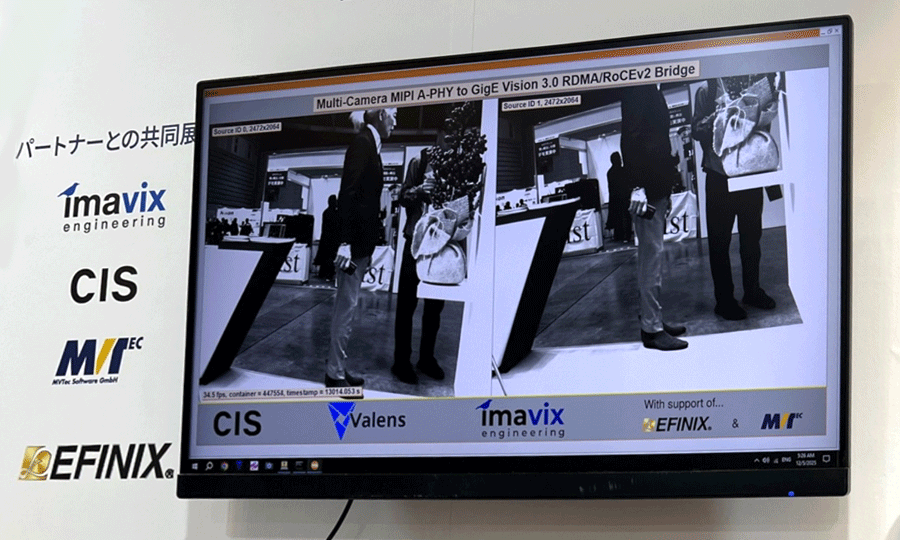

電磁波ノイズに強いSerDesチップを売りにしているValensは、自動車メーカーへの売り込みに成功した後、産業向けにも進出してきた。産業向けは独自仕様が多く、1社だけではシステムを設計・製造できないため、エコシステムの構築に力を注ぎ、顧客に提案できるまでになった。低消費電力、高性能、低コストのFPGAメーカーEfinixも参照ボード設計に加わった。

[→続きを読む]

2025年11月28日

|技術分析(プロセス)

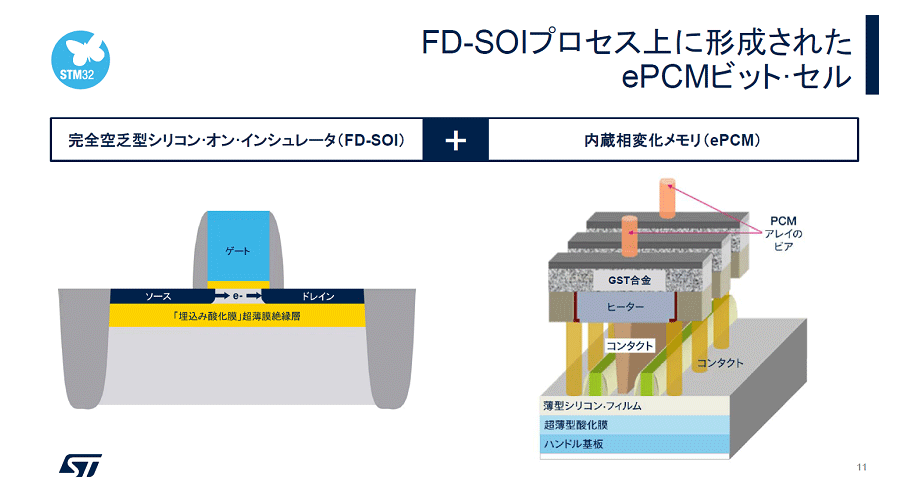

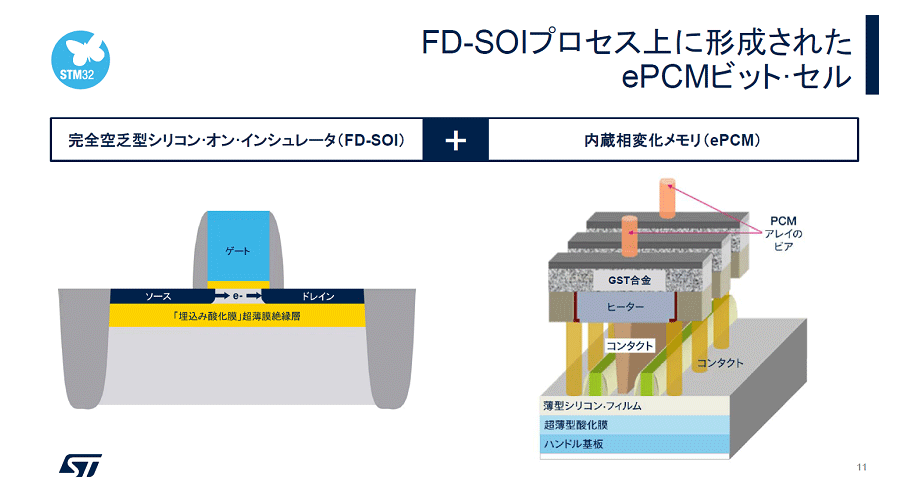

STMicroelectronicsは、初めてマイコンに18nmノードをもたらした。新製品STM32V8は、FD-SOI(完全空乏化シリコンオンインシュレータ)プロセスにPCM(相変化メモリ)を使い微細化を果たした。これまでのマイコンでは、NORフラッシュメモリを使っていたが、微細化が難しく40nmプロセスでほぼ止まっていた。28nm製品はあるが、ぎりぎりだった。実は、ストレージ部分をNORフラッシュから新型メモリに変えることでマイコンの性能は一段と上がることになる。

[→続きを読む]

2025年11月27日

|技術分析(半導体製品)

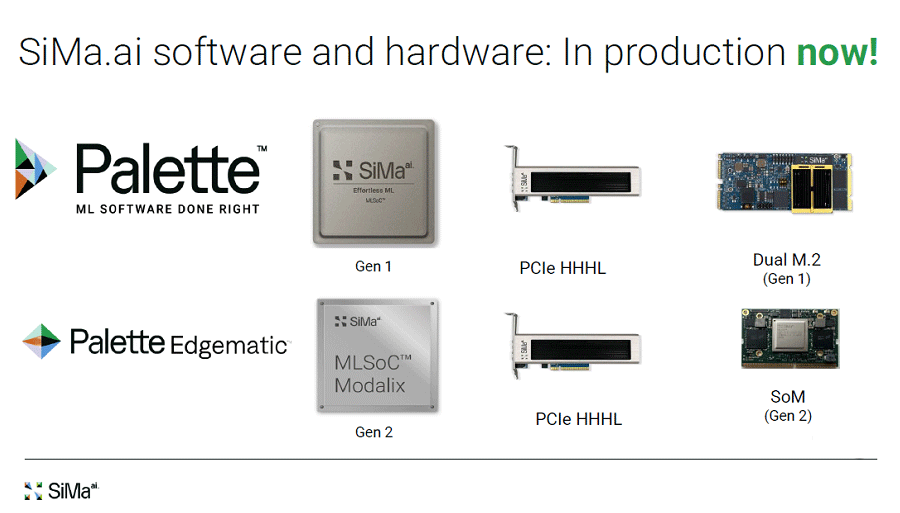

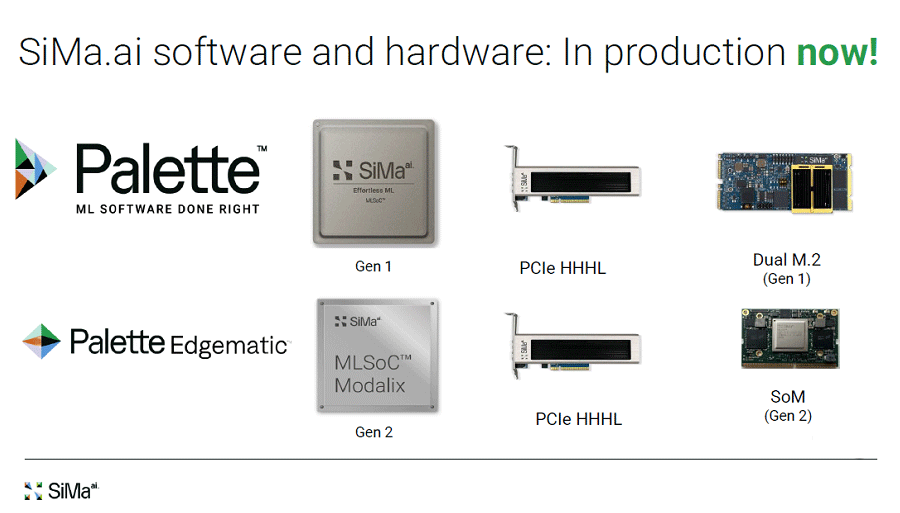

人が話しかければ、言葉で答えてくれる。しかもインターネットにつなぐ必要もない。こんなエッジAIを実現するAIチップをスタートアップのSiMa.ai(シーマドットエイアイ)が開発した。LLM(大規模言語モデル)を使って受け答えだけではなく、映像データも分析する。4000FPS(フレーム/秒)という超高速度映像にも対応する。エッジAIだからこそクルマやドローン、ロボット、監視カメラなどでの広い応用が期待される。

[→続きを読む]