2025年12月18日

|技術分析(プロセス)

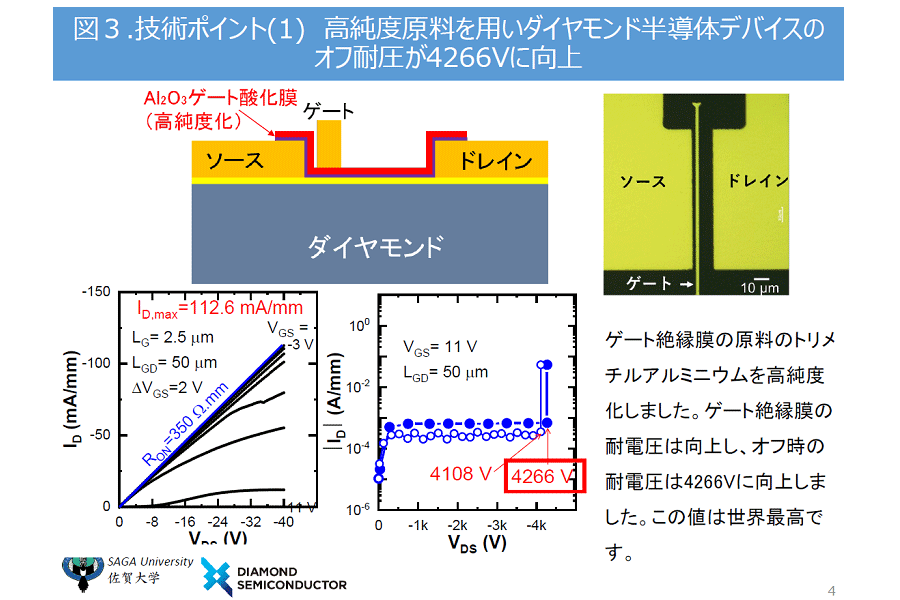

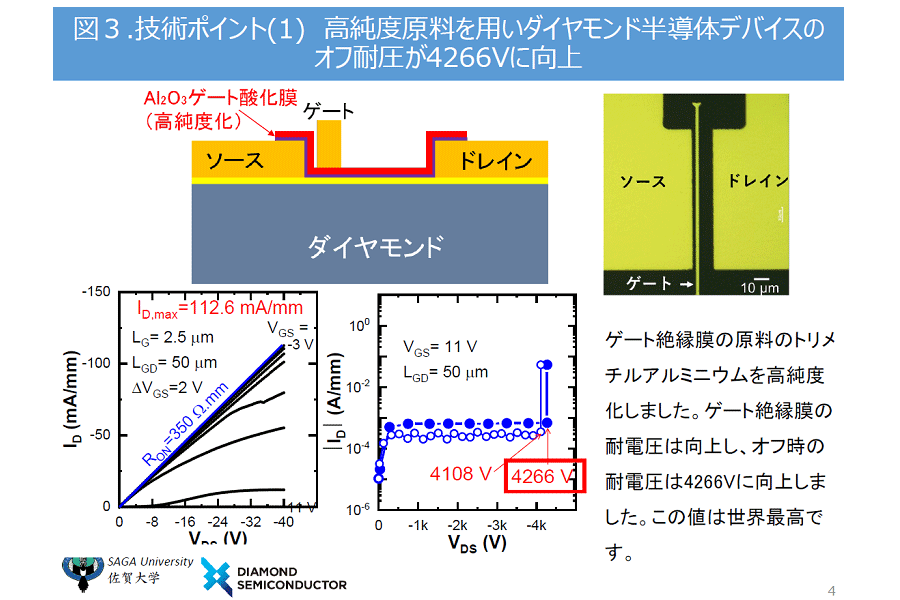

佐賀大学の嘉数誠教授らのグループは、ダイヤモンド結晶を使って半導体としてMOSトランジスタを試作し、その高周波特性を測定したところ、遮断周波数fMAXが120GHzを示した。ダイヤモンドはバンドギャップがシリコンの4.9倍もあり耐圧が高いため、パワー半導体への応用が期待されている。とはいえ、実際のトランジスタを形成することは簡単ではない。ゲート絶縁膜、n型/p型の形成などシリコンとは難しさが違う。

[→続きを読む]

2025年11月28日

|技術分析(プロセス)

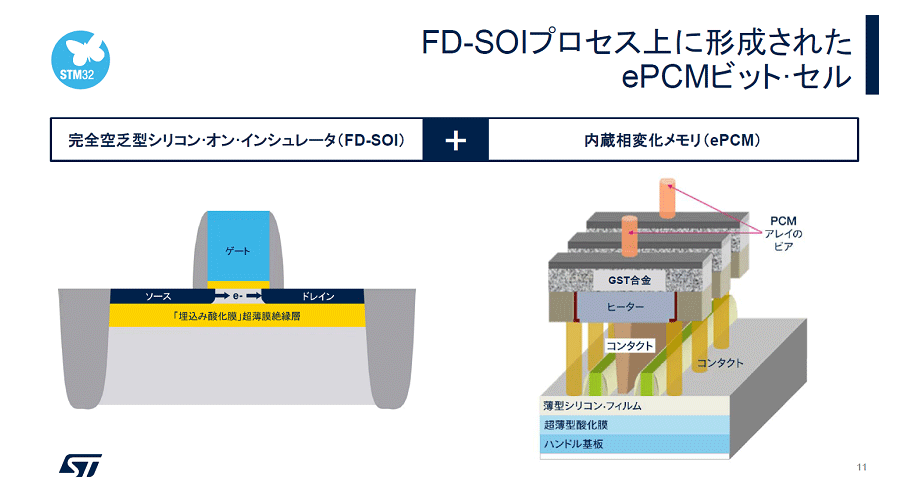

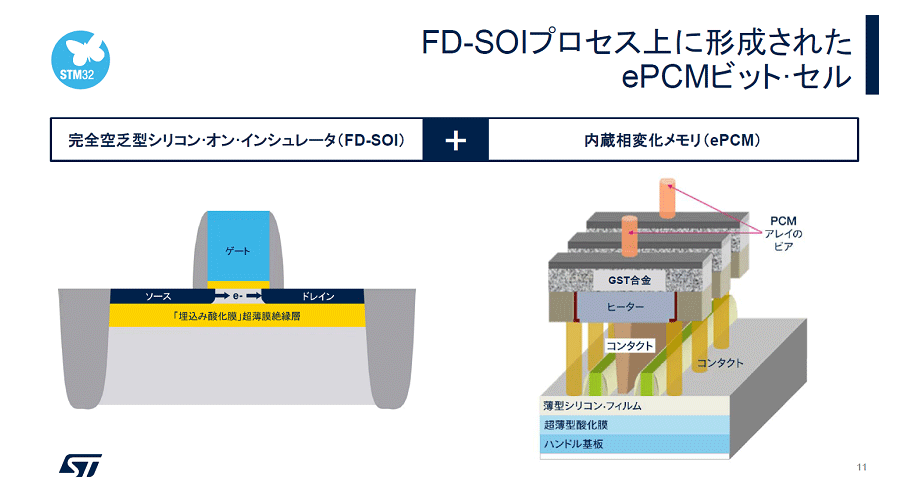

STMicroelectronicsは、初めてマイコンに18nmノードをもたらした。新製品STM32V8は、FD-SOI(完全空乏化シリコンオンインシュレータ)プロセスにPCM(相変化メモリ)を使い微細化を果たした。これまでのマイコンでは、NORフラッシュメモリを使っていたが、微細化が難しく40nmプロセスでほぼ止まっていた。28nm製品はあるが、ぎりぎりだった。実は、ストレージ部分をNORフラッシュから新型メモリに変えることでマイコンの性能は一段と上がることになる。

[→続きを読む]

2025年10月30日

|技術分析(プロセス)

TSMCが東京でTSMC 2025 Japan OIP(Open Innovation Platform)Ecosystem Forumを開催、この3年間AIによってOIPは成長した、とTSMCジャパンの小野寺誠社長(図1)が述べた。AIがあらゆるデバイスに入り新しい応用を生む時代に入ったことを印象付けた。AI時代ではコンピュータ能力をもっと欲しいという要求が高まり、さらに高集積になるSoC設計が難しくなってきた。

[→続きを読む]

2025年2月28日

|技術分析(プロセス)

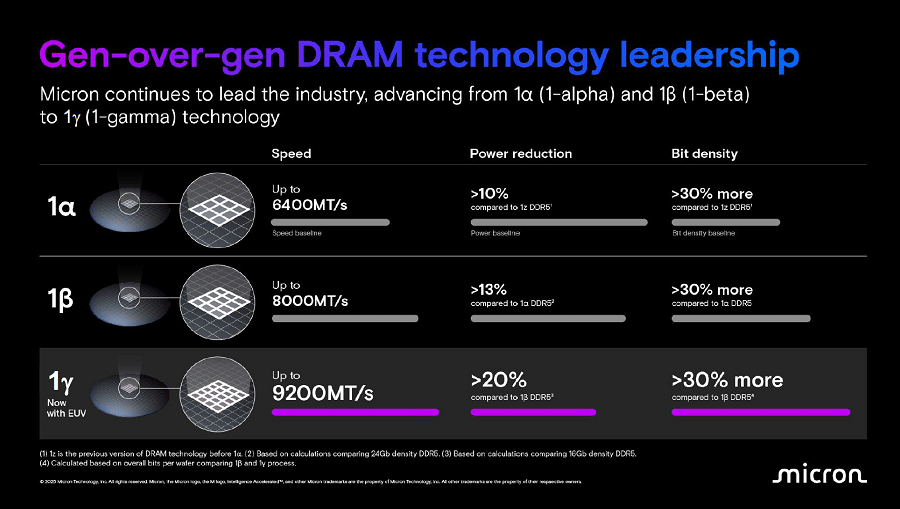

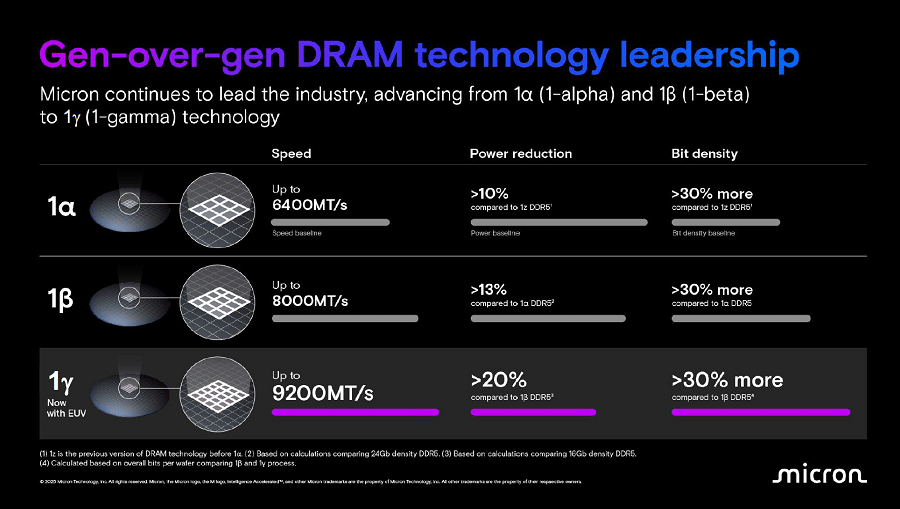

Micron Technologyが1γnmノードのDDR5DRAMをサンプル出荷した。1γnmというサイズは10nmクラスのようで、EUV装置の導入が必須になる。Micronの微細な技術によって、スピードは現世代の1βnmノードのDRAMと比べ、8Gbpsから9.2Gbpsと高速になり、消費電力は20%削減され、集積度は30%上げることができる(図1)。

[→続きを読む]

2024年7月 2日

|技術分析(プロセス)

AIコンピューティングパワーがけん引し、プロセスノードの微細化は早まっている、とTSMCシニアバイスプレジデント兼副共同最高業務執行責任者のKevin Zhang氏が述べた。これは6月28日に横浜でTSMC Technology Symposium Japanを開催した際、メディア向け技術説明会で述べたもの。

[→続きを読む]

2024年3月28日

|技術分析(プロセス)

2nmプロセスでは、EUVといえどもOPC(光学的近接効果修正)が必要になってくる。EUVの13.5nmという波長ではパターンをそのまま加工できなくなってきたからだ。2nmプロセスだと複雑すぎて試行錯誤的なアプローチはもはや使えない。計算機利用のリソグラフィの出番となる。NvidiaとTSMC、Synopsys、ASMLは、昨年エコシステムを構築したが(参考資料1)、TSMCの量産ラインに計算機リソを導入していることが明らかになった。

[→続きを読む]

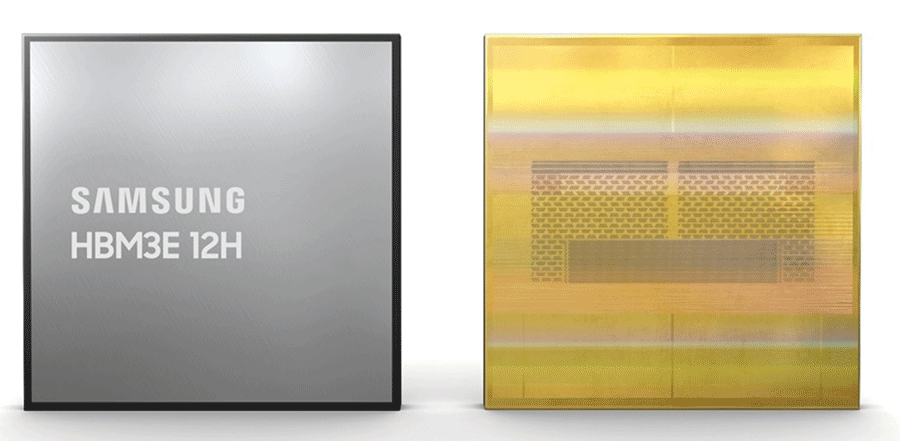

2024年2月28日

|技術分析(プロセス)

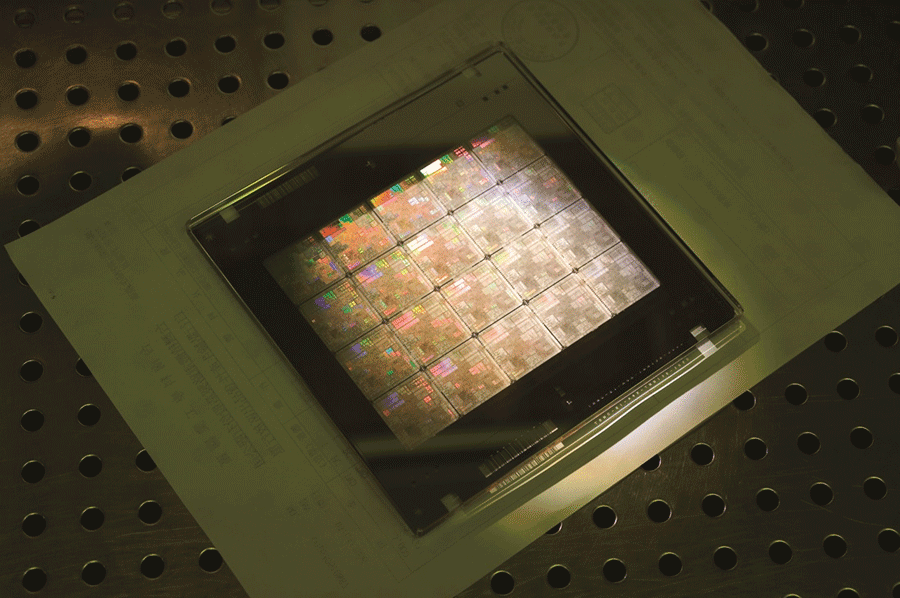

Micron、Samsungが3D-IC技術を使ったDRAMメモリであるHBM3Eを相次いで製品化した(図1)。HBMメモリは大容量のメモリを一度に大量に並列読み出しできるデバイスであり、AIチップやSoCプロセッサと一緒に使われる。SK hynixがこれまでHBM1や2、3のメモリ製品に力を入れてきたが、コストがかかるため他社はあまり力を入れてこなかった。

[→続きを読む]

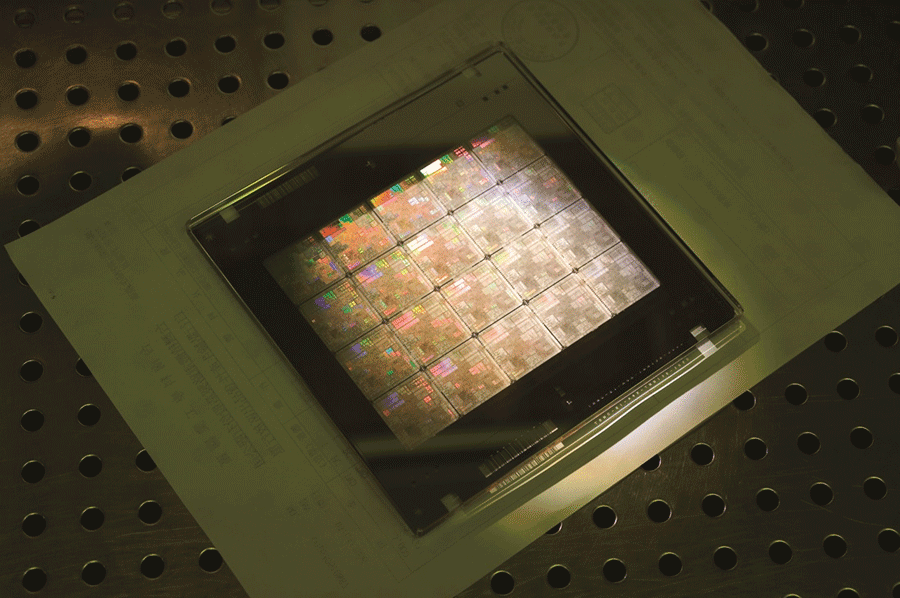

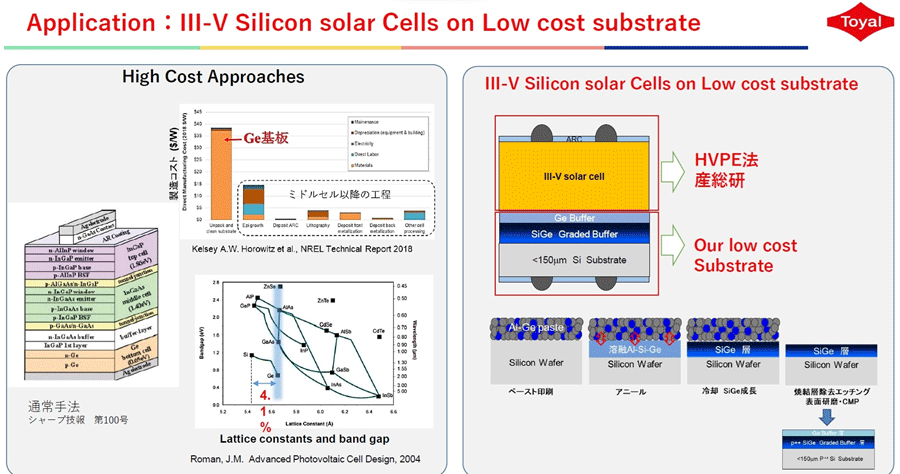

2024年2月16日

|技術分析(プロセス)

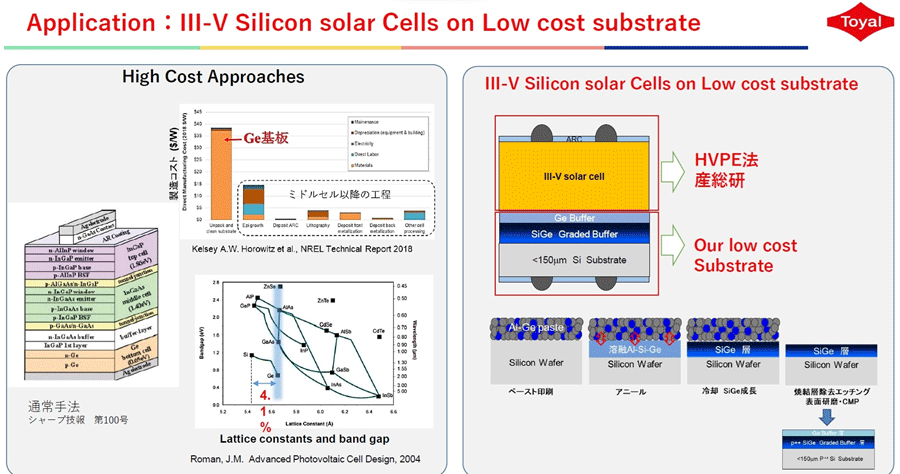

Si基板上にGe層を短時間で安価に作製する方法を東洋アルミニウムが開発した。Ge層の厚さを自由に変えられるだけではなく、ストイキオメトリ(化学組成)も制御できる。今のところ高価なGaAs系半導体向けの基板としての道を提案している。安価な太陽電池やSiフォトニクス、スピントロニクスなどの基板材料への応用を狙っている。

[→続きを読む]

2023年8月16日

|技術分析(プロセス)

フラッシュメモリの国際会議であるFlash Memory Summit 2023において、Most Innovative Flash Memory startup部門で最優秀賞を英国のスタートアップQuinas Technologyが受賞した(図1)。この新型メモリは量子力学的な井戸型ポテンシャルの共鳴トンネル現象を利用して電荷を出し入れする方式のデバイス。Quinasは英ランカスター大学の発明を事業化する企業。

[→続きを読む]

2023年7月 4日

|技術分析(プロセス)

TSMCは自動車向けの半導体チップに関してもADAS(先進ドライバー支援システム)や自動運転向けなどの演算主体のSoCプロセッサ向けに、そして最先端の3nmプロセスノードの技術「N3AE」を自動車およびHPC(High Performance Computing)向けに、2024年に提供する。さらに高周波無線技術でも6nmノードを導入する。同社ビジネス開発担当シニアVPのKevin Zhang氏(図1)が語った。

[→続きを読む]