NvidiaがASML、TSMC、Synopsysと組み、計算機リソで2nmノードを突破へ

プロセスノード2nm以降の次世代半導体チップ製造に欠かせない、計算機リソグラフィ(Computational Lithography)のエコシステムをTSMCとNvidia、ASML、Synopsysが設立した。3nmノードの実チップ上での最小寸法が13nm台までやってきて、波長13.5nmのEUVリソでもOPC(光近接効果補正)の導入が欠かせなくなってきた。計算機リソはそのための技術である。

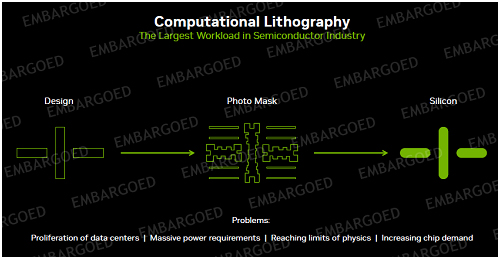

図1 計算機リソグラフィ(OPC)がEUVにも使われるようになってくる 出典:Nvidia

KrFやArFリソグラフィで使われるレーザー光の波長は、それぞれ248nm、193nmであるが、これらの波長よりも微細なパターンを加工するためOPC技術が使われていた。130nm、90nmプロセスでは日本が世界の先頭になってOPC技術を駆使、量産プロセスを確立してきた。OPC技術は、ArFリソグラフィでも使われてきたが、波長13.5nmのEUV時代になって再びOPC技術が使われる必要性が出てきた。実寸法のパターン線幅が波長と同じ13nm台まで微細になってきたからだ。

図1に示すように実際の設計パターンをそのまま使って露光しても光の屈折や反射、回折などの影響を受けて、シリコン上では設計パターンを忠実に再現できない。このため、最終的にシリコン上で求めるパターン形状になるように、マスクパターンや位相を修正するOPCや、光源の形状やマスクパターンを最適化して焦点深度などのプロセスマージンを改善する超解像技術などが必要になる。そこで、シリコン上の実形状から逆算してフォトマスクの形状パターンを計算で見つけておかなくてはならない。これが計算機リソグラフィと呼ばれる技術だ。

Nvidiaは、計算機リソ用のソフトウェアcuLithoと、GPUを大量に搭載した計算機Nvidia DGX H100を持っているが、この計算機リソでは500台のH100システムを使っている。これまでのCPUベースの計算では2週間かかっていた計算期間を一晩で済ませるようなスピードにできた。つまりフォトマスクの制作に週間かかっていた時間を一晩に短縮できるようになったという。逆に言えば、cuLithoを使う工場ではフォトマスク、すなわちチップ設計のテンプレートの生産性が3〜5倍向上し、計算に必要だった消費電力が1/9に削減できることになる。500台のH100システムは、4万台のCPUシステムに相当する、とNvidiaは見積もっている。

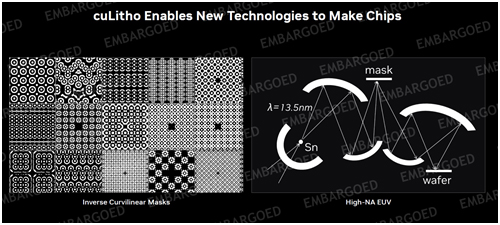

図2 高NAのEUVシステム 出典:Nvidia、ASML

このcuLithoのチームは、従来CPUで行っていた計算機リソをGPUで計算するようになったことで、さらなる微細化を進めることができると、TSMC社CEOのC.C. Wei氏は期待している。同様にリソグラフィ装置を提供するASML社のCEOであるPeter Wennink氏は、GPUのサポートを自社の計算機リソソフトウエア製品に組み込む計画であり、これによって高NAのEUV装置(図2)の時代が真実味を帯びてきた、と語っている。また、OPCソフトウェアを提供しているSynopsysのCEOであるAart de Geus氏は、「Nvidiaとコラボすることによって、SynopsysのOPCソフトウェアをcuLitho上で走らせられるため、これまで数週間かかっていた作業が数日でできるようになる」と期待している。

この技術は、Nvidia主催のGTC 2023で発表された。ラピダスは2nmプロセスから量産を始める方針であるから、この計算リソグラフィ技術は欠かせない。今回の4社によるコラボレーションを、Nvidia のニュースリリースではファウンデーションという言い方をしている(参考資料1)。ラピダスはこのファウンデーションに入れるのか、あるいは自ら計算リソのパートナーシップを作るのか、早くも新しい課題が出てきた。

参考資料

1. "NVIDIA, ASML, TSMC and Synopsys Set Foundation for Next-Generation Chip Manufacturing", Nvidia

(2023/03/21)