2024年7月18日

|技術分析(デバイス設計& FPD)

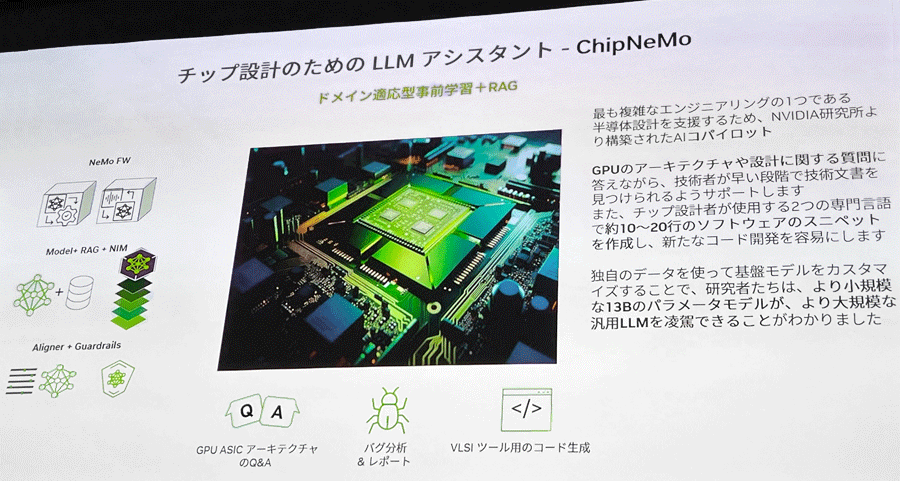

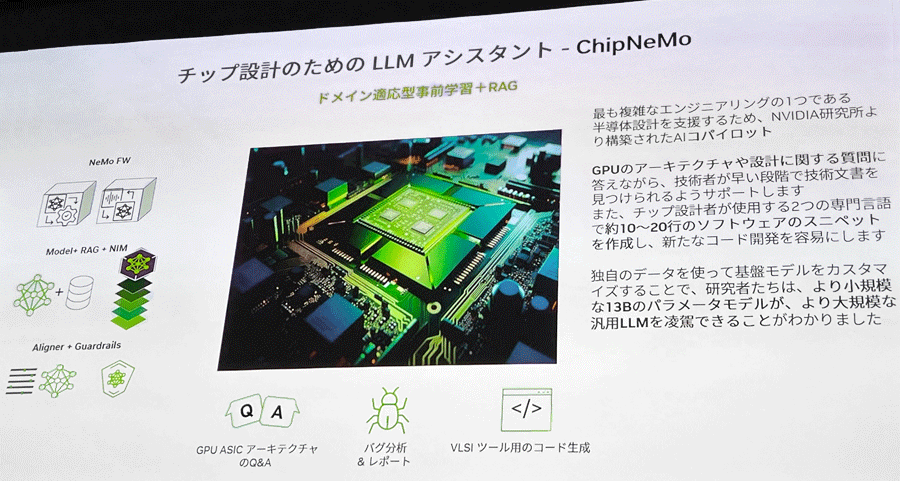

半導体売り上げで急成長しているNvidiaは、生成AIをはじめとするAIコンピューティングのGPUやソフトウエアをさまざまな応用ごとにAIソリューションを提供している。このほどLSI設計期間を短縮するため、チップ設計のための生成AIであるLLM(大規模言語モデル)アシスタントChipNeMo(図1)を開発、IC製品開発に使っていることを「NTTPC GPU Day 生成AI基盤の最前線」の講演で、明らかにした。

[→続きを読む]

2024年3月14日

|技術分析(デバイス設計& FPD)

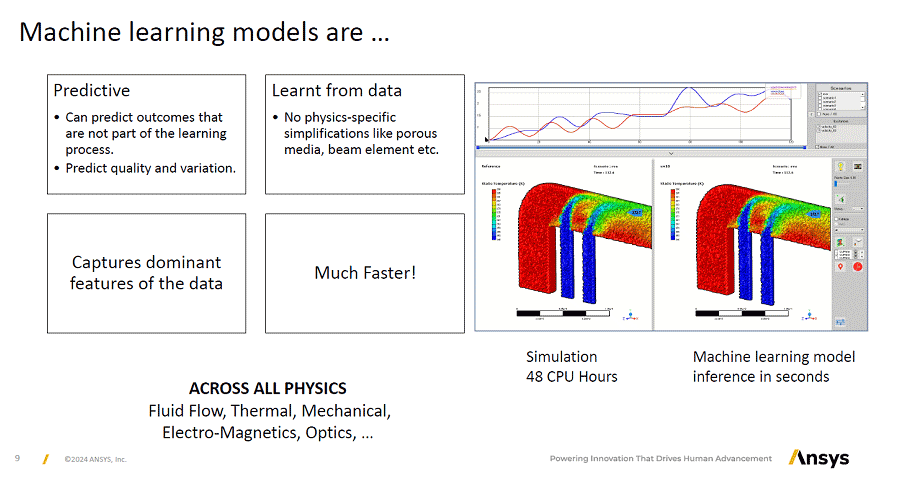

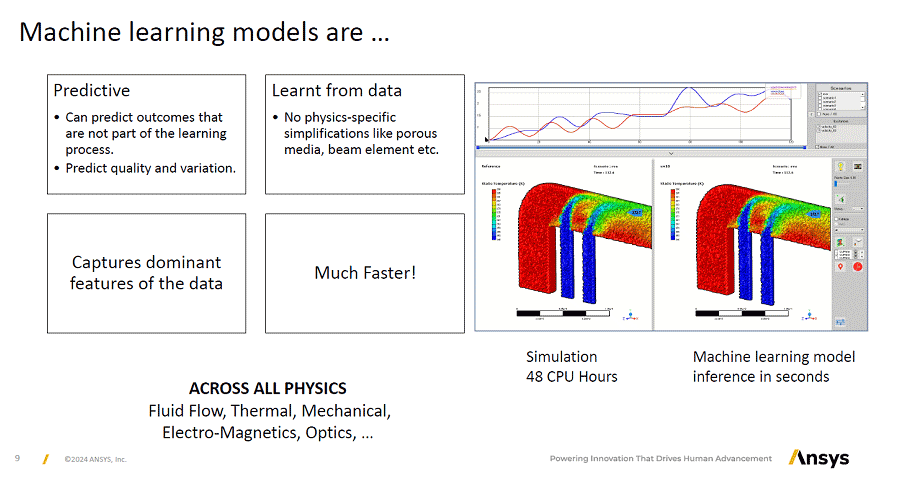

先端パッケージングで重要になる、流体解析や構造解析などのシミュレーション技術にAI/ML(機械学習)を利用すると、桁違いに結果が速く得られるAIシステム「SimAI」をシミュレーションベンダーのAnsysが開発した。AnsysはTSMCのエコシステムにもEDA3社と共に参加しており、これからの半導体パッケージには欠かせなくなりそうな存在だ。

[→続きを読む]

2021年11月10日

|技術分析(デバイス設計& FPD)

シーメンス EDAジャパンとArmの日本法人であるアームは、SoC開発と検証の環境を共同で提供すると発表した(図1)。Armの提供するCPUやGPUなどのIPコアを使って、SoCを設計してみたいエンジニアにとって安価に手軽に設計しやすくなる。まずはIoT用のSoCを開発するためのFPGA検証ボードを提供する。

[→続きを読む]

2021年4月23日

|技術分析(デバイス設計& FPD)

Siemens EDA(旧Mentor Graphics)は、LSI設計をハードウエアレベルで検証するエミュレータVeloce(ベローチェと発音)の次世代版の検証システムを発表した。今回の検証システムでは、ハードウエアマシンだけではなく、協調設計で必要な仮想プラットフォームでのソフトウエア検証ツールVeloce HYCONを含め4製品を用意した。

[→続きを読む]

2020年6月10日

|技術分析(デバイス設計& FPD)

Armが新時代のCPU、GPU、AIの各コア製品をリリースした。それぞれCortex-A78、Mali-G78、Ethos-E78という製品名だ。既存の最高のコア製品(A77、G77、E77)と比べ、電力効率で20%、性能で25%、単位面積当たりの推論性能で25%改善されている(図1)。性能や効率を上げることでイマーシブ(没入感)体験が増すという。カスタム化に対応するCPUコア、Cortex-Xも提供する。

[→続きを読む]

2019年11月14日

|技術分析(デバイス設計& FPD)

ベルギーにある半導体研究所のIMECが今週はじめ、東京でIMEC Technology Forumを開催した。ここ2〜3年、このフォーラムではIoTやAI関係の半導体応用の発表例が多かった。このため、CEOのLuc Van den Hove氏(図1)は、日本企業に対して装置・材料メーカーとシステム企業に参加を期待していた(参考資料1)。今年は違った。本流のムーアの法則で進展があった。

[→続きを読む]

2018年12月 6日

|技術分析(デバイス設計& FPD)

半導体のショット雑音が熱雑音と比べて、ほぼ3dB小さいことを、Analog Devices社のCTOオフィスのシミュレーション開発ディレクタのMike Engelhardt氏が見つけた。このことを同氏は東京・品川で開かれた「LTspiceユーザーの集い2018」で明らかにした。

[→続きを読む]

2018年7月 6日

|技術分析(デバイス設計& FPD)

ディープラーニングのニューラルネットワーク行列演算に超並列DSP回路を利用するIPがCEVAに続き、Flex Logixからも出てきた。エッジAIチップに集積するためのIPコアである。ニューラルネットの演算では8ビットや16ビットのように小さな積和演算(MAC)が適しているため、小さなDSPを大量に集積している。

[→続きを読む]

2018年1月 9日

|技術分析(デバイス設計& FPD)

フランスの半導体IPベンチャーのeVaderis社は、組み込みMRAMのIPを開発、それを集積したマイクロコントローラ(マイコン)をスロベニアのBeyond Semiconductorが設計、このほどテープアウトを終えた。IoTやウェアラブルのような低消費電力用途を狙う。

[→続きを読む]

2017年9月26日

|技術分析(デバイス設計& FPD)

英国のIPベンダー、Imagination Technologiesは、推論専用のAI向けIPコア「PowerVR 2NX NNA」のライセンス提供を開始した。クラウドを通すとレイテンシが遅くなるエッジやフォグなどの用途に使うだけではなく、モバイルにも使えるほど消費電力は少ないという。「セキュリティAIをエッジに持ってくる」と同社PowerVR 担当DirectorのChris Longstaff氏は強調する。

[→続きを読む]