ArmのIPコアとシーメンスEDAの検証プラットフォームを共同で提供

シーメンス EDAジャパンとArmの日本法人であるアームは、SoC開発と検証の環境を共同で提供すると発表した(図1)。Armの提供するCPUやGPUなどのIPコアを使って、SoCを設計してみたいエンジニアにとって安価に手軽に設計しやすくなる。まずはIoT用のSoCを開発するためのFPGA検証ボードを提供する。

図1 シーメンスEDAとアームがSoCの論理設計・検証で手を組む 出典:シーメンスEDAジャパン、アーム

これまで、LSI設計者がArmのIPコアを使って、すぐにSoCを始めることがなかなかできなかった。Armからライセンス提供してもらっても、期待していた性能や機能、消費電力などを実現できず、こんなはずではなかった、という不満を持った設計者がいても対応できなかった。このため、正式なライセンスを結ぶ前に、ちょっと使ってみよう、という仕掛けがAFA(Arm Flexible Access)である。実際に論理設計を行い、SoC用のRTLを得たとしても、論理が正しくプログラミングしてされているのか検証してみる必要がある。このため、アームはシーメンスと相談してきた。

旧メンターグラフィックスジャパンであるシーメンスEDAジャパンは、ハードウエアを検証するエミュレータVeloceに、開発検証ボードやソフトウエア検証ツールなども追加してきた。しかし、シーメンスEDAはIPを持っていないため、すぐに設計できる環境ではなかった。

今回、armのIPサービスAFAと、シーメンスのVeloce proFPGA検証プラットフォームを使ってSoCを設計検証する環境を提供する。アームがシーメンスに提案を持ちかけたのは、armの持つIPコアが他のEDAライバル2社とは違い、シーメンスのIPはarmのIPコアとは競合しないためだという。また、arm自身の自前の開発ボードは持っているが、餅は餅屋でシーメンスの方が検証技術はしっかりしているため、今回のコラボとなった。

AFAは、年会費を支払うだけで、SoC開発のツールやサポート・トレーニングサービスなどが受けられるため、量産に入る段階で初めて正式なロイヤリティ費用を見積もることができる。また問題が起きた時は、Armとも直接話をすることができる。アームが提供するCPU/GPUコアや周辺IP、物理IPは図2に示すとおりである。

図2 Armが提供するIP製品群 出典:アーム

シーメンスのVeloce proFPGAプロトタイピング開発ボードは、RTL出力までの論理設計を検証するもので、ネットリストや論理合成は扱わない。Armと組むことで、ArmのCPUコアやGPUコア、その他のIPなどを搭載し、SoCを組む前に論理設計が正しく書かれ、論理動作できるかどうかを検証する。

一般に、SoCを設計してみる場合には、いきなりシリコンに実装するのではなく、最初にFPGAで論理を組んで、その論理が正しいかどうかを検証しておく必要がある。正しければ、ネットリストあるいは論理合成などで回路図に落とし、最終的に配置配線・レイアウトを済ませ、OPCなどの補正を加えてフォトマスクデータとして出力する。

開発ボードに使用するFPGAそのものがXilinxのZynq製品のようにCPU内蔵のFPGAでも、純粋のFPGAでどちらでも対応可能だとしている。また、Xilinxだけではなく、Intel(旧Altera)のFPGAも搭載できる。

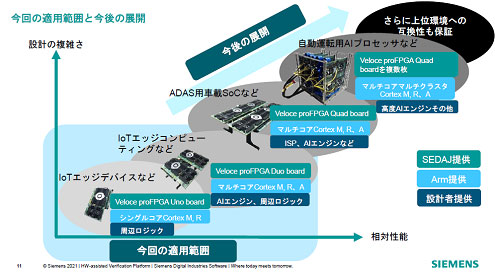

またシーメンスの提供するVeloce proFPGAではFPGAが1個、2個、4個を搭載したマザーボードを提供する。ユーザーの望むSoCの規模によって選択する。最大4個FPGAを搭載したボードを最大5枚まで収容できるモジュラー方式をとっており、最大8億ゲートまでの設計規模のSoCまで対応できる。

図3 今後はさらに規模の大きなSoCの設計検証にも対応していく 出典:シーメンスEDAジャパン

今回はIoT向けのSoCを狙ったものだが、今後、さらに規模の大きいADAS用のSoCや自動運転向けのSoCなど規模と性能が高い製品のサポートへと拡大していく(図3)。今回の提携は日本法人同士のコラボだが、両本社とも両社のコラボを世界展開する場合の参考にしようと今後の経緯を注目しているという。