Intel、2nmプロセスのPC用Panther Lakeの詳細を公表

Intelはパソコン向けにIntel 18Aプロセスを使ったSoC「Panther Lake」を発表していたが、このほどその詳細を明らかにした(図1)。最近のCPUはCPUだけではなくGPU(グラフィックプロセッサ)やNPU(ニューラルプロセッサ)などを集積しており、CPUと呼ぶにはふさわしくないため、SoCと呼ぶ。Panther Lakeは3種類の製品シリーズがあるが、全て同じパッケージ、同じピン配置を採っている。

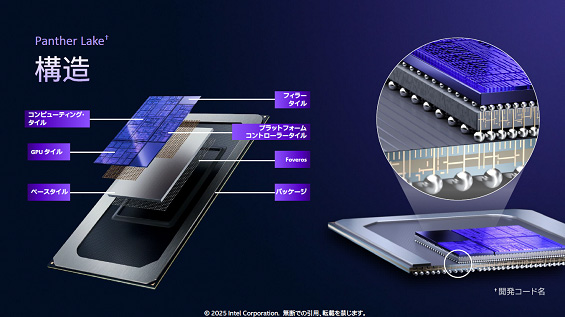

図1 Panther Lake 構造 タイル(チップレット)をふんだんに使いながらシリコンインターポーザとの接続には3D構造のFoveros技術を使う 出典:Intel

Panther Lakeの発表時には、量産を開始したという表現を使っていたが(参考資料1)、本格的な量産をこの第4四半期に立ち上げることを目標としていた。数量はまだ多くないようだが、サーバー用の「Clearwater Forest」もほぼ同時に立ち上げた。その量産開始はPanther Lakeの方が早く、パソコン用のSoCの量産状況(歩留まりなど)を見ながらサーバー用のSoCを量産化していくと見られる。共に2nm相当のIntel 18Aプロセスを使い、アリゾナ工場とオレゴン工場の2拠点で生産するという。

Panther Lakeは、CPUを8コアと16コア、16コアでGPUを強化した12Xeコアの3種類あり、それぞれチップ面積が違うものの、3つとも同じパッケージ、同じピン配置で作製する(図2)。このため、各チップにはフィラータイルと呼ぶ空きスペースができる。ここに独自のハードウェアを入れることも可能だ。

図2 3種類とも同一パッケージ、同一ピン配置のパッケージを使う 出典:Intel

3種類の基本チップはチップサイズを変えながらもCPUやGPUなどのIPコア揃えて配置しており、柔軟性・拡張性を重視している。そのための空きスペースに顧客に応じて何か機能を置いても良い設計になっている。シリコンインターポーザの上にCPUコアやGPUコアなどをタイル(チップレット)として、まるでレゴブロックのように配置しているが。GPUはコンピューティングタイルとは分離しているが、これはチップによってGPUコアを増やせるように柔軟性を持たせている。ただし、CPUタイル、GPUタイルともメモリコヒーレンシー(異なるCPUからもGPUからも同じメモリをアクセスできること)を保つためのシステムも集積している。

また、CPUコアには、性能を優先したPコアと呼ばれる「Cougar Cove」とEコアと呼ばれる電力効率の良い「Darkmont」の2種類をIntel 18プロセスの最適化したCPUコアとして設計した。ウェブブラウザなどで素早く検索するような場合にはPコアをフルに使い、ブラウザを読むだけで次々と展開しない場合にはEコアを主体的に動作させることによって、システム全体の消費電力を下げる。

Intel 18プロセスではGAA(Gate All Around)トランジスタ(IntelはRibonトランジスタと呼ぶ)と、裏面電源供給技術を使っている。ただし、ウェーハの張り合わせ技術ではなく、PMICチップレットとして裏面から電源を供給しているようだ。

チップ内のCPUもGPUもNPUも全て現世代のチップ(Lunar LakeやArrow Lake)と比べて優れた性能と電力効率を示している(図3)。例えば、CPUのマルチスレッド性能は現世代の両チップよりも同じ消費電力では50%以上性能がアップし、GPUの性能も両チップよりも50%以上向上している。またNPUもLunar Lakeと比べ、面積当たりのTOPS性能は40%以上増加している。

図3 Panther Lakeの主要な性能 出典:Intel

特にGPU性能を上げた16コアで12Xeコアのチップは、GPUを12コア使いながら各コアにレイトレーシング技術を搭載し、写真か絵か判別できないほどの写実的な絵を描ける機能もある。3種類全てNPUを搭載しており、その性能もAI PCの規格に入る性能だとしている。

参考資料

1. 「Intelが米国で初めて2nmプロセスのSoCを生産開始」、セミコンポータル、(2025/10/14)