AIを進化させる半導体新技術のオンパレード、2026 VLSI Symposium

2026年6月14〜18日、ハワイで開催される2026 Symposium on VLSI Technology and Circuits(通称VLSI Symposium)のテーマは「VLSIのイノベーションを通してAI開発を進化させよう(Advancing the AI Frontier through VLSI Innovation)」であり、4つの基調講演は全てAI関係となっている。OpenAI、TSMC、Micron、東京エレクトロンから4名の専門家が講演する。

基調講演のタイトルにはすべてAIという言葉がついている。各タイトルは次の通りで、主催者による簡単な日本語を添えている;

・OpenAIのRichard Ho氏「Building the Engine of AI: From Foundational VLSI Technologies to System-Scale Impact」(生成AIを支える半導体設計)

・TSMCのL. C. Lu氏「Advanced Package for Next-Generation AI System Scaling」(先端パッケージ技術)

・Micron TechnologyのNirmal Ramaswamy氏「Intelligence Accelerated: Memory Innovations to Power the AI Era」(DRAM技術革新)

・東京エレクトロンの三田野好伸氏「Meeting AI Demand Through Equipment Innovation and AI-Driven Manufacturing: Progress and Challenges」(装置革新とスマート製造)

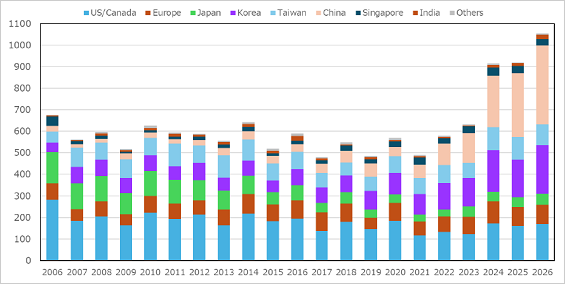

図1 地域別投稿数の推移(Circuits/Technology合計) 出典:VLSIシンポジウム委員会

一般に基調講演はその時々のトピックスを表すことが多い。現在、半導体技術はAIがドライブしていることを示唆していると言えるだろう。特に生成AIからの半導体技術への要求が高まっており、それは投稿論文数の推移(図1)からもわかる。生成AIが普及する前の2016年から2023年までの投稿数は400件〜700件の範囲に収まっていたが、AIが普及し始めた2024/25年には900件以上、そして2026年は1041件と1000件超えを達成している。採択数は若干増える程度なので、採択率は23%、とこれまでの33%前後から減少している。

採択された論文は、デバイス・プロセスのTechnologyと、回路のCircuitsで分けられており、それぞれ101件と138件となっている。Technology部門の国別の採択数は、多い順に韓国23件、北米22件、日本14件、欧州と中国が13件、台湾10件、シンガポール6件となっている。同様にCircuits部門では、韓国37件、北米33件、欧州と中国が21件、日本13件、マカオ7件、台湾6件である。

VLSI Symposiumのプログラム委員会が注目した、いくつかの講演を紹介しよう。

Technology部門では、2nmプロセスのGAA(ゲートオールアラウンド)トランジスタを基本とし、それを積層して縦構造にするCFET(3D Stacked FET)の開発が盛んだが、Samsungが3層積層のナノシートチャンネルの構造を持つCFETを作製した。これまでは2層のCFETが多かった。さらにゲートピッチが42nmとシュリンクしている。またIntelは2層のCFET構造でインバータ動作を実証している。性能を上げるため下層のnMOSに(100)面方位、上層のpMOSに(110)面を用いて最適化している。

メモリでは、3D-NANDフラッシュのようにDRAMセルを3次元に積層して記憶容量を高める技術が注目されているが、Samsungは16層のVS-DRAMと称して、GAAトランジスタを用い、水平にストレージキャパシタを採用した16層垂直積層(VS)DRAMを試作している。NANDフラッシュでは、キオクシアとSanDiskが共同で、2枚のウェーハ同士の直接接合によるマルチ積層セルアレイCMOS構造で、QLC(4ビット/セル)動作を確認した。

回路部門では、AIチップの性能と消費電力を改善する手法の一つとしてDCiM(Digital Compute in Memory)が注目されているが、TSMCは精度を4ビット、8ビットなどと変えながら複数のMAC(積和)演算回路を構成するDCiMコンパイラを開発し、234.4TOPS/Wと511.9TOPS/mm2の高性能な演算を実現した。またMediaTekは、ウェアラブル機器で常時推論できるNPU(ニューラルプロセッサ)をDCiMベースで試作、トークン当たりの消費エネルギーが0.06〜134.36μJという低さを実現した。

Nvidiaからは、3次元積層フォトニクス回路上で差動TIA(トランスインピーダンスアンプ)を用いて受信感度を-17.3dBmに高めた、32Gb/sの光受信機を実現している。Nvidiaは、AI GPU基板から基板への光ファイバ送受信機の感度向上で光配線技術に磨きをかけている。

ワイヤレスでは6G通信を目指す150GHz帯で144GbpsのMIMO(Multiple Input Multiple Output)フェイズドアレイトランシーバを東京科学大学から発表される。デュアルの偏波MIMOをλ/4(波長の1/4)ピッチで高密度集積することで小型のトランシーバを実現している。将来の6Gスマホに採用される可能性を秘めている。