Intel最大のマレーシア後工程工場のクリーンルームに入ってきた!

マレーシアにあるIntel最大の後工程工場のクリーンルームにバニースーツ(無塵衣)を着て入って見学してきた。無塵衣着用のレベルは、工程によって前工程と同じ最も厳しい完全装備の無塵衣着用レベルからガウン着用まで工程ごとに細かくわかれていた。今回は、シリコンウェーハをダイに切り出しダイ状態でテストしテープに封入するまでのアセンブリ工程の前段階を写真で紹介しよう。

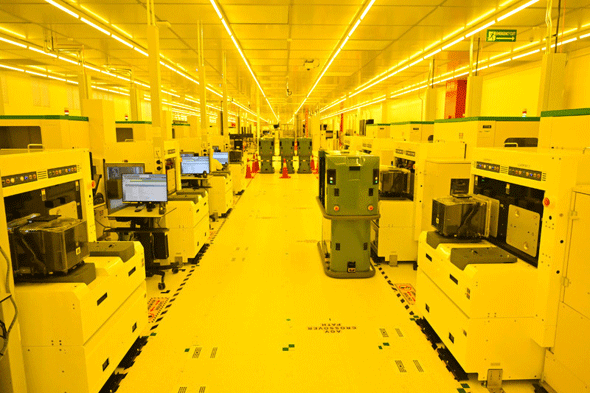

米国やアイルランド、イスラエルの前工程工場から送られてきたシリコンウェーハからダイに切り出しトレイに並べてSingulated Die Sort Tester(SDX)と呼ばれるソータで合否を選別し、合格品だけテープに封入し映画フィルムのようにリールに巻きとるまでの工程を、ペナン島の対岸の本土のクリム・ハイテク工業団地(マレーシア・ケダ州クリム)にあるIntelマレーシア工場クリム・キャンパスで行っている。社内でKMDSDP(KuliM Die Sort Die Prep)とよばれる製造施設である。なお、写真撮影や録音機材やノートの持ち込みは禁止されたため、写真は著者撮影と表記されたもの以外はIntelから提供されたものである。

(1)ダイ・プリパレーション

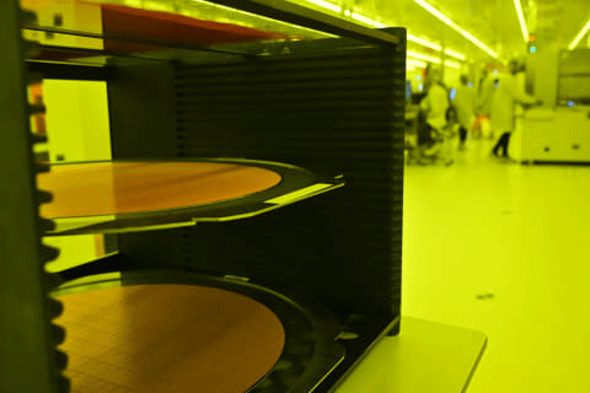

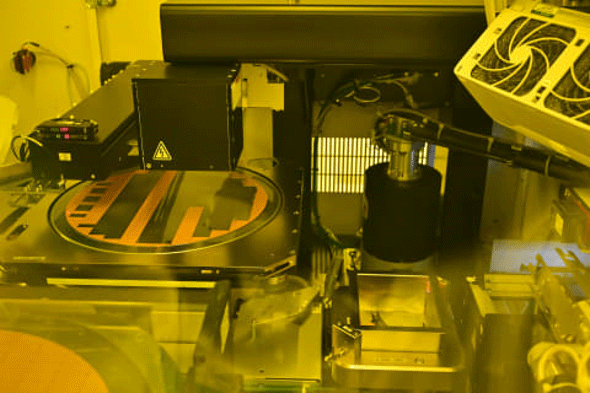

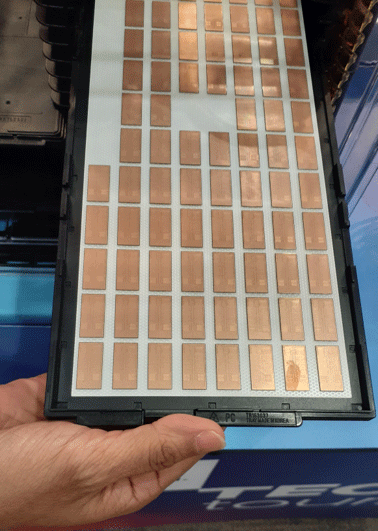

KMDSDPに納品されたウェーハ(図1、2)は、まず裏面研磨で薄板化し、ダイシングテープで接着保持される。このような状態のシリコンウェーハは、(図3)によりダイにカットされ(ダイシングともスクライビングとも呼ばれる)(図4)、ロボットによりダイを収容するトレイに自動的に移載されて(図5、6)、次のソート(合否判定選別)工程に移送される。

図1 ダイシングテープで接着保持されたシリコンウェーハ 出典:Intel

図2 ダイシング前のウェーハの最終目視検査 出典:Intel

図3 ずらりと並んだレーザーを用いたダイシングマシン群 出典:Intel

図4 ロボットがダイシングの済んだウェーハからダイを1個ずつ取り出して専用トレイに収納 出典:Intel

図5 ダイを収納する専用トレイ、韓国製の文字が見える。トレイは黒いFOUPボックスに収納されて搬送される 出典:クリーンルーム外で展示用トレイを著者撮影

図6 取り出したダイをトレイに移載する装置群 出典:Intel

(2)ダイソート

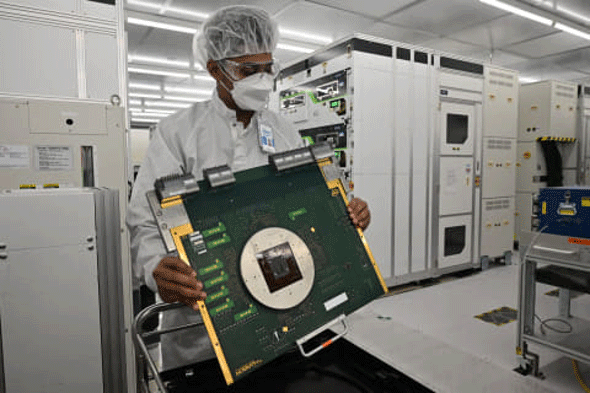

ダイの電気的測定を行うソート装置(Singulated Die Sort Tester、SDX)(図7)は4段5列の配置された20台のテストセル(図8)で構成され20個のダイを同時にテストできるようになっており、ここで不良品や低性能品を選別する。テストセルにはテスト用基板が収納されており、テスト対象のCPU/GPUごとに基板を簡単に差し替えられるように基板に取っ手がついている。なお、このテスト用基板(図9)やテストセルは、社内(マレーシア工場SIMS部門)で内製され、社外への情報漏洩を防いでいる。

図7 (上)ダイテストシステム(ダイソータ)側面、(下)ダイテストシステムの前面 出典:Intel

図8 ソータシステムのテストセル 出典:Intel

図9 20台のテストセルそれぞれに収納されている自家製テスト用基板 出典:Intel

(3)トレイからキャリアテープへ

ダイソートで合格したダイのみキャリアテープへ封入されて(図10、11)、ペナン島にあるアッセンブリ工程へ送られる。

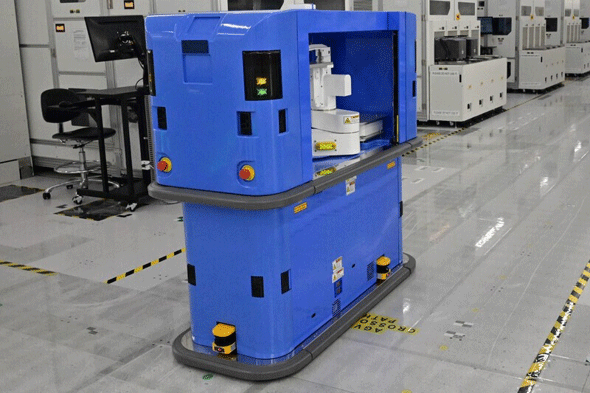

図10 ソータとキャリアテープ封入工程間を走行する自動搬送車(AGV) 出典:Intel

図11 合格したダイは判定グレードごとにキャリアテープに封入され、映画のフィルムリールのような形状のリールに巻き取られてペナンキャンパスのアセンブリ最終テスト工程へ送られる。 出典:Intel

次回は、ペナンキャンパスのMeteor Lakeアッセンブル + 最終テスト工程を紹介しよう。