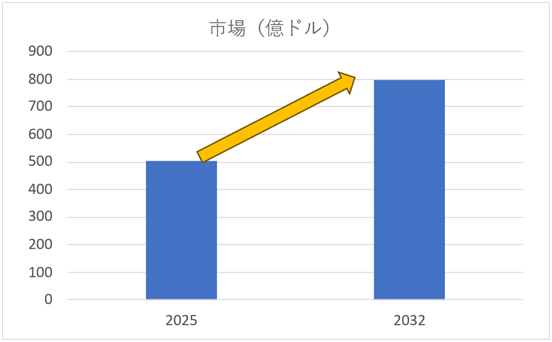

先端パッケージの市場規模、2032年に約800億ドルへ

先端半導体パッケージ市場予測が発表され、今後8年間の平均年成長率(CAGR)が6.8%になりそうだ。先端パッケージング技術は、TSMCのCoWoS(Chip on Wafer on Substrate)やFOWLP(Fan-Out Wafer Level Package)、チップレットなど従来の組立後工程とは違い、これまで以上の高集積を実現する中工程の技術である。

図1 先端パッケージの市場規模 出典:Coherent Market Insightsの数字をセミコンポータルがグラフ化

先端パッケージの市場予測を発表したのは、米市場調査会社Coherent Market Insights社。同社の見積もりによると、2025年の先端パッケージ市場は503.8億ドルだが、これが2032年には798.5億ドルになると予想する。これ以上の高速・低消費電力・小型化が必要な電子機器からの需要が高まっているからだ。特に、HPC(High Performance Computing)やIoT(Internet of Things)、5G、AIなどの新市場には2.5D、3Dパッケージングが強く求められているといえそうだ。

現在の先端パッケージ市場では、最大のパッケージはFOWLPで、58.6%を占めている。地域別で、最大の市場はアジア太平洋地区であり市場全体の52.3%を占めているが、米国は、最も急成長しており、市場全体の29.3%を占めている。

先端パッケージは、CPUやGPU、メモリなどさまざまな異なるチップを利用するヘテロ集積に向いた技術である。特に自動車、医療機器、産業機器などが急速に成長しており、これらの産業が先端パッケージを求めているとしている。

今後は、チップを大きなパネルに並べて実装するPLP(Panel Level Packaging)や、1枚のウェーハに大きなAIチップを1個形成してそのまま実装するSoW(System on Wafer)のような新しいパッケージング技術が成長していくと見られ、先端パッケージが大きく成長すると見ている。