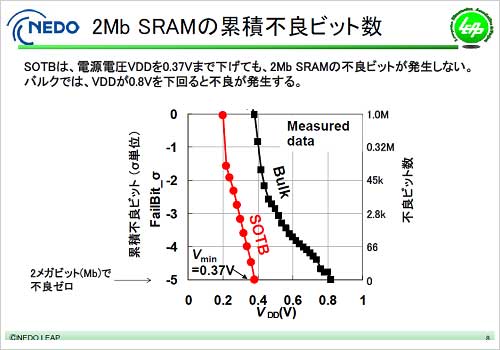

LEAP°ĘŇŇłĽŇŇįĶ0.37V§«∆į§Į2M•”•√•»SRAM§ÚĽÓļÓ°ĘŃī•”•√•»∆įļÓ≥ő«ß

NEDO° Ņ∑•®•Õ•Ž•ģ°ľé•Ľļ∂»ĶĽĹ—ŃŪĻÁ≥ę»ĮĶ°ĻĹ°ň§»LEAP° ń∂ń„ŇŇįĶ•«•–•§•ĻĶĽĹ—ł¶ĶśŃ»ĻÁ°ň§Ō°Ę0.37V§»§§§¶ń„§§ŇŇįĶ§«∆įļÓ§Ļ§ŽSOI§őMOSFET§Ú≥ę»Į(Ņř1)°Ę2M•”•√•»§őSRAM§ÚĽÓļÓ§∑°Ę§Ĺ§ő∆įļÓ§Ú≥ő«ß§∑§Ņ°£§≥§őņģ≤Ő§Ú6∑Ó11∆Ł§ę§ťĶĢŇ‘§«≥ęļҧĶ§ž§∆§§§Ž2013 IEEE Symposium on VLSI Technology and Circuits° ńŐĺőVLSI Symposium°ň§«»Į…ŧ∑§Ņ°£

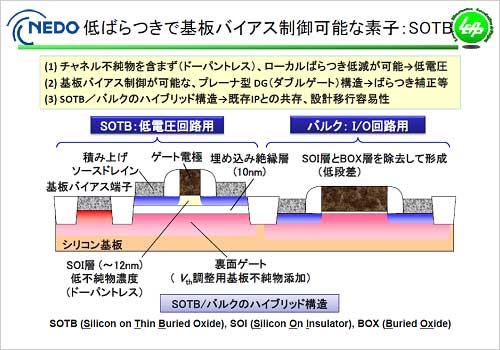

Ņř1°°LEAP§őńůį∆§Ļ§ŽSOTB•»•ť•ů•ł•Ļ•ŅĻŬ§°°Ĺ–ŇĶ°ßLEAP

»ĺ∆≥¬őLSI§Ú»ýļŔ≤ŧ∑§∆§§§Į§»°Ę•≤°ľ•»§∑§≠§§ŇŇįĶ§ő•–•ť§ń§≠§Ō¬Á§≠§Į§ §Ž°£√Ľ•Ń•„•ů•Õ•Žłķ≤Ő§»§§§¶§Ť§Í§Ō°Ę…‘Ĺ„ ™ł∂Ľ“§Ĺ§ő§‚§ő§őŅۧ¨ŅŰĹĹnmĽÕ ż§»§§§¶»ýļŔ§ •»•ť•ů•ł•Ļ•ŅőőįŤ∆‚§ň§Ť§√§∆•–•ť§ń§§§∆§Į§Ž§Ņ§Š§ņ°£ŇŇłĽŇŇįĶ§ő•ř°ľ•ł•ů§ÚĻ≠§Į§»§Ž§≥§»§¨§«§≠§ §§§Ņ§Š°ĘŇŇłĽŇŇįĶ§Ú¬Á§≠§Į≤ľ§≤§Ž§≥§»§¨§«§≠§ §§°£•≤°ľ•»ŇŇįĶ§ő•–•ť§ń§≠§¨ĺģ§Ķ§Ī§ž§–°Ę∆įļÓ•ř°ľ•ł•ů§Úłļ§ť§Ľ§Ž§Ņ§Š°ĘŇŇłĽ§Ú≤ľ§≤§∆§‚Ńī•»•ť•ů•ł•Ļ•Ņ§¨∆įļÓ§Ļ§Ž°£

•≤°ľ•»§∑§≠§§ŇŇįĶ§Ú∑Ť§Š§Ž•—•ť•Š°ľ•Ņ§őįž§ń§¨…‘Ĺ„ ™ł∂Ľ“§«§Ę§Ž°£§Ĺ§‚§Ĺ§‚•∑•Í•≥•ůł∂Ľ“§¨1cm3ŇŲ§Ņ§Í10§ő24即ń§Ę§Ž¬őņ—√ś§ňīř§ř§ž§Ž…‘Ĺ„ ™ł∂Ľ“(•…• °ľ§š•Ę•Į•Ľ•◊•Ņ)§¨10§ő17即ńńÝŇŔ§Ę§ž§–°Ę•»•ť•ů•ł•Ļ•Ņ§őŇŇőģ§Ō•™•ů§Ļ§Ž°£§Ļ§ §Ô§Ń1000ňŁ ¨§ő1§ő…‘Ĺ„ ™§«∆įļÓ§Ļ§Ž§ő§¨»ĺ∆≥¬őMOS•»•ť•ů•ł•Ļ•Ņ§«§Ę§Ž°£

§»§≥§Ū§¨°Ę•»•ť•ů•ł•Ļ•ŅőőįŤ§¨20nmĽÕ ż§»§ §√§∆§Į§Ž§»°Ę§Ĺ§ő√ś§ň∆Ģ§Í§¶§Ž•∑•Í•≥•ůł∂Ľ“§őŅۧŌ°Ę20nm°Ŗ20nm°Š4°Ŗ10§ő-12即ń/cm2§»§ §Ž°£§Ō§ §Ō§ņÕūňŧ ĶńŌņ§Ú§≥§ž§ę§ť§∑§∆§§§Į§¨°Ę§‚§∑•…• °ľ«ĽŇŔ§¨10§ő17即ń/cm3§ņ§»≤ĺńͧĻ§Ž§»°Ę√ĪįŐ…ĹŐŐ匧ň§Ō10§ő11即ń/cm2§ő•…• °ľ§¨łĹ§ž§Ž§»ĻÕ§®§ť§ž§Ž°£•∑•Í•≥•ůł∂Ľ“§Ō√ĪįŐ…ĹŐŐ匧ň10§ő16即ń§Ę§Ž§»§∑§∆°Ę20nm°Ŗ20nm∆‚§ň§Ō•∑•Í•≥•ůł∂Ľ“§Ō4°Ŗ10§ő4即ń§Ę§Ž§¨°Ę•…• °ľł∂Ľ“§Ō0.4łń§∑§ę§ §§°£§ń§ř§Í°Ę20nm°Ŗ20nm§ő√ś§ň§Ō1łń§Ę§Ž§ę0łń§ę§»§§§¶ĶńŌņ§ň§ §Ž°£§≥§ž§«§Ō°Ę•…• °ľ§¨1łń§Ę§Ž•»•ť•ů•ł•Ļ•Ņ§»0łń§ő•»•ť•ů•ł•Ļ•Ņ§ň ¨§ę§ž§Ž§≥§»§ň§ §√§∆§∑§ř§¶°£§≥§¶§ §Ž§»•»•ť•ů•ł•Ļ•Ņ§ň§Ť§√§∆∂űň≥Ńō§őńĻ§Ķ§Ō¬Á§≠§Įįا §Í°Ę•≤°ľ•»§∑§≠§§ŇŇįĶ§Ō¬Á§≠§Į§–§ť§ń§Į§≥§»§ň§ §Ž°£

§ņ§√§Ņ§ť§§§√§Ĺ§ő§≥§»°Ę…‘Ĺ„ ™§Ú∂ňőŌłļ§ť§∑°Ę∂űň≥Ńō§őńīņį§ÚMOSFET§őīū»ń•–•§•Ę•Ļ§«Ļ‘§™§¶°Ę§»§§§¶ĻÕ§®§ň√£§Ļ§Ž°£§≥§ž§¨LEAP§őĻÕ§®§Ž°Ę§∑§≠§§ŇŇįĶ§ő•–•ť§ń§≠§Úłļ§ť§Ļīūň‹ł∂Õż§«§Ę§Ž°£§Ņ§ņ§∑°Ę ∆Ļ٧ő»ĺ∆≥¬őIP•Ŕ•ů•Ń•„°ľSuVoltaľ“§‚∆ĪÕÕ§ ĻÕ§®§«°Ę•≤°ľ•»§∑§≠§§ŇŇįĶVth§ő•–•ť§ń§≠§Úłļ§ť§ĻĶĽĹ—§Ú≥ę»Į§∑°Ę…ŔĽőńŐ•Ľ•Ŗ•≥•ů•ņ•Į•Ņ°ľ§ň•ť•§•Ľ•ů•Ļ∂°ÕŅ§∑§∆§§§Ž°£

ļ£≤ů°ĘLEAP§Ō°ĘŃį≤ů° Ľ≤ĻÕĽŮőŃ1°Ę2°ň§»∆ĪÕÕ°ĘSOI° silicon on insulator°ňĻŬ§§ň§∑§∆īū»ń•–•§•Ę•Ļ§Ú§ę§Ī§ť§ž§Ž§Ť§¶§ň§∑§Ņ°£MOS•»•ť•ů•ł•Ļ•Ņ§ŌłŁ§Ķ10nm§ő«Ų§§ňš§ŠĻĢ§ŖĽņ≤Ĺňž° BOX°ň匧ň∑Ńņģ§∑°ĘSOIņšĪÔňž§őīū»ń¬¶§ę§ť•–•§•Ę•Ļ§Ú§ę§Ī§ť§ž§Ž§Ť§¶§ň§∑§Ņ° Ņř1°ň°£§≥§őĻŬ§§őSOI•»•ť•ů•ł•Ļ•Ņ§ÚLEAP§Ō°ĘSOTB° silicon on thin buried oxide°ň•»•ť•ů•ł•Ļ•Ņ§»ł∆§ů§«§§§Ž°£

Ņř2°°ŇŇłĽŇŇįĶ0.37V§«2M•”•√•»SRAM§¨Ńī•”•√•»∆įļÓ°°Ĺ–ŇĶ°ßLEAP

§≥§őSOTB•»•ť•ů•ł•Ļ•Ņ§ÚĽ»§√§∆ĽÓļÓ§∑§Ņ2M•”•√•»§őSRAM§«ŇŇłĽŇŇįĶ§Ú§…§≥§ř§«≤ľ§≤§ť§ž§Ž§ę§Úńī§Ŕ§Ņ°£SRAM•Ľ•Ž§Ō6łń§ő•»•ť•ů•ł•Ļ•Ņ§ę§ťņģ§Íő©§ń•’•Í•√•◊•’•Ū•√•◊§ §ő§«°Ę•»•ť•ů•ł•Ļ•Ņ§¨§–§ť§ń§Į§»•Š•‚•Í§Ō∆įļÓ§∑§ §Į§ §Ž°£ľ¬ł≥§«§Ō°Ę∆įļÓŇŇįĶ§Ú1V§ę§ť≤ľ§≤§∆§§§≠°Ę…‘ő…•”•√•»ŅۧÚŅۧ®§Ņ°£§≥§ő∑Ž≤Ő°ĘŇŇłĽŇŇįĶ§Ú0.37V§ř§«≤ľ§≤§∆§‚SRAM§ŌŃī•”•√•»∆įļÓ§∑§Ņ°£§Ņ§ņ§∑°Ę§Ĺ§žį ĺŚ≤ľ§≤§Ž§»•”•√•»…‘ő…§Úņł§ł§Ž°£∆ĪÕÕ§ň§∑§∆ĹĺÕŤ§őCMOSĻŬ§§»∆Ī§ł•–•Ž•Į§«2M•”•√•»§őSRAM§ÚļÓ§Ž§»°Ę0.8Vį ≤ľ§«§Ō…‘ő…•”•√•»§¨Ĺ–ĽŌ§Š§Ņ°£

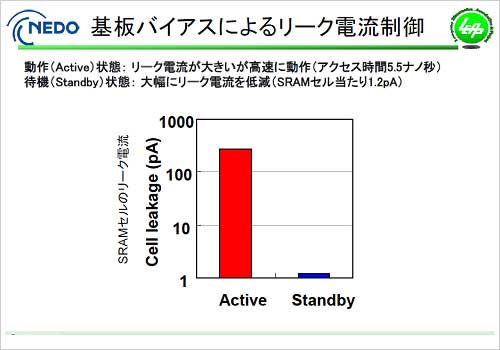

īū»ń•–•§•Ę•Ļ§Ō°Ę•≤°ľ•»§∑§≠§§ŇŇįĶ§Úńīņį§«§≠§Ž§ņ§Ī§«§Ō§ §Į°Ę¬‘Ķ°ĽĢ§ő•Í°ľ•ĮŇŇőģ§ÚÕř§®§ť§ž§Ž§»§§§¶łķ≤Ő§‚§Ę§Ž(Ņř3)°£•≤°ľ•»ŇŇįĶį ≤ľ§ő•Ĺ°ľ•Ļ-•…•ž•§•ůŇŇőģ°Ę§Ļ§ §Ô§Ń•Ķ•÷•Ļ•ž•√•∑•Á•Ž•…ŇŇőģ§ő•≤°ľ•»ŇŇįĶ§ň¬–§Ļ§Ž∑Ļ§≠§Ú•∑•„°ľ•◊§ň§Ļ§Ž§»§§§¶ŐÚ≥š§¨īū»ń•–•§•Ę•Ļ§ň§Ō§Ę§Ž°£§≥§ő§Ņ§Š°ĘĻ‚¬ģ∆įļÓĽĢ§»¬‘Ķ°ĽĢ§«īū»ń•–•§•Ę•Ļ§ÚļŔ§ę§Įńīņį§Ļ§ž§–°ĘLSIŃī¬ő§»§∑§∆§őĺ√»ŮŇŇőģ§Ú≤ľ§≤§Ž§≥§»§¨§«§≠§Ž°£

Ņř3°°īū»ń•–•§•Ę•Ļ§«•Í°ľ•ĮŇŇőģ§Ú≤ľ§≤§Ž°°Ĺ–ŇĶ°ßLEAP

§≥§őSOTB•»•ť•ů•ł•Ļ•Ņ§Ō°Ę•◊•ž°ľ• ĻŬ§§ő§ř§ř»ýļŔ≤ŧ«§≠§Ž§»§§§¶•Š•Í•√•»§¨§Ę§Ž°£īū»ń•–•§•Ę•Ļ§«•Ķ•÷•Ļ•ž•√•∑•Á•Ž•…ŇŇőģ§Úłļ§ť§Ľ§Ž§ę§ť§ņ°£•–•Ž•ĮCMOS §ņ§»°Ę10nm¬ś§ō§»»ýļŔ≤ŧĻ§Ž§»°Ę £Ľ®§ ĻŬ§§őFINFET§»§§§√§Ņ3ľ°łĶĻŬ§§¨∑Á§ę§Ľ§ §§°£STMicroelectronics§¨FD° fully depletion°ň∑Ņ§őSOI•»•ť•ů•ł•Ļ•Ņ§«§ŌFINFET§ŌÕ◊§ť§ §§§»łņ§√§Ņ§≥§»§»…šĻÁ§Ļ§Ž° Ľ≤ĻÕĽŮőŃ3°ň°£

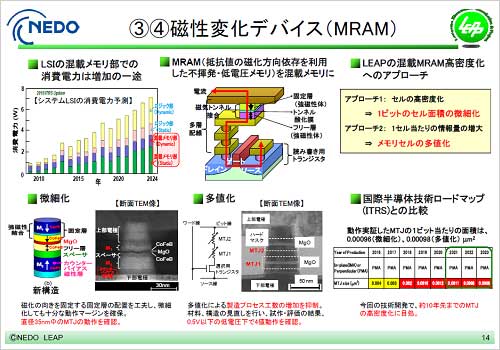

SOTB•»•ť•ů•ł•Ļ•Ņ§Ō•Ū•ł•√•ĮLSIÕ—§ň≥ę»Į§Ķ§ž§Ņ§‚§ő§ņ§¨°ĘLEAP§«§Ō•Š•‚•ÍŃ«Ľ“§»§∑§∆MRAM°ĘPCM°Ęł∂Ľ“į‹∆į•«•–•§•Ļ§‚≥ę»Į√ś§ņ°£§≥§őVLSI Symposium§«§Ō°Ę§≥§ž§ť§őŅ ‚§ň§ń§§§∆§‚ ůĻū§∑§Ņ°£MRAM§«§ŌŃį≤ů° Ľ≤ĻÕĽŮőŃ1§™§Ť§”2°ň§őńĺ∑¬50nm•Ķ•§•ļ§ő•Š•‚•Í•Ľ•Ž§ę§ťļ£≤ů§Ō35nm§ň»ýļŔ≤ŧ∑§∆°Ę§Ķ§ť§ň…‚Õ∑ľß垧ڬ«§Ńĺ√§∑ĻÁ§¶§Ť§¶§ň¬–ĺőĻŬ§§ň§∑§Ņ(Ņř4)°£≤√§®§∆¬Ņ√Õ≤ŧň§ń§§§∆§‚ł°∆§§∑°Ę2•”•√•»/•Ľ•Ž§ő∆įļÓ§Ú≥ő«ß§∑§Ņ°£

Ņř4°°MRAM§Ú»ýļŔ≤ŧ∑°Ę2√Õ≤ŧ‚ĽÓ§Ŗ§Ņ°°Ĺ–ŇĶ°ßLEAP

ŃÍ —≤Ĺ•Š•‚•Í° PCM°ň§«§Ō°Ęń∂≥ Ľ“ĻŬ§∆‚§«§őGeł∂Ľ“§őį‹∆į•Š•ę•ň•ļ•ŗ§Ú≤ÚŐņ§∑§Ņ°£Ļ‚ńŮĻ≥ĺű¬÷§ő≥ Ľ“§»ń„ńŮĻ≥ĺű¬÷§ő≥ Ľ“§»§őī÷§őŃęį‹§ň§Ō∑ŽĺŧÚÕŌ§ę§Ļ§ő§«§Ō§ §Į°ĘŇŇĽ“§ő√Ū∆Ģ§ň§Ť§√§∆Geł∂Ľ“§őį‹∆į§Ú¬•Ņ §∑§∆§§§Ž§»§§§¶°£

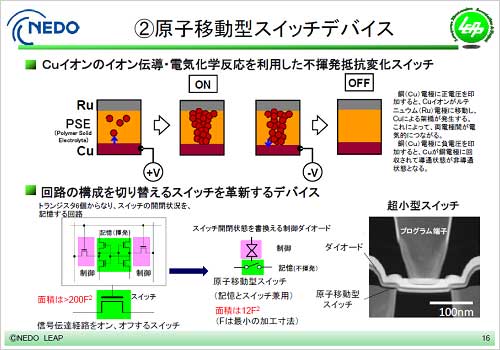

ł∂Ľ“į‹∆į•Ļ•§•√•Ń§«§Ō°Ę…‘īÝ»Įņ≠§őĶ≠≤ĪŃ«Ľ“§Ú•™•ů/•™•’∆įļÓ§Ķ§Ľ§ŽŐÚ≥š§Ú≤Ő§Ņ§Ļ•Ļ•§•√•Ń•ů•į•»•ť•ů•ł•Ļ•Ņ§Úĺģ§Ķ§Į§Ļ§Ž§Ņ§Š°ĘĶ≠≤ĪŃ«Ľ“§ő匧ňŃ– żłĢ•ņ•§•™°ľ•…§Ú•Ļ•§•√•ŃŃ«Ľ“§»§∑§∆ņŖ§Ī§Ņ(Ņř5)°£§≥§őĺžĻÁ§Ō°Ę∂‚¬į-TaO-∂‚¬į§»§§§¶•∑•Á•√•»•≠•ņ•§•™°ľ•…ĻŬ§§ÚĽ»§§°Ę•ņ•§•™°ľ•…§ő§∑§≠§§ŇŇįĶ§Úń∂§Ļ§ęĪاĶ§ §§§ę§«•Ļ•§•√•Ń∆įļÓ§ÚĻ‘§¶°£SRAMĻŬ§§ő6•»•ť•ů•ł•Ļ•Ņ żľį§őŐŐņ—200F2§ň¬–§∑§∆°Ę§Ô§ļ§ę12F2° F§Ōļ«ĺģņ£ň°°ň§«§Ļ§ů§ņ°£

Ņř5°°Ń– żłĢ•ņ•§•™°ľ•…•Ļ•§•√•Ń§«»ýļŔ≤ŧň¬–ĪĢ°°Ĺ–ŇĶ°ßLEAP

§≥§őVLSI Symposium§«§Ō°ĘLEAP§ę§ť§ő»Į…Ĺļő¬ÚŌņ ł§Ō5∑Ô°£§≥§őŅŰĽķ§Ōļő¬ÚŌņ łŅŰ1įŐIMEC§ő9∑Ô§ňľ°§į¬Ņ§§∑ÔŅۧ«§Ę§Ž°£

Ľ≤ĻÕĽŮőŃ

1. LEAP°ĘLSIĺ√»ŮŇŇőŌļÔłļ§ő§Ņ§Š§őMOS§ő≠ýVtń„łļ°Ę…‘īÝ»Įņ≠•Š•‚•Í§ňőŌŇņ (2012/06/15)

2. LEAP§őń„ĺ√»ŮŇŇőŌ°¶…‘īÝ»Įņ≠•Š•‚•Í§Ō•ő•§•ļ•ř°ľ•ł•ůĻ≠§≤°ĘĻ‚Ĺłņ—≤ĹŐ‹Ľō§Ļ (2012/12/25)

3. ST•ř•§•Į•Ū§¨•’•°•÷•ť•§•»ņÔő¨§Úļő§Í§ §¨§ť§‚IDM§ň§≥§ņ§Ô§ŽŃņ§§§»§Ō (2013/02/28)