Micronが176層NANDフラッシュの設計思想を明らかに

チップ同士を重ね合わせる3次元ICが本格化する。メモリメーカーのMicron Technologyが176層のNANDフラッシュを開発した技術(参考資料1)を明らかにした。実は88層のNANDフラッシュメモリセルを重ね合わせて構成していた。

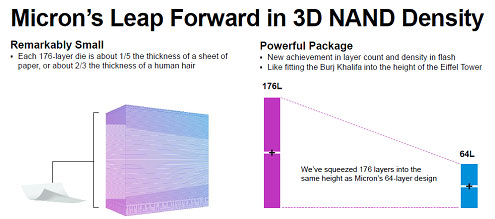

図1 176層のNANDフラッシュの厚さは64層と同じ 出典:Micron Technology

これまでも3D-ICがなかったわけではない。DRAMメモリアレイを縦に重ねるHBM(High Bandwidth Memory)(参考資料2)や、Intelが3D-IC技術Foverosを採用した最新製品Lakefield(参考資料3)などが出荷されている。TSMCはGoogleと組み、3D-IC技術を使った製品を22年にも量産するという。MicronはさらにNANDフラッシュにも積極的に量産に使っている。NANDフラッシュという大量生産製品に3D-ICが使われることで、3D-IC時代を迎えたと言っても過言ではない。ここに、3D-ICの国家プロジェクトを推進してきた日本の姿はない。

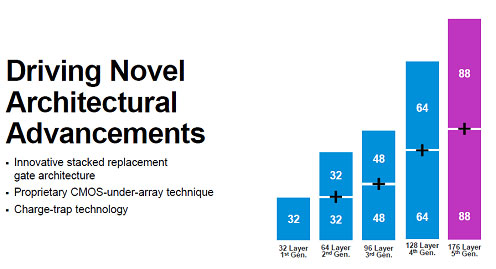

3D-NANDフラッシュの製造では、モノリシックにメモリセルをシリコンで何層もリソグラフィ+エッチング+デポジションを繰り返しながら積み上げていく。32層くらいまでなら何とか処理時間内にできたが、今回のように176層となるとプロセス時間がかかりすぎて数カ月にも及んでしまう。これでは量産にはとても間に合わない。そこで、Micronは、メモリセルだけを重ねていく方法を採った。実はMicronは、このスタッキング技術を64層から使っており、今回の176層は第4世代となる(図2)。

図2 Micronは64層から3Dスタック技術を使っていた 出典:Micron Technology

上の図からもわかるようにMicronは64層からスタック技術を使ってきており、第2世代の96層、第3世代の128層、第4世代の176層とスタック技術と共に1層の総数も増やしてきた。同社がCuA(CMOS-under Area)と呼ぶこの技術では、CMOS回路を先に作製してからメモリセル部分を1層ずつ積んでいく。88層まで達すると貫通孔を開け、下地との配線を形成する。176層を作ってから貫通孔を開けるにはあまりにも高精度なアスペクト比が必要になるからだ。貫通孔は従来通りRIE(反応性イオンエッチング)を使う。高層ビルに設置するエレベータのようなもの、と表現している。

176層を一気に貫通孔を作成することは難しいが、その半分の88層なら形成できそうだ。88層のメモリアレイをスタックして合計176層となる。同社はこの方法で更なる高層化が可能になると見ているが、その詳細には明らかにしていない。ただし、スタック技術を使えば、88層のメモリアレイを3枚、4枚とスタックすることである程度まで可能になりそうだ。モノリシックでの高層化=プロセス時間の延長につながり、ウェーハプロセス期間が長くかかる恐れが出てくる。これを避ける意味でも、3枚、4枚といったスタック層数の多層化はありうる解となりそうだ。

今回出荷したNANDフラッシュの容量は0.5Tビットであり、TLC(3ビット/セル)技術を使っているという。また、転送速度が1600MT/sと広帯域化できたのは、CMOS回路の工夫によるとしている。ただし、従来の128層のNANDフラッシュデバイスと比べ、読出しレイテンシが35%以上も短縮できたのは、メモリアレイ内のブロックのサイズを小さくしたからだという。しかもメモリアレイを3次元化しているため、チップ面積は従来よりも30%小さくできたとしている。

Micronは、NANDフラッシュの縦方向の層数をさらに増やすことで今後の大容量化にも自信を深めている。

参考資料

1. Micron、176層という最高層のNANDフラッシュをサンプル出荷 (2020/11/10)

2. AMD、3D-ICメモリをインタポーザに搭載した2.5Dモジュールを開発 (2015/06/26)

3. 3D-ICがいよいよパソコンに載る時代へ (2020/06/16)