高集積SoC向けエミュレータをMentorがリリース

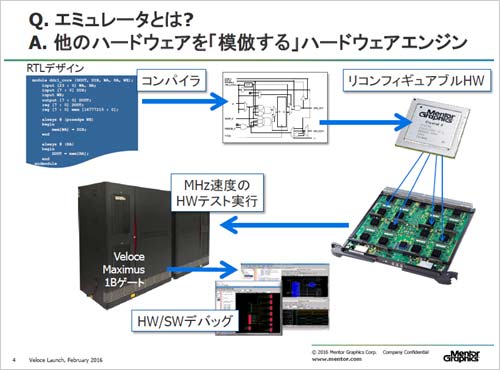

半導体設計回路が正常に動作するかどうかを検証するエミュレータをMentor Graphicsがさらに進化させている。半導体ICの集積度が上がり複雑になるにつれ、設計やプロセスも複雑で難しくなるが、検証も極めて困難になる。ソフトウエアの検証にはシミュレータを使うがハードウエアの検証にはエミュレータを使う(図1)。今回Mentorはエミュレーションに必要なアプリを新規に開発した。

図1 今さら聞けないエミュレーション 出典:Mentor Graphics

Mentorは数年前からエミュレータVeloce(ベローチェと発音)を設計販売しているが(参考資料1)、半導体の集積度が数十億トランジスタにもなると、回路配線的には正しくてもタイミングがずれて正常な動作をしなくなることがある。ソフトウエアシミュレーションだけで開発しているLSIが正しく動いたとしても実際の回路を組んでみないと正常な動作を期待できない。このためこれまではFPGAを使って論理回路を形成し、さらに検証エミュレータも使って実証してきた。

しかし、検証が不十分でバグが発生し、トラブルを起こしたLSIは多い。1994年のIntelのPentium FDIVのバグや、2007年のAMDのPhenom TLBのバグなどがあった。記憶に新しい所では、昨年Qualcommの Snapdragonの出荷遅れを発生させたバグがある。このトラブルは、昨年のQualcommの業績悪化の一因になっており、Snapdragonの消費電力が大きすぎてチップを出荷できなかった。このための機会損失が大きかった。

エミュレータはある意味で、一種のコンピュータでもある。このためのOSとミドルウエアやアプリケーションなどのソフトウエアも必要となる。今回のエミュレータでは、3つのアプリを開発し、OSをアップグレードした(図2)。3つのアプリは、1)100%再現性良くデバッグできるDeterministic ICE(In-circuit emulator)、2) 歩留まりを上げるための新DFT(Design for Testability)、3) 複数のクロックを使う設計でクロックを自動的に切り替えるFastPath、である。

図2 Veloceに拡張した新アプリとOS3 出典:Mentor Graphics

Veloce Deterministic ICEは、ICE環境内でデバッグする時にパルス波形を確認でき100%可視化と再現性を実現する。ICEでは実デバイスを外付けしてエミュレーションしたデータをホストデータベースに蓄えるが、今回のアプリでは実デバイスを切り離して仮想化してVeloceでエミュレーションできる。

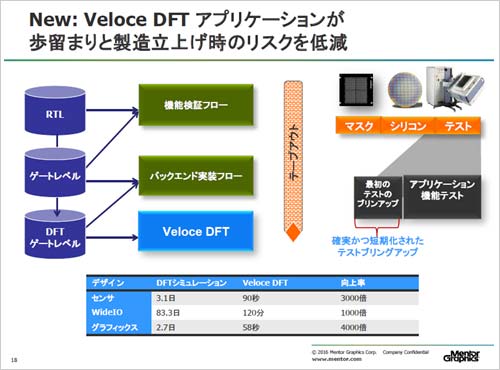

DFTにはJTAGチェーンなどのスキャンパスチェーンの長さやテストパターンなどの情報を搭載している。ここでは、歩留まりが上がるような回路構成を確認することができる。ただし、従来DFTを使ってパターン検証しても極めて長い時間がかかっていた。Veloce DFTアプリを使えば、従来よりも極めて速く検証できる。例えば、センサだと、DFTシミュレーションで3.1日かかっていた検証がわずか90秒で済み、グラフィックスICでも2.7日が58秒で済んだ。最も厄介なWideIOチップでは83.3日もかかっていたが、これは120分ですんだ(図3)。このため、テープアウト前にDFTを終えることができた。

図3 Veloce DFTアプリで高速エミュレーションを実現 出典:Mentor Graphics

Veloce FastPathでは、クロックを複数使うような超高集積ICの設計検証においてこれまでよりも高速になるモデルを開発したことで、検証時間を半減させた。特にクリティカルパスの処理を工夫したという。

新しいOS3では、従来ボトルネックであったコンパイル時間を半減させた。新OSでは、ゲートをブロック単位にまとめ、コンパイルすることで、少ないメモリですみ、高速にコンパイルできた。従来はゲート1個ごとにコンパイルしていた。OS3はパルス波形の目視までの時間も半減した。

2012年に同社はVeloceで専用LSIのCrystal 2を開発したが、最近のFPGAはもはやエミュレーションには使えなくなってきたことが背景にある。最新のFPGAにはDSPや乗算器などエミュレーションに必要のない回路が載っており、無駄になる。だから、Mentorはエミュレーション専用のプログラマブルLSIのCrystal 2チップを開発した。

図4 Mentor Graphicsエミュレーション部門Product Marketing ManagerのGabriele Pulini氏

今回、このチップに関して、同社Product Marketing ManagerのGabriele Pulini氏(図4)から詳細を聞くことができた。このチップはFPGAとは違い、リコンフィギュアラブル回路ブロックを複数持ち、それらをクロスバースイッチで接続している。従来のFPGAだとチャネルベースの配線であるため、遅延が大きかった。Crystal 2では、さらにデバッグ用の可視化機能、パルス波形を捉えるためのトリガー機能、そして波形メモリやチップ間通信インターフェースなども集積されている。

Veloceに使われるコンピューティングボードにはこのCrystal 2を16個搭載し、そのボードを数十枚搭載している。まさにデータセンターのコンピュータさながらだ(図5)。

図5 Veloce本体の中のコンピュータボード エミュレータ専用ICが16個搭載されている

MentorはVeloceエミュレータをシリコンバレーと東京に持っている。高集積LSIを設計するようなユーザーにはOS3を付けてVeloceを販売する。付随のソフトウエアはアドオンで販売する。ベンチャーや小さなユーザーにはサービス提供の形でVeloceをネットワーク経由のタイムベースで貸し出す。想定ユーザーとしては、半導体メーカーの他にIPベンダーやシステムハウスなどがある。システムハウスでは、Juniper NetworksのASIC設計に使っている。IPベンダーでは、ARMとImagination Technologiesが採用している。

参考資料

1. Mentor Graphics、クラウドベースのVerification 3.0時代へ (2014/04/11)

2. メンターグラフィックス、専用プロセッサを開発、エミュレータを2倍高速 (2012/05/02)