メンターグラフィックス、専用プロセッサを開発、エミュレータを2倍高速化

メンターグラフィックスは、高速のエミュレータVeloce2と、SoCの周辺インターフェース回路をソフトウエアで検証するツールVeloce VirtuaLABをリリースした。エミュレータは、膨大な時間がかかるソフトウエアのシミュレーションの代わりにハードウエアを組んで「シミュレーションする」もの。Veloce2もVeloce VirtuaLABも時間のかかる検証作業を短時間で行うための開発環境である。

図1 エミュレータに搭載したリコンフィギュアラブルIC 出典:Mentor Graphics

Veloce2(ベローチェ)は、第1世代のVeloce1エミュレーションツールよりも高速に検証するために、従来のFPGAなどではなく専用のリコンフィギュアラブルなプロセッサIC「Crystal2」チップを搭載した。この結果、第1世代のVeloceと比べ、性能とキャパシティは2倍に、生産性は4倍上がるという。このチップは、メンターがハードウエアエミュレーションするための専用IC。検証作業はシステムごとに構成が変わるため、プログラマビリティが要求される。このICでは、LUT(ルックアップテーブル)の情報を変えることで開発すべきSoCに組み込むソフトウエアを変えることができる。機能的には、高速のコンパイル、フルデバッグの可視化、メモリモデリング機能を備えている。しかも65nmプロセスで設計しながら、機能は45nmプロセスチップを上回る性能だとしている。

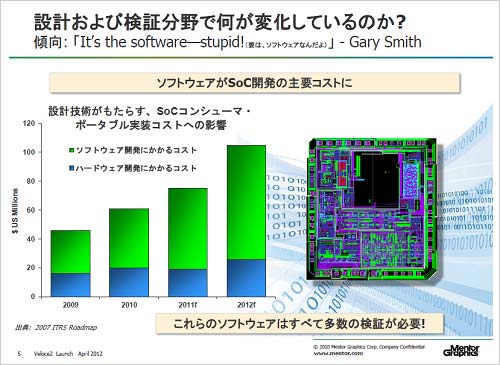

エミュレーションするための専用ICを同社が開発したのは、組み込みシステムやSoCではソフトウエアの重要性が増してきているためである。ソフトウエアの量が増えれば検証時間が膨大になってしまう。ソフトウエアを駆使するプロセッサのコア数は2004年に平均1.06個だったが、2007年は1.46個、2010年には2.14個と増えてきている。プロセッサのコア数やプロセッサ数が増えてくるということは、それだけソフトウエアの負担がかかるということである。実際、SoC開発におけるソフトウエアコストは年々上昇している(図2)。

図2 ソフトウエアの比率がますます高まるSoC 出典:Mentor Graphics

そうなると、ソフトウエアのデバッグや、フォーマリティチェックだけではなく、SoCの回路をチェックするためのテストベクトルの生成や、それをシミュレーションするための検証作業が必要になってくる。例えば、デジタルカメラに60フレーム/秒という高速動画機能を付ける場合(1000万ゲートクラスの比較的小規模回路)、リアルタイムOSを起動して60フレーム/秒の処理を行うのに20億回のクロックサイクル数が必要となるという。これをソフトウエアでシミュレーションすると309時間(13日)かかるが、Veloceを使ってハードウエアでエミュレーションすると20分で終わるという。つまりVeloceエミュレータはシミュレーションよりも800倍も高速である。しかも検証作業にはテストベクトル開発とシミュレーションなどの作業が検証作業の半数を超えるという。この作業に高速エミュレータを導入することで、検証時間を少しでも短縮しようというものだ。

もう一つのツール、Veloce VirtuaLAB は、SoCの主要な周辺インターフェース(USBやEthernet、PCI Express、SATA、SAS、video/audio)をシミュレーションするためのソフトウエア。Veloce VirtuaLABには、これらのインターフェースのRTLを統合している。このためターゲットとする周辺インターフェースの環境をソフトウエアで再現できる。従来は、物理的な周辺インターフェースのエミュレータへの接続にはハードウエアのアダプタを介して行っていた。Veloce VirtuaLABだとソフトウエアレベルで周辺インターフェース回路のシミュレーションができる。このため、ハードウエアがまだ製造されていない段階からハードウエアと組み込みソフトウエアの検証を同時に進めることができ、製品開発サイクルを大幅に縮めることができる。