SiTime、4つのSoCに同時にクロック信号を送れるICを製品化

MEMSを利用する振動子と発振回路、クロック発生器を1パッケージに実装したクロックICは、小型、高性能、低ノイズだけではなく、クロック周りのプリント基板設計も簡易にしてくれる。MEMSベースのクロックICを手掛けてきたSiTimeが4つのSoCを同時にクロックできる4出力のクロックIC「Chorus」を製品化した。

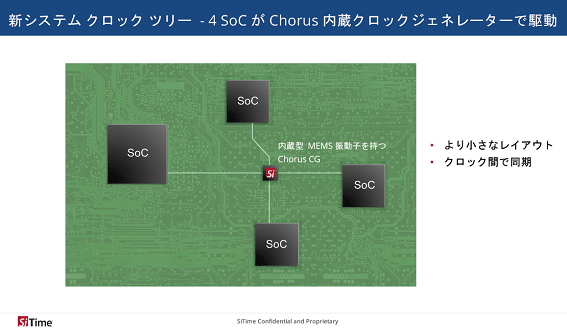

図1 1チップで4個のSoCにクロック信号を供給する、振動子内蔵のクロックIC 大きさは4mm角のパッケージ 出典:SiTime

正確なタイミングが必要なデジタル機器では、正確なパルスを発生するクロックICが欠かせない。このため、温度変化にも長期間の信頼性にも全く変わらないクロック信号を出力しなければならない。正確であることが最優先のICである。

水晶振動子は温度依存性が強いため、ヒーターなどで定温に保つ必要がある上、振動子だけでは振動が減衰するため、それを補う発振器が必要となる。ここまでは正弦波でも構わないが、しかもきちんとしたパルスを出すためには、クロック発生器で正確なパルス波形を出力しなければならない。パルス波形の立ち上がりや降下のエッジでの操作なども求められるからだ。これら3点はプリント基板上にディスクリートで組み合わされて使われることが多かった。しかし、プリント基板上の実装面積が問題になる小型形状や多数のSoCやアクセラレータなどにクロックパルスを与えらければならなくなると、実装面積に余裕がなくなってしまう。しかもクロックICの数もバカにならない。

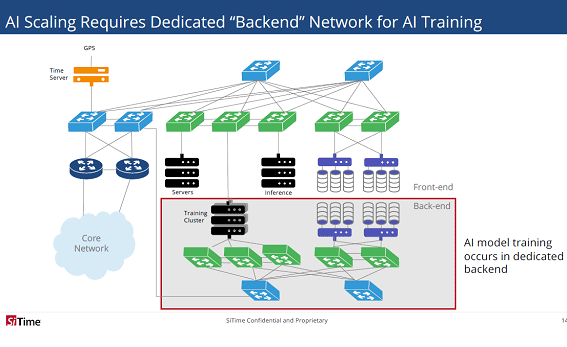

データセンターでは、同期を採るためのスイッチやサーバ、ストレージなどに加えて、最近はAI(機械学習やディープラーニング)専用の推論サーバや学習サーバも備えている。特にAIの学習サーバは、表に出ずむしろ裏で働くことが多いが(図2)、いったん学習させてしまえば、推論サーバが活躍する。さらにデータセンターそのものは仮想化してソフトウエア(ハイパーバイザ)でクライアントに分配するため、こういったスイッチやサーバの数は増える一方だ。このためクロックICも同様なうえ、プリント回路基板上には複数のクロックICが必要となる。

図2 AI学習サーバは裏で働いている 出典:SiTime

こういった用途を狙ったクロックICが今回の「Chorus」シリーズとなる。例えば4つのSoCへクロックを供給する場合、従来ならSoCごとに発振器やクロックICが必要だったが、Chorusシリーズだと1個で済む(図2)。しかも1チップの大きさが4mm×4mmしかないため、ボード面積を小さくできるだけではなく、4つのSoCをできるだけ近づけてレーシングやクロック遅延を避けることができる。

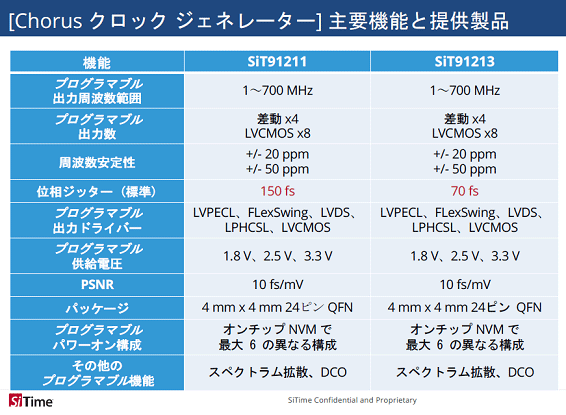

クロックICでは、クロック波形とその位相揺らぎであるジッターが小さければ小さいほど望ましいが、Chorusシリーズは150fs(10のマイナス15乗秒)と70fsの製品がある。極めて短い。

図3 Chorusシリーズのスペック 出典SiTime

SiTimeのクロックICは、MEMS振動子をCMOS信号処理IC上に搭載しモールドでパッケージした製品。MEMS振動子は薄膜メンブレンを作製するため垂直に深くシリコンを削り取らなければならないため、Boschプロセスと呼ぶ、デポジションしながらエッチングするという処理が必要。MEMSデバイスの製造はBosch、CMOSICはTSMCに、パッケージングは台湾のASEやマレーシアのCarsemにそれぞれ依頼している。SiTimeは純粋のファブレスだ。