VLSI SympoŹó¹š”§Intel¤ĪMayberry CTO”¢„³„ó„Ō„唼„æ„Č„ģ„ó„ɤņøģ¤ė

VLSI Symposium¤Ī“šÄ“¹Ö±é2ĘüĢܤĒ¤Ļ”¢Intel¤ĪCTO¤Ē¤¢¤ėMichael Mayberry»į¤¬”¢„³„ó„Ō„唼„Ę„£„ó„°¤ĪĀē¤¤ŹĪ®¤ģ¤Č¾Ķč¤ĪŹżøž¤Ė¤Ä¤¤¤Ęøģ¤Ć¤æ”£„Ē”¼„æ„»„ó„攼¤Ī„Č„Ż„ķ„ø”¼¤¬ŹŃ¤ļ¤ź”¢Ćę±ū¤«¤éŹ¬»¶²½¤ĪŹżøž¤ņ¼Ø¤·¤æ”£É¬ĶפŹČ¾Ę³ĀĪ„Ē„Š„¤„¹¤Ė¤āæؤģ”¢GAA¹½Ā¤¤Ź¤É¤ĪĶȳŗŁ²½”¢„Į„Ƅׄģ„ƄȤĖ¤č¤ė¹ā½øĄŃ²½”¢3D-IC²½¤Ųøž¤«¤¦”£„ą”¼„¢¤ĪĖ”Ā§¤Ī¤č¤¦¤Ė”¢„Ē”¼„æĪĢ¤Ļ3ĒƤĒ2ĒÜĮż¤Ø¤ė¤ČĶ½øĄ¤·¤æ”£

æŽ1””Intel Senior VP·óCTO & GM Technology Development¤ĪMike Mayberry»į””½ŠÅµ”§Intel Corp.

¤³¤ģ¤«¤é¤ĪČ¾Ę³ĀĪ„³„ó„Ō„唼„Ę„£„ó„°¤Ē½ÅĶפŹ¤³¤Č¤Ļ”¢„¹„±”¼„ź„ó„°¤Ą¤±¤Ē¤Ļ¤Ź¤Æ”¢¤Ų„Ę„ķ„ׄķ„»„Ć„µ¤Ī½øĄŃ²½¤ä”¢Ę±»žŗĒŬ²½”¢„½„Õ„Č„¦„Ø„¢¤¬¤±¤ó°ś¤¹¤ė„Ļ”¼„É„¦„Ø„¢”¢AI”ŹæĶ¹©ĆĪĒ½”Ė”¢Ķ„¤ģ¤æ„³„ó„Ō„唼„æ„ķ„ø„Ć„Æ¤Ą¤Č¤¤¤¦”£¤³¤ģ¤Ž¤Ē¤Ī„µ”¼„Š”¼¤ä„Ń„½„³„󤥤±¤Ē¤Ļ¤Ź¤Æ”¢„Æ„ė„Ž¤ä”¢„Ē„ø„æ„ė„Ę„ģ„Ó¤Ī¤č¤¦¤Ź„Ö„ķ”¼„É„„ć„¹„Ę„£„ó„°„µ”¼„Ó„¹”ŹNetflix¤Ź¤É”Ė”¢“Ę»ė„«„į„锢IoT„Ē„Š„¤„¹¤Ź¤É¤µ¤Ž¤¶¤Ž¤Ź„Ē„Š„¤„¹¤«¤éĄø¤ß½Š¤µ¤ģ¤ė„Ē”¼„æ”ŹĄ°Ķż¤µ¤ģ¤Ę¤¤¤Ź¤¤„Ē”¼„攧unstructured data”Ė¤¬¤Ž¤¹¤Ž¤¹ĖÄĀē¤ĖĮż¤Ø¤ė¤æ¤į”¢¤³¤ģ¤é¤Īµ»½Ń¤¬·ē¤«¤»¤Ź¤Æ¤Ź¤ė¤Ī¤Ē¤¢¤ė”£

¤ā¤Ć¤Č¶ńĀĪÅŖ¤Ė¾Ņ²š¤·¤č¤¦”£Īć¤Ø¤Š„Æ„ė„Ž¤Ļ¤«¤Ä¤Ę„Ļ”¼„É„¦„Ø„¢¤Ī¤ß¤Ą¤Ć¤æ”£¤½¤ģ¤¬„æ„Æ„·”¼¤ĪÅŠ¾ģ¤Ē„µ”¼„Ó„¹¤ņÄ󶔤¹¤ė¤č¤¦¤Ė¤Ź¤ź”¢ŗĒ¶į¤Ē¤Ļ¼«Ę°±æž¤Ėøž¤±¤æADAS¤Ī¤č¤¦¤Ė„µ”¼„Ó„¹+¾šŹó¤ņÅėŗܤ¹¤ė¤č¤¦¤Ė¤Ź¤Ć¤æ”£¤½¤ģ¤Ė¤č¤Ć¤Ę²ĮĆĶ¤ĻĮżĀē¤¹¤ė”£

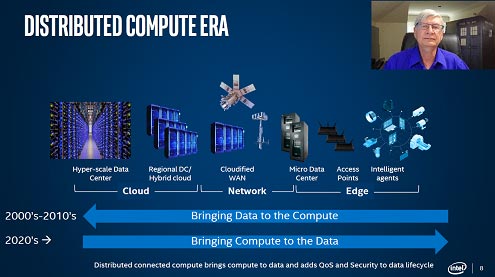

„Ē”¼„æ¤Ė°ī¤ģ¤ėĄ¤³¦¤ņ¤ā¤Ć¤Č¤¤ģ¤¤¤ĖĄ°Ķż¤¹¤ė¤æ¤į¤Ė”¢„Ē”¼„æ„»„ó„攼¤Ī„Č„Ż„ķ„ø”¼¤¬ŹŃ¤ļ¤ė¤ČMayberry»į¤ĻøĄ¤¦”£¤³¤ģ¤Ž¤Ē¤ĪĆę±ū½øø¢ÅŖ¤Ź„Ē”¼„æ„»„ó„攼¤«¤é¤ā¤Ć¤ČŹ¬»¶ÅŖ¤Ź„Ē”¼„æ„»„ó„攼¤ĖŹŃ¤ļ¤ė¤Č¤¤¤¦¤Ī¤Ą”£„Ē”¼„æžĮ÷¤Ī„³„¹„ȤĻ„³„ó„Ō„唼„愳„¹„ȤņĶ¤Ø¤ė¤č¤¦¤Ė¤Ź¤ź”¢„Ø„Ć„ø¤Ų¤Č¶į¤Å¤Æ¤«¤é¤Ą”£¤Ä¤Ž¤ź”¢„Ƅ鄦„É„Ł”¼„¹¤Ī„Ē”¼„æ„»„ó„攼¤«¤éĆĻ°č¤Ī„Ē”¼„æ„»„ó„攼”¢ÄĢ殓šĆĻ¶ÉĘā¤Ē¤Ī„Ƅ鄦„ÉWAN¤ä„Ø„Ć„ø“šĆĻ¶É¤Ē¤Ī„Ē”¼„æ„»„ó„攼”¢¤µ¤é¤Ė¤Ļ„Ø„Ć„ø¤Ē¤Ī„Ē”¼„æ„»„ó„攼¤Ź¤É¤Ų¤ČŹ¬»¶¤¹¤ė”ŹæŽ2”Ė”£

æŽ2””„Ē”¼„æ„»„ó„攼¤ĻĆę±ū½øø¢·æ¤«¤éŹ¬»¶·æ¤Ų””½ŠÅµ”§Intel Corp

„Ē”¼„æ„»„ó„攼¤¬Ź¬»¶²½¤µ¤ģ”¢Ą°Ķż¤µ¤ģ¤Ę¤¤¤Ź¤¤„Ē”¼„椬Ą°Ķż¤µ¤ģ¤Ź¤¬¤é¤ā„Ē”¼„æ¤ĪĪĢ¤ĻĮż¤ØĀ³¤±¤ė”£µÕ¤ĖøĄ¤Ø¤Š”¢Ą°Ķż¤µ¤ģ¤Ę¤¤¤Ź¤¤„Ē”¼„æ¤ĪĒśČƤņĖɤ°¤æ¤į¤Ė„Ē”¼„æ„»„ó„攼¤¬Ź¬»¶²½¤¹¤ė¤Č¤ā¤¤¤Ø¤ė”£

Ź¬»¶²½„Ē”¼„æ„»„ó„攼¤Ė¤Ź¤ģ¤Š”¢¤½¤³¤ĖÅėŗܤµ¤ģ¤ėČ¾Ę³ĀĪ„Į„ƄפĻ”¢Ä¶¾®·æ¤Ī„Ē”¼„æ„»„ó„攼¤Ī¤č¤¦¤Ė”¢CPU¤ČGPU”¢DSP”¢NPU”Ź„Ė„唼„é„ė„Ķ„Ć„Č„ļ”¼„Ƅׄķ„»„Ć„µ”Ė¤Ź¤ÉXPU”ŹĀææō¤Ī°Ū¼ļ„ׄķ„»„Ć„µ”Ė¤Ė¤Ź¤ė”£¤³¤ģ¤Ļ”¢„Ø„Ć„ø¤Ē¤ĪĄģĶфׄķ„»„Ć„µ¤Ī¤č¤¦¤Ė”¢„É„į„¤„󄹄Ś„·„Õ„£„Ć„Æ¤Ź„¢”¼„„Ę„Æ„Į„ć¤ņ»ż¤Ä¤č¤¦¤Ė¤Ź¤ė”£„Ø„Ķ„ė„®”¼øśĪؤņ¾å¤²¤ė¤æ¤į¤Ą”£

„Ų„Ę„ķ„ׄķ„»„Ć„µ„¢”¼„„Ę„Æ„Į„ć¤Ļ”¢ĢæĪį„»„ƄȤ¬„ׄķ„»„Ć„µ¤“¤Č¤Ė¤¢¤ź”¢¶Ė¤į¤ĘŹ£»Ø¤Ė¤Ź¤ė”£½øĄŃÅŁ¤¬Įż¤¹¤Ą¤±¤Ē¤Ļ¤Ź¤Æ”¢„ׄķ„°„é„ß„ó„°¤āŹ£»Ø¤Ė¤Ź¤ź”¢³«ČÆ“ü“Ö¤¬Ä¹“ü¤Ė¤ļ¤æ¤ė¤č¤¦¤Ė¤Ź¤ė”£¤½¤ģ¤Ą¤±¤Ē¤Ļ¤Ź¤¤”£„į„ā„źĶĘĪĢ¤āĖÄĀē¤Ė¤Ź¤ź”¢¾ĆČńÅÅĪĻ¤¬ĖÄĀē¤Ė¤Ź¤ź¤¹¤®¤ė”£²Ć¤Ø¤ĘAI„Į„ƄפĻĘƤĖ³Ų½¬„Į„ƄפĪ½øĄŃÅŁ¤Ļŗ£¤Ė¤āĮż¤·¤ĘĶŹ£»Ø¤Ė¤Ź¤ė”£¤Ž¤µ¤Ė„³„ó„Ō„唼„Ę„£„ó„°„®„ć„Ƅפ¬¤Ē¤¤Ę¤·¤Ž¤¦”£

¤½¤ģ¤ņ²ņ·č¤¹¤ė°ģ¤Ä¤Ī„½„ź„唼„·„ē„󤬄ā„ø„å„锼Źż¼°¤Ē”¢„³„ó„Ō„唼„Ę„£„ó„°¤Ļ„ģ„¤„䔼¤“¤Č¤ĖĆź¾Ż²½¤·”¢æ·¤æ¤Ź¼«Ę°²½„Ä”¼„ė¤āɬĶפĖ¤Ź¤ė”£„Ļ”¼„É„¦„Ø„¢ÅŖ¤Ė¤Ļ3¼”øµ²½¤ä2.5¼”øµ²½¤Ė¤č¤Ć¤Ęµ”Ē½¤“¤Č¤Ė½øĄŃ¤·¤Ę¤¤¤Æ”£¤³¤ģ¤Ė¤č¤ź”¢Č¾Ę³ĀĪĄ½ÉŹ¤Ė½øĄŃ¤µ¤ģ¤ė„Č„é„ó„ø„¹„ææō¤Ļ2ĒƤĒĒܤĖ¤Ź¤ė¤Č¤¤¤¦„ą”¼„¢¤ĪĖ”Ā§¤¬Ā³¤Æ¤³¤Č¤Ė¤Ź¤ė”£

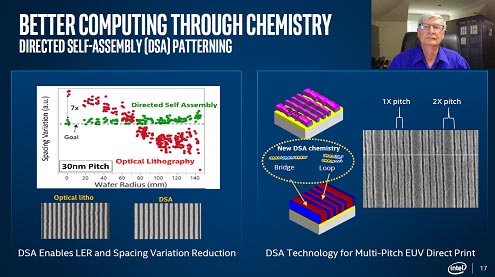

¹ā½øĄŃ²½µ»½Ń¤Č¤·¤Ę”¢„Č„é„ó„ø„¹„æ¤ĻGAA”ŹGate All Around”Ė¹½Ā¤¤Ė¤Ź¤ź”¢„Ń„æ”¼„ó„Ė„ó„°¤Ļ²½³ŲÅŖ¤Ź„»„ė„Õ„¢„鄤„óµ»½Ń¤ĪDSA”ŹDirected Self-Assembly”Ėµ»½Ń”ŹæŽ3”Ė¤ņ»Č¤¦¤³¤Č¤Ē„¦„§”¼„ĻĢĢĘā„Š„é„Ä„¤ņĶŽ¤Ø¤ė¤³¤Č¤¬¤Ē¤¤ė¤Č¤¤¤¦”£

æŽ3””ĶȳŗŁ²½¤Ė¤ĻDSA¤ĒĀŠ±ž””½ŠÅµ”§Intel Corp

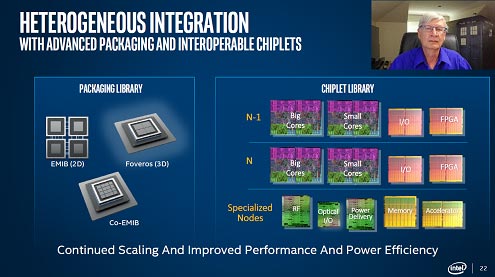

3¼”øµ²½¤Ē¤Ļ„į„ā„ź¤ä„ķ„ø„Ć„Æ¤Č¤Ī„¹„æ„Ć„Æ¤¬ø½¼Ā¤Ė¤Ź¤ź”¢Intel¤Ļ¤¹¤Ē¤Ė2.5D¤ĪEMIBµ»½Ń¤äCo-EMIBµ»½Ń”¢3¼”øµ¤ĪFoverosµ»½Ń¤ņ¾¦ÉŹ²½¤µ¤»¤Ę¤¤¤ė”£ŗĒ¶į½Š²Ł¤·¤æLakefield¤ĻFoverosµ»½Ń¤ņ»Č¤Ć¤æ¤ā¤Ī”Ź»²¹Ķ»ńĪĮ1”Ė”£¤³¤ģ¤é¤Īµ»½Ń¤Ļ„Į„Ƅׄģ„ƄȤȤ¤¤¦IP„³„¢¤Ī„鄤„Ö„é„ź¤ņ»ż¤Ä¤³¤Č¤¬É¬ĶפȤŹ¤ė”ŹæŽ4”Ė”£

æŽ4””½øĄŃÅŁ¤ņ¹ā¤į¤ė¤æ¤į¤Ė2.5D”¢3Dµ»½Ń¤ä„Į„Ƅׄģ„Ƅȵ»½Ń¤ņ»Č¤¦””½ŠÅµ”§Intel Corp

¤³¤ģ¤é¤ņĮČ¤ß¹ē¤ļ¤»¤Ę”¢Intel¤ĪFPGA¤Ļ„Į„Ƅׄģ„ƄȤäHBM”ŹHigh Bandwidth Memory”Ė„ā„ø„唼„ė¤ņ2.5D„Ń„Ć„±”¼„ø¤ĖĘž¤ģ¤æ¤ź”¢3¼”øµ¤ĪLakefield¤ČĮČ¤ß¹ē¤ļ¤»¤æ¤ź¤¹¤ė¤č¤¦¤Ź„Ļ„¤„Ę„Æ„Ń„Ć„±”¼„ø¤¬½ÅĶפŹ»žĀå¤Ė¤Ź¤ė”£

¤³¤ĪĄč”¢„Ļ”¼„É„¦„Ø„¢¤Č„½„Õ„Č„¦„Ø„¢¤Ī¶¦Ę±æŹ²½¤¬É¬ĶפĖ¤Ź¤ė”£½¾Ķč¤Ī„Õ„©„ó„Ī„¤„Ž„ó·æ„³„ó„Ō„唼„Ę„£„ó„°¤«¤é„Ē„£”¼„ׄ锼„Ė„ó„°¼źĖ””¢¤µ¤é¤Ė„Ó„Ć„°„Ē”¼„æ¤Ī²ņĄĻ¤ĖɬĶפŹ„°„é„Õ²ņĄĻ”Ź„°„é„Õ¤ĪÄŗÅĄ¤ä„Ø„Ć„ø¤Č¤Ī“Ų·ø¤ņø«½Š¤¹¼źĖ””Ė”¢æĶ“Ö¤ĪʬĒ¾¤Ī»ÅĮȤߤņĢĻŹļ¤¹¤ė„Ė„唼„ķ„ā”¼„Õ„£„Ć„Æ”¢ŗĒ½ŖÅŖ¤Ė¤ĻĪĢ»Ņ„³„ó„Ō„唼„Ę„£„ó„°¤Ų¤Čøž¤«¤¦¤Ą¤ķ¤¦”£¤æ¤Ą¤·”¢ĪĢ»Ņ„³„ó„Ō„唼„Ę„£„ó„°¤Ļ2030ĒÆ°Ź¹ß¤Ė¤Ź¤ė¤Č¤¤¤¦”£

Intel¤Ļ¤³¤ģ¤é¤Īæ·¤·¤¤„¢”¼„„Ę„Æ„Į„ć¤Ī„³„ó„Ō„唼„Ę„£„ó„°¼źĖ”¤ņ»ī¤·¤Ę¤Ŗ¤ź”¢¤½¤Īŗ¤Ęń¤µ¤ņČ©¤Ē“¶¤ø¤Ę¤¤¤ė¤«¤é¤³¤½”¢¤½¤Īµ÷Ī„“¶¤¬¤ļ¤«¤ė¤Ī¤Ē¤Ļ¤Ź¤¤¤Ą¤ķ¤¦¤«”£

»²¹Ķ»ńĪĮ

1. 3D-IC¤¬¤¤¤č¤¤¤č„Ń„½„³„ó¤Ėŗܤė»žĀå¤Ų (2020/06/16)