製造装置・材料の展示会から半導体総合技術展に変わってきたセミコンJ

半導体製造装置や材料の展示会であるセミコン・ジャパンが半導体総合展の様相を見せてきた。DAC(設計自動化会議)というEDA(電子設計自動化)産業がSEMIの中に組み込まれ、半導体設計と製造が近づいている。先週開催された2024年のセミコンは、海外からはIPベンダーやファブレス半導体企業なども参加するようになった。ラビダスのようなファウンドリも昨年に続き出展社側に来ている。

図1 セミコン・ジャパン2024の風景

従来、セミコンは半導体製造装置と化学材料や機械的な部材などの企業が出展しており、来場者はそれらを購入する潜在バイヤーであった。ところが、ここ数年、IoTやAI、5GなどIT産業も出展側に採り入れ、それらを一つの企画として扱い、半導体産業と関連付けようとしてきた。もちろん、配線やゲート長などの微細化技術が行き詰まったための苦肉の策ではあった。

プロセスには配線幅や間隔などの微細化は飽和しており、3次元構造のトランジスタや配線やビアホールなどを採用することで集積度を上げてきた。例えば7nmプロセスとは、配線幅は14〜16nmと広いまま、単位面積当たりのトランジスタ数を約1億個形成できるプロセスと見なしてきた。この3次元化技術はDTCO(Design Technology Co-Optimization)技術あるいはエリアスケーリングなどと呼ばれ、微細化せずに集積度を上げ、単位面積当たりのトランジスタ数によって、5nmプロセスノード、3nmプロセスノード、2nmプロセスノードなどと称してきた。

このため従来と違い、プロセスノードが進むにつれ、フリップフロップをはじめとするスタンダートセルのロジックゲートを設計し直してきた。横浜のみなとみらいにあるTSMCデザインセンターでは日本人IC設計者がスタンダードセルの作り直し作業に従事している。つまりIC設計とプロセスの両方が求められるようになってきたのである。EDA産業がSEMIに取り込まれることは自然の成り行きだった。

いみじくもNvidiaのCEOであるJensen Huang氏が、「微細化技術は止まりつつあるが、コンピューティングパワーを上げよという要求はますます強まっている」、と述べたことは、微細化しなくても集積度をさらに上げ、ICの性能・消費電力をさらに改善してほしいという要求が増えていることを示している。

先端パッケージングに注目

そこで集積度を一気に上げられる技術として、先端パッケージ技術が登場した。Nvidiaの最新GPUのBlackwellは2チップ構成からなっており、「チップ1個はプロセス技術で製造できる最大の面積である」とHuang CEOは述べている。つまり、チップ面積を大きくして集積度を上げたいが、歩留まりが悪化するため2チップ構成にしたのである。2チップで2000億トランジスタ以上を集積している。

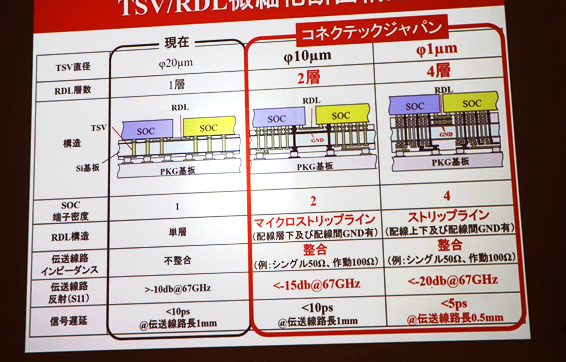

セミコン・ジャパンでは、先端パッケージに名乗りを上げたコネクテックジャパンのブースに人だかりができた。同社は半導体後工程を1個の試作から量産までを担うため、組み立ての量産を請け負うOSAT(Out-Sourced Assembly and Testではなく、自らをOSRDA(Outsourced Semiconductor Research Development & Assembly)と呼んでいる。80°Cという低温でチップを接合できる技術を開発、2024年度はすでに400件以上の開発案件を受託したという。現状ではまだ20µm径のTSV加工を協力会社に委託しているが、26年第2四半期からはTSV(Through Silicon Via)の専用ラインを社内に設け、10µm径でRDL(再配線層)2層のインターポーザ形成を予定している(図2)。

図2 チップレット実装に進出するコネクテックジャパン

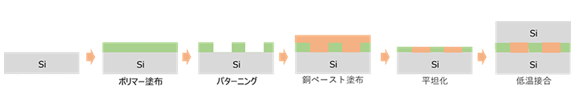

コネクテックの協力会社でもあるダイセルでは、ガラスインターポーザのTSV孔を空けてCu(銅)を埋め込むプロセスに、従来のメッキではなく、Cuペーストを使った印刷工程を利用する。形成時間の短縮とボイドの発生を防ぐという狙いがある。Cuペーストといえどもシードメタルを付ける所までは同じだが、印刷で配線を形成する。その前に一時的な支持フィルムを装着し真空中で印刷、配線した後、支持フィルムを除去しシンタリングし、ペーストで溶かした有機溶剤を蒸発させる。表面上の余分なCuを除去し、ハイブリッドボンディングへと進む(図3)。

図3 銅をメッキではなく印刷で穴埋めするダイセル 出典:ダイセル

先端パッケージングでは、半導体後工程側とプリント基板技術側からのせめぎ合いとなる。これまでプリント基板のCADを得意としてきた図研は、2.5D-ICや3D-IC、チップレットなどの配線・レイアウト・検証などにEDAツール「CR-8000」が使えることを示した。特に、ポリマーのRDLインターポーザを使って微細なビアホールだと配線層数を大幅に削減できることを実証した。従来の配線幅・間隔が8µm/8µmだと再配線層が9〜10層必要だったのに対して、2µm/2µmだと2層程度になることをCR-8000が実証した。

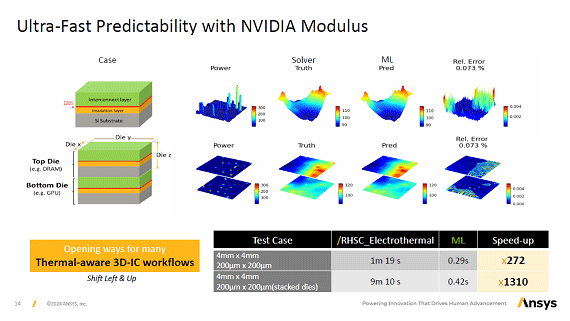

チップレットや3D-ICでは、チップ同士を積層してから不良品がわかるようでは手遅れだ。物理学上の熱や流体、電磁気学などのシミュレーションを得意とするAnsysはTSMCのEDAベンダーの集まりである、TSMC 3DFabric Allianceのメンバーでもある。

同社は先月、Nvidia Modulusと呼ばれるAIフレームワークを、自社のクラウドベースのビッグデータ解析プラットフォーム「Ansys SeaScape」に統合したと発表したが、今回その成果を見せた。SeaScapeにはAnsysのパワーインテグリティや信頼性などのプラットフォームを集積している。4mm角のチップレットの温度分布を従来のモデルベースのシミュレータだと2次元表示による解析結果を見るのに1分19秒かかったが、Nvidia Modulusの機械学習だと0.29秒で同等の結果を得た(図4)。さらにこれを積層した3D-ICでは従来ツールで9分10秒かかったが、機械学習ツールでは0.42秒で同等の結果を得た。AIの威力はすさまじい。

図4 AIを導入したシミュレータは積層した2チップの熱分布シミュレータは1300倍速い 出典:Ansys

また、今回のセミコン・ジャパンでは、英国の半導体企業が使節団として十数社が参加した。出展こそしなかったが、そのうちの2社とインタビューできた。またアイルランドからも半導体や関連企業の誘致に同国政府産業開発庁が自らやってきてアイルランドにおける半導体産業について解説した。台湾からは、国家科学及技術委員会がセミコン・ジャパンでセミナーを開催し、台湾の市場調査会社TrendForceが開催期間中に会場近くのホテルでセミナーを開催した。日本のスタートアップのEdgeCortixも出展し、同社のエッジAI用チップSakuraシリーズのロードマップを見せた。また、アドバンテストは中期経営計画としての他社とのエコシステム構築に向けたプロジェクトを明らかにした。これらの技術に関しては、後日レポートする。