Micronの232層NANDフラッシュは1Tビットの高集積+2.4GB/sの高速化

Micron Technologyがこれまで最多のセル層数である232層の3D-NANDフラッシュメモリを開発(図1)、それを搭載したCrucialブランドのSSDのサンプル出荷を限定ユーザー向けに始めた(参考資料1)。量産は2022年末になる見込みだ。232層と3ビット/セル技術でNANDフラッシュは1Tビットのチップと2Tバイトのパッケージ容量を実現できるという。

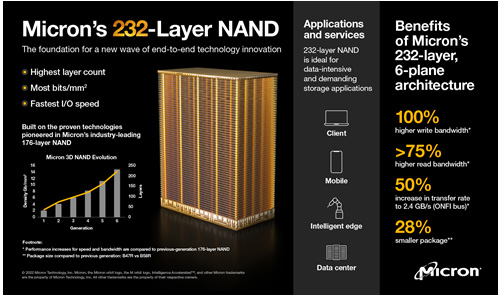

図1 Micronの開発した232層3D-NANDは高速化も達成 出典: Micron Technology

これまでMicronは、176層のNANDフラッシュを発表しており(参考資料2、3)、その時は88層のNANDフラッシュ層を2段積むことで176層を実現していた。当時は88層を製造するのに必要な深くてバラつきの少ないエッチングの精度は、88層が限界だと語っていたが、その限界を突破したといえそうだ。

今回はプロセスにおける層数を116層としたことで、それらを2枚重ねて232層を実現した。これまでSamsungは100層程度が製造の限界と述べており、この限界も突破したことになる。層数を高めたことで、集積密度は14.6Gビット/mm2となり、同じ3ビット/セル(TLC)の競合製品の35~100%の面積になるとしている。

また読み出しのI/O速度は、2.4Gバイト/秒と速い。これはメモリセルアレイを従来4分割(4プレーン)していたのに対して、6分割(6プレーン)にすることで高速化した。一般に、メモリ容量を上げるのに従い、セルまでの距離が長くなりアクセスが遅くなってしまう恐れがある。このため、セルアレイを複数に分割することで、セルにアクセスするまでの距離を短くし高速に読み出す工夫をしている。読み出し速度を上げることによって、低レイテンシで高スループットのデータセンター仕様やAI、非構造化データベース、クラウドコンピューティングなどに向くとしている。

Micronの高集積3D-NANDフラッシュでは、CMOSトランジスタ構造の上にメモリアレイを形成するCMOS under Array(CuA)を採用している。層数を232層に増やしたことで、最大1Tビットのチップを形成できるという。176層の前世代と比べパッケージサイズを28%小さくし、11.5mm×13.5mmのパッケージに収容できるとしている(参考資料4)。これにより前世代より50%高速の2400MT/秒のONFI(Open NAND Flash Interface)転送速度を得ている。

参考資料

1. 「マイクロン、世界初の232層NANDを出荷開始し、テクノロジー・リーダーシップを拡大」、Micron (2022/07/27)

2. 「Micron、176層という最高層のNANDフラッシュをサンプル出荷」、セミコンポータル (2020/11/10)

3. 「Micronが176層NANDフラッシュの設計思想を明らかに」、セミコンポータル(2020/11/19)

4. "First to Market, Second to None: the World’s First 232-Layer NAND", Micron (2022/07/26)