TSMC、有機インターポーザによるCoWoS技術の優位性を実証

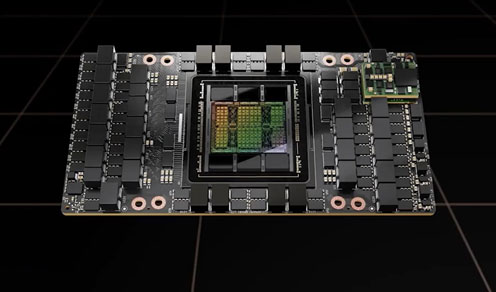

先端パッケージ(Advanced Package)技術が今後ICパッケージの中で最も大きな成長を遂げると市場調査会社が予測している通り、Appleのパソコン用プロセッサであるM1チップやNvidiaの最新GPUチップH100(図1)などに使われている(参考資料1)。ここではインターポーザ技術がカギを握る。TSMCは有機インターポーザによるCoWoS技術が性能だけではなく信頼性も優れていることを明らかにした。

図1 Nvidiaの最新GPU「H100」を搭載したボード 出典:Nvidia

先端パッケージ技術は2.5Dあるいは3D-ICなどと呼ばれているが、その世界市場は2020年から2027年にかけて年平均成長率CAGRが10.2%で成長するという予測から、7.84%成長や8%成長などいろいろな市場調査会社から発表されている。市場規模も2026年に382億ドルや475億ドル、2027年に642億ドル、2028年に550億ドルなど市場調査会社によってまちまちである。とはいえ、400〜500億ドルに成長するとみてよいだろう。

なぜか。TSMCは微細化の先頭を切って、7nm、5nmとやってきて最近では4nmと微細化を進めているが、コスト的には極めて高くなっている。例えば、TSMCは7nm以下のウェーハを全投入ウェーハの1〜2割しか占めていないが、その売上額は全体の半分にも及ぶ。コストがかかるため製造サービス価格も上げている。このため、巨大なチップよりは回路ごとに小さなチップレットに分割して切り出し、マルチチップ実装する方が安い、と同社DirectorであるShin-Puu Jeng氏は言っている。このマルチチップパッケージが先端パッケージである。

ただしチップレットやメモリ、SerDesなどの周辺回路のプロセスノードはまちまちで、しかも配線の電極パッドもバラバラなので、配線をし直さなければパッケージングできない。そこで再配線層(Redistribution Layer)となるインターポーザを導入して最終的にプリント基板に実装しやすくする、あるいは標準的なピン配置に合わせるのである。

シリコン上に回路を構成したダイは、インターポーザ上に端子をボンディングされ、インターポーザ内の再配線層を通り、プリント回路基板(サブストレート)の電極パッドと接続される。大きなシリコンダイだと歩留まりが悪いが、小さなシリコンに分割する方がもはやコストが安くなる、とTSMCのJeng氏は言う。加えて反りが減少し、信頼性も高まるとしている。インターポーザ自身の大きさはレチクルサイズ(32mm×26mm)を基本単位とする。

このインターポーザの材料としてはシリコンウェーハを使う手がこれまでは有効だった。いわゆるシリコンインターポーザである。しかし、TSV(Through Silicon Via)が深くなりすぎると配線層が実質的に長くなる。配線が長くなるとデータ速度が落ちるだけではなく、消費電力も上昇し、さらにノイズの影響を受けやすくなる。良いことは一つもない。HBM3とSoCとの間の距離はJEDEC規格で5.5mm程度なので、HBMのシリコンが厚ければその距離がさらに伸びることになる。インターポーザとして、シリコンよりも薄く作製できる有機ポリマーを使えば、配線距離を短縮できる。そこで、TSMCは有機インターポーザを用いて配線層の短縮を図った。有機ポリマーを評価した結果、28GHzから56GHzへと周波数を上げるに従い損失は、これまでのシリコンインターポーザと同様大きくなるが、現状の薄いシリコンインターポーザよりは小さい。

先端パッケージでは、SoCプロセッサに大容量3次元メモリのHBM(High Bandwidth Memory)が使われており、それもHBM3という最大バンド幅が819GB/秒と極めて広い3次元メモリである。このため配線がデータ速度を落とすことは許されない。

TSMCはインターポーザ上にチップを集積するこの技術をCoWoS(Chip on Wafer on Substrate)技術と呼んでいるが、SoCやチップレットとHBMを集積する用途では大量に使われそうだ。CoWoS技術における有機インターポーザは、シリコンとプリント回路基板との熱膨張係数の違いによる応力を緩和するバッファの役割も持つとしている。

実際、インターポーザの再配線層において信号層を電源層・接地層で挟むことにより、7.2Gbpsの信号のアイダイヤグラムでのノイズとジッターは極めて少なかった。さらに高温保管や高温動作、温度サイクルなどの試験を行った結果、不良品は発生しなかったという。また大きなダイサイズのフリップチップ実装したSoCと比べても、シリコンとプリント基板との熱膨張係数の差を有機インターポーザがバッファとして吸収したことで応力は少なかったとしている。また、シミュレーションだが、4チップのSoCと20チップのHBM3Eを、88.5mm×78.5mm(レチクル8枚分)という巨大な有機インターポーザ上にパッケージした場合でも反りは最大59µmと少ないとしている。

今回の発表は、2022年IMSI(電子実装工学研究所)オープンフォーラムにおける特別講演としてJeng氏が話されたもの。講演中にスライドをコピーして欲しくないと述べていたため、図を示すことができなかったことは残念であるが、Jeng氏は講演の最後に、ガラスインターポーザの可能性について聞かれた質問を紹介しよう。同氏は「インピーダンスが低いという点ではガラスは優れているが、問題はクラックの発生であり、それを防ぐための投資が大きい。その投資をどう回収するかが問題であり、新プロセスはできる限り使いたくない」と述べている。

参考資料

1. 「Nvidia、最新GPU・CPU・ネットワークチップで世界最強のコンピュータを作る」、セミコンポータル (2022/03/25)