TSMCが変身か、10年ぶりの記者会見でロードマップ示す

TSMCが10年ぶりに日本で記者会見を開いた。同社は毎年TSMC Technology Symposiumを世界各地で開催しており、米国や台湾のメディアは参加できたが日本のシンポジウムはメディアを締め出し記者会見さえ開催してこなかった。TSMCの現状をレポートする。

図1 TSMC社Corporate Communications部門シニアディレクタのElizabeth Sun氏

これまでのTSMCには、「傲慢になった」、「ベンチャーは相手にしてもらえない」といった声を聞いた。しかし、会見やシンポジウムには参加できなかったため、本当の姿を日本のメディアは捉えることができなかった。ただし、ここ数年TSMCは変わった、という声も聞いた。どう変わったのか。同社Corporate Communications部門シニアディレクタのElizabeth Sun氏(図1)は、TSMCの三つの強さとして、「技術リーダー」、「卓越した製造技術」、「顧客の信頼の厚さ」を上げ、「TSMCは信頼の厚いサプライヤーです」と何度も語った。「Honesty(正直)とTrust(信頼)」がTSMCの企業文化であり、一言でいえばIntegrity(モラルや顧客に忠実)を32年間貫き通してきたと誇る。ある時期に聞いた「Arrogant(傲慢な)」な態度を反省したのかもしれない。

2019年第1四半期にファウンドリ企業が軒並み2ケタの落ち込みを示した中(参考資料1)で、4%減の落ち込みで済んだTSMCは、「7nmプロセスが収益に貢献した」とSun氏は語る。この第2四半期の見通しに対しても、第1四半期が71億ドルの売り上げに対して、76億ドルになりそうな見込みだと語っている。プロセス別の売り上げでは、7nmプロセスの売り上げは第1四半期には22%だが、第3四半期までに30%に達するのではないかとみている。2018年第3四半期に初めて売り上げが計上された7nmプロセスは、その収益力を急速に増している。2019年の通年では全売上の25%になりそうだとしている。

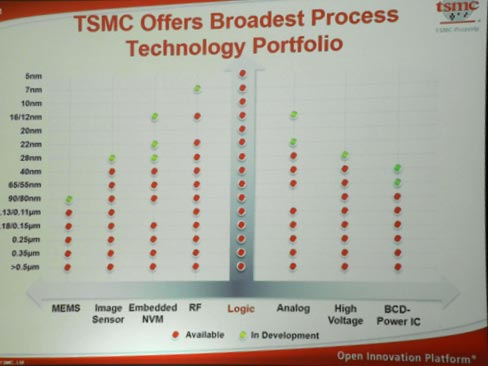

図2 先端の7nmから0.5µm強まで揃えているTSMC

売上額の市場別では、スマートフォンが最大だが、これからはHPC(高性能コンピューティング:いわばデータセンタ向けのハイエンドサーバーやスーパーコンピュータなど)分野が成長すると見ている。スマホでは、QualcommやApple、MediaTek、HiSiliconなどがモデムやアプリケーションプロセッサの製造をTSMCに依頼しているからだ。HPCではNvidiaやXilinxなどが依頼しており、微細化技術では他のファウンドリをリードしている。もちろん、7nmが収益に貢献したといっても、それ以外のデザインルールのプロセスもそろえている(図2)。

TSMCが今回、会見を開いた理由の一つを、昨年Samsungが日本でもファウンドリビジネスを推進していることを訴求し、シンポジウムと記者会見を開催し(参考資料2)、さまざまなメディアが報じたことも今回の開催の要因の一つとみる向きもある。Samsungが7nmプロセス以降3nmまでのロードマップを示したのに対し、今回TSMCは5nmまでの堅実なロードマップを描いた。

これまで7nmプロセスの応用は、HPCや仮想通貨の暗号解読チップだったが、仮想通貨が昨年後半に急落し、しばらくその価格は低迷を続けていた。最近、再び仮想通貨価格は上がり始めている。「スマホにも間もなく7nmを使った製品が出てくる」と同社Business Development担当VPのKevin Zhang氏(図3)は語る。7nmといった微細化はモデムやアプリケーションプロセッサ、FPGAなどを含むロジックチップが加速させていく。

図3 TSMC社Business Development担当VPのKevin Zhang氏

TSMCの微細化ロードマップは、7nmプロセス以降ではこれまでとは違い、ゆっくりとしたペースで歩む。これまでは、28nmの次が20nmあるいは14/16nm、さらに10nm、そして7nmとやってきた。ところが、7nm以降はもっとゆっくり刻んでいく。

7nmプロセスをN7プロセスと表現し、さらにN7プロセスの次はN7+プロセスになるという。N7プロセスとの違いは、7nmをベースにしながら20%ロジック密度を上げたものだとしている。このN7+はEUVを量産で使う初めてのプロセスとなる。EUV技術のアベイラビリティ(可用性:使える状態を維持している割合)が上がり、生産性が上がることを実証してきた。アベイラビリティは2018年の70%から85%へと上がり、2020年には90%以上になる見込みだ。また、EUVの出力は280Wを安定して得られるようになっており、2019年に300W、2020年には350Wに行きそうだという。N7+プロセスの量産は2019年後半からとしている。

その次はN6プロセスで、7nmプロセスをベースにしてスケーリングしたものだという。性能は上がりコスト的には有利になりそうだという。デザインルールやSPICEモデル、IPなどはN7と互換性があり、EDAツールもN7と同じものが使える。広い範囲の応用を目指しリスク生産は2020年第1四半期を予定している。

さらにその先がN5プロセスだ。メインのロジックをスケーリングしたもので、性能は15%上がり、消費電力は30%減少、ロジック密度は1.8倍になるとしている。ここではEUVリソグラフィを使うレイヤーの数が増えるという。N7とは違うeLVT技術を導入するとしている。これは極端に低いしきい電圧VT技術を意味している。リスク生産は2019年3月に始まっている。

その先にはN5Pプロセスが来る。Pは+(プラス)の意味。これはN5と同じデザインルールを使いながら、しきい電圧を下げることによって性能を上げる技術だ。スピードが同じなら消費電力は下がる技術である。

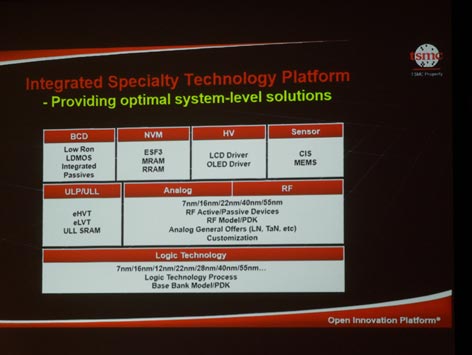

図4 高耐圧デバイスやRF、アナログ、センサ、NVMなどを集積するスペシャルティ技術プラットフォーム

TSMCが提供するファウンドリ技術には、高耐圧トランジスタや不揮発性メモリ、センサなどを集積するスペシャルティ技術もある(図4)。この中で特に、超低消費電流プロセスプラットフォームという形で、SRAMや、RFとアナログ、組み込みNVM(MRAMとReRAM)をIoTやAIを使ったスマート社会向けチップと位置付けている。

組み込み用不揮発性メモリ(eNVM)として抵抗変化型メモリ(RRAM)と磁気メモリ(MRAM)を用意したのは、ユーザーからの要望によるとZhang氏は言う。しかもMRAMは百万回以上のR/W(読み出し/書き込み)耐久性があり、RRAMはマスク数の増加が2枚だけというコスト要因もある。

加えて、さまざまな機能のチップを集積するという点で、2.5Dや3Dの集積技術もある。ファンアウトのウェーハレベルパッケージInFO技術やPoP(Package on package)、CoWoS(Chip on Wafer on Substrate)などの技術を揃え、さらにChip on Chip(SoIC: System on Integrated Chips)やWoW(Wafer on Wafer)などの3D技術もある。WoWはN16プロセスで実証されており、SoIC技術もN7プロセスで成功しているという。2.5D/3D実装技術では、台湾のASEと比べ微細化技術で全く違うため、競合しない、とZhang氏は語っている。

参考資料

1. 直近のファウンドリランキング、2桁マイナス成長企業が続出 (2019/06/26)

2. ファウンドリ2社が成長戦略を語る〜Samsung編 (2018/09/14)