Intelマレーシア見学記(5):CPUテスターは後工程工場で内製されていた!

Intelマレーシア第2回と第3回(参考資料1、2)でCPUテスターをいくつか紹介したが、これらのテスターやテスト用マザーボードは、機密漏洩防止のため、Intelマレーシア後工程工場で内製されていた。Intelマレーシア見学記の最終回となる今回は、CPUテスターの製造の様子を写真で紹介しよう。最後に、おまけでベールに包まれている不良解析ラボについても紹介する。

(1)CPUテスターおよびテスト用マザーボード製造

マレーシアのペナン島の対岸のマレー半島にあるクリム・キャンパスには、システムインテグレーション&マニュファクチャリングサービス(SIMS)と呼ばれる事業部門が同居しており、SMT(表面実装技術)というプリント基板に電子部品を表面実装する装置が並んで、IntelのCPUやGPUなどの最終テスト時に必要なマザーボードおよびこれらを搭載したテストシステムをマレーシア工場内部で製造していた。SIMSでは、プレ・シリコン向けのシミュレータ用基板も製造され、米国はじめ世界中のCPUの開発拠点に提供されているという。CPUテスターやそのためのマザーボードをマレーシア工場で内製するのはIntel社外に製品の秘密が漏洩しないためだという。

(1-1) High Density Modular Tester

最初に、CPUチップのシステムレベルテストを行うための「High Density Modular Tester(HDMT)」の製造現場を紹介しよう。これはCPUの基本性能をテストする装置である。

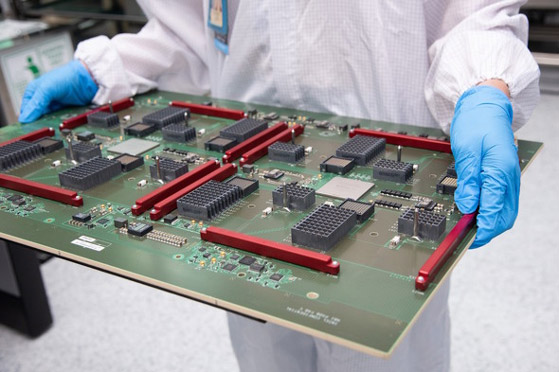

図1 テスター用マザーボード(試作段階)へ手作業で電子部品の装着および検査 出典:Intelマレーシア工場

図2 テスター用マザーボード(試作品)の電気的特性チェック 出典:Intelマレーシア工場

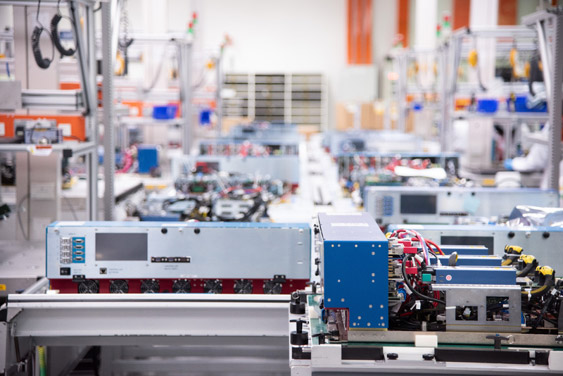

図3 High Density Modular Testerの組み立て現場 出典:Intelマレーシア工場

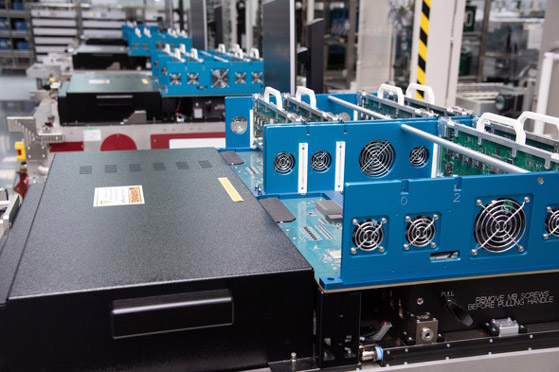

図4 HDMTを4段積み上げて動作確認中 出典:Intelマレーシア工場

(1-2) System Level Tester

System Level Testerは、外付けGPU、SSDなどのストレージデバイス、USBなどの各種周辺機器との連携動作を、Windowsなどの実在OSでの動作下で実際のコンピュータ製品に収まった状態と極めて近い状態で動作試験を行う最終段階のテスターである。

図5 SLT外観 出典:Intelマレーシア工場

図6 流れ作業のテスター量産製造 出典:Intelマレーシア工場

(1-3) High Density Burn-In(HDBI)Tester

High Density Burn-In(HDBI)Testerは、完成したCPUチップを実際に低温/高温状態にしたり、定格よりも高い電圧を掛けたりして、基本動作試験を行うために使われるテスターである。1台の装置で複数のCPUを並行してテストできるようになっている。

図7 High Density Burn-In(HDBI)Tester外観 出典:Intelマレーシア工場

図8 HDBIテスター用マザーボード:厚くて重くて耐熱 出典:Intelマレーシア工場

図9 HDBIテスター生産現場 出典:Intelマレーシア工場

(2) 不良解析ラボ

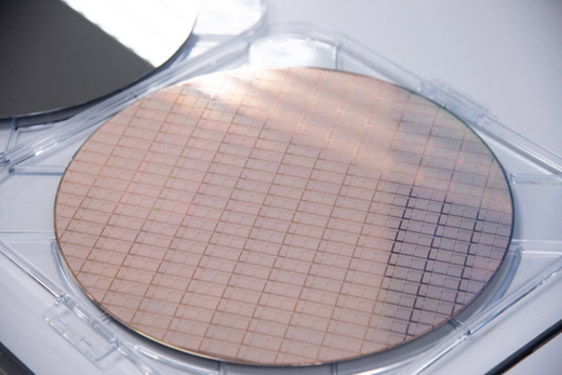

ペナンキャンパスには不良解析ラボがあり、テスターで不良となったCPUチップの不良原因追及作業が行われていた。ウェーハレベルの不良解析も行っており、不良解析情報は米国オレゴン州の開発・試作チームにフィードバックされる。

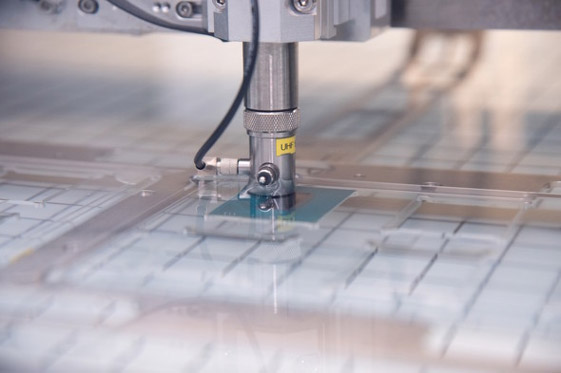

図10 不良解析作業 出典:Intelマレーシア工場

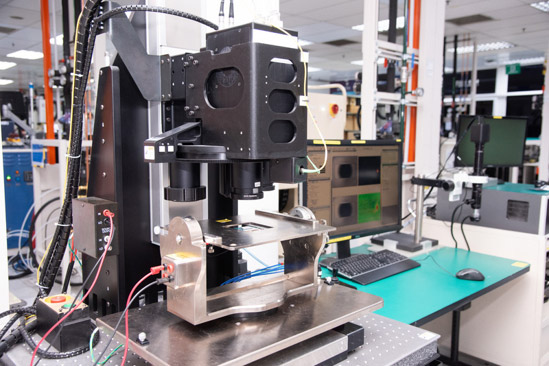

図11 不良チップ表面の温度分布を観察するための周波数ロックイン・サーモグラフィ 周波数を固定して温度分布を測定できるようになっている 出典:Intelマレーシア工場

図12 不良CPUチップの内部の陥を検出する超音波顕微鏡 出典:Intelマレーシア工場

図13 不良解析を待つ300mmシリコンウェーハ;Core Ultraプロセッサ(開発コード:Meteor Lake)のマザーウェーハ(チップレットを搭載するための配線用シリコン基板)と思われる 出典:Intelマレーシア工場

Intelが、ベールに包まれていた後工程工場をここまでPC関連メディアに公開したのは初めてのことだという。EUVリソグラフィを初めて使用したAI機能搭載 PC用Core Ultraプロセッサ(12月発売予定)がなかなか発表されず、年内発売を危ぶむ声が上がっていたが、Intelは、12月14日の発売開始に向けて順調に組み立てられていることをアピールしたかったようである。

参考資料

1. 服部毅、「Intel最大のマレーシア後工程工場のクリーンルームに入ってきた!」、セミコンポータル (2023/09/26)

2. 服部毅、「12月発売予定のIntel Core Ultraプロセッサ組立・テスト現場を見てきた!」、セミコンポータル (2023/10/11)