AMAT、3D構造のFinFET、NANDフラッシュに向け新CMPとCVDを発表

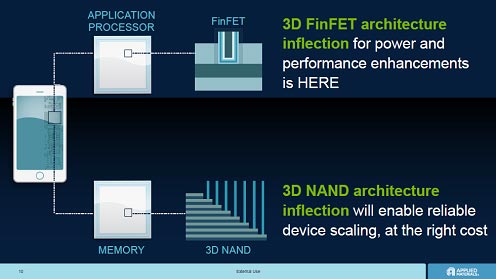

Applied Materialsは、ロジック向けのFinFETプロセス、メモリ向けの3D NANDフラッシュプロセスという大きな二つの3次元構造(図1)を実現するためのプロセス装置: CMP(化学的機械的研磨)とCVD(化学的気相成長)の新製品を発表した。

図1 スマホのキモとなる3次元構造デバイスFinFETと3D NAND 出典:Applied Materials

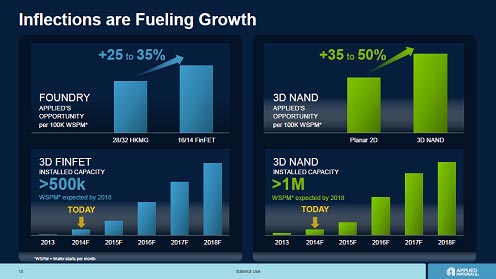

AMATは、これからの半導体市場を牽引するエレクトロニクスはやはりスマートフォンであり、その市場は2017年には70億台にも達する、と見ている。これを牽引する半導体チップはアプリケーションプロセッサとNANDフラッシュメモリである。どちらも3次元化する方向にある。アプリケーションプロセッサの最先端は20nmのプレーナプロセスであるが、その次の14/16nm世代はFinFET技術に行くと見る向きが多い。またNANDフラッシュは、メモリセルを横方向に作り込んできたこれまでのプロセスに対して、セルを縦方向に積むことで集積度を上げる方向に向かっている。Samsungは3D NANDを出荷しそれを使ったSSDを昨年すでに発表している(参考資料1)。今年は昨年の24層から、一歩進んで32層のメモリを開発している。このため、AMATは3次元構造を加工するための装置開発に力を入れてきた。この先もFinFETと3D NANDフラッシュ用ウェーハは増加していくとAMATは見ている(図2)。

図2 3D FinFETと3D NANDフラッシュのウェーハは増えていく 出典:Applied Materials

3次元構造を加工することは簡単ではない。FinFETでは原子層レベルの厚さの薄膜を形成しなければならない。そのための新CVD装置、Applied Producer XP Precisionは成膜の精度を上げ、材料の欠陥などの課題を解決するという。FinFETプロセスでは、10nm以降のトランジスタにはFinFETのチャンネルにキャリヤ移動度の高いIII-V化合物半導体を堆積させる技術を使うことになろう。このため、CVDエピタキシャル装置も欠かせない。装置の詳細は明らかにしていない。

NANDでは、60:1と極めてシャープなアスペクト比のコンタクト孔を加工し電極をつなげた後、CMPで平坦に加工する必要がある。CMP工程は、FinFETと3D NANDでは最大10工程も使われる可能性があるとする。今回AMATが発表したツールReflexion LK Primeには、6つの研磨ステーションと8つの洗浄ステーションを持つ。ナノメートル精度での3次元ゲートの高さ制御では、均一性が従来よりも50%向上したとしている。全14ステーションの工程を行うとして、従来機種と比べると、スループットは2倍に上がるという。

なお、AMATは今後統合する東京エレクトロンとの新会社の名前を「Eteris」にすると発表している。Eteris(エテリス)は、Eternal Innovation for Societyからきている。

参考資料

1. サムスン、3次元NANDを64個搭載したSSDを量産開始 (2013/08/15)