EB直描のeASICがTensilicaのプロセッサコアでSoCへ進出

1層のビア配線のマスクパターンだけを電子ビームの直接描画によりマスクレスでパターンを描くことを特長としてきた米国ファブレスeASIC社の短納期性と、Tensilica社Diamondファミリのコアの小さな面積を特長とする32ビットプロセッサを組み合わせることで、組み込みシステム設計者はDiamondベースのSoCをわずか4週間で製造できるようになる。

米国ファブレスのストラクチャードASICメーカーであるeASIC社は、プロセッサIPベンダーであるTensilica社とパートナーシップを結び、Tensilica社の標準的なプロセッサであるDiamondファミリのコアを組み込むことで、短納期の組み込みチップを提供できるようになる、と発表した。1層のビア配線のマスクパターンだけを電子ビームの直接描画によりマスクレスでパターンを描くことを特長としてきたeASIC社の短納期性と、Tensilica社の小さな面積を特長とする32ビットプロセッサを組み合わせることで、組み込みシステム設計者はDiamondベースのSoCをわずか4週間で製造できるようになる。

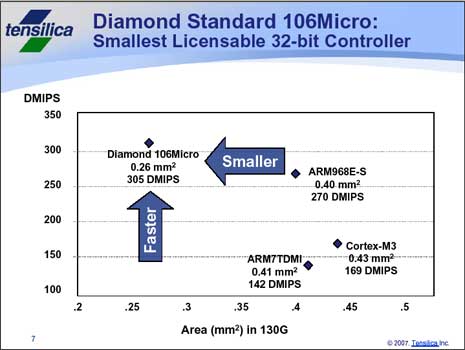

コンフィギュラブル・プロセッサのXtensaが有名なTensilica社であるが、今回提携したのは、コンフィギュラブルではないプロセッサコアで、面積の小ささを売り物にしている。130nm世代のプロセスで比較するとDiamondシリーズの中では最小面積の305DMIPSの32ビット・キャシュレスRISCである106Microコアの面積はわずか0.26平方mmしかない。

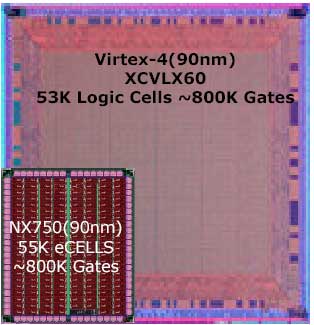

eASIC社がライバルと見るFPGAデバイスを、同じアルゴリズムと同じプロセスの条件で比べると、チップ面積は1/4程度になり、消費電力は1/10以下になるという。両者の発表では、ビデオ監視カメラへ応用した場合のデモを行い、FPGAによるシステムでは1.2Vで4.9Aの電流を消費したが、eASIC社のデバイスでは1.2Vで0.28Aしか消費しなかった。

eASIC社のマーケティング担当シニアディレクタであるJasbinder Bhoot氏によると、「これまでのストラクチャードASICはカスタム配線が数層にもわたり、微細化が進む時代には設計が難しくなり、EDAメーカーのツールの調整も必要になっていた。このため、ストラクチャードASICはすたれてきたが、eASIC社の手法はビア層1層だけを電子ビーム直描でカスタム配線する独自の方法なのでEDAツールによるDFMを取り入れる必要がなく、簡単に設計できる」としている。電子ビームの直描は富士通に依頼している。

eASICが最初から埋め込んでいるさまざまなIPコアはすべて検証済みで、シグナルインテグリティのチェックなどは不要だという。使えるTensilicaのプロセッサコアは106Micro以外では、以下IPがある;

108Mini:DSP機能を作り付けで持ちながらキャッシュレスの32ビットRISCコントローラコア

211GP:ミッドレンジの32ビットRISCコントローラコア

232L:LinuxOSをサポートするためMMU(メモリ管理ユニット)を搭載するミッドレンジの32ビットCPUコア

570T:ハイエンドの32ビットCPUコア

545CK:高性能のDSPコア

330HiFi:オーディオおよび音声コーデックをサポートしている低消費電力の24ビットDSPプロセッサ

これらはDiamondの標準的なソフトウエアツールを使え、Tensilicaの持つ業界の協力関係が既に構築されているため、設計のエコシステムができている。

Diamondが少ない面積でプロセッサ機能を持てるのは、よく使う16ビットおよび24ビットの命令セットだけに絞り、コード効率を上げたためだとTensilica社マーケティング担当バイスプレジデントのSteve Roddy氏は説明している。

関連記事:

・65nm以下のEB直描に賭けるイー・シャトル 2007年10月 9日

・Xilinxが32ビットプロセッサの開発システムをIPまで含めて一式サポート 2007年11月26日

・マルチコアよりマルチスレッドで性能を上げながらシリコン面積を削減 2007年11月 8日