マルチコアよりマルチスレッドで性能を上げながらシリコン面積を削減

英Imagination Technologies社は、少ないチップ面積で性能を高め、DSPコアまでも内蔵したマルチスレッドプロセッサIPコアMETAの新バージョンの開発を終え、ライセンス供与活動を開始した。SoCに搭載することを狙い、小さなチップ面積でマルチコアと同等の並列性を持つIPにしたことが特長である。65nmプロセスで製造すると700MHz動作で最大1552DMIPSという性能が得られる。

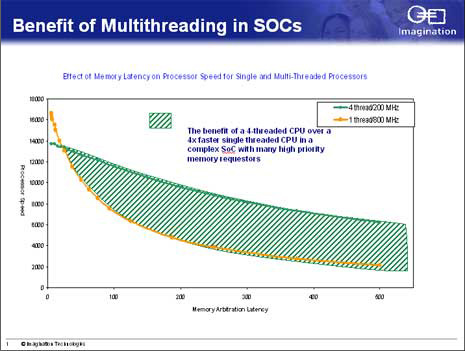

SoCに搭載するIPコアとしてシングルスレッドコアプロセッサだとミスヒットしたときのレイテンシが長ければ性能はとたんに低下するが、マルチコアやマルチスレッドだとレイテンシが長くかかっても性能の低下はシングルスレッドコアよりも少ない。シングルスレッドで800MHz動作と4スレッドで200MHz動作を比べると、メモリーのレイテンシがゼロだともちろん800MHz動作の方が早いものの、150サイクル後だと4スレッド200MHz動作のほうが約2倍速く、300サイクル後だと3倍、500サイクル以上では4倍以上速い。

このIPの対象はあくまでもSoCへの組み込みであるため、ミスヒットでも性能の落ちないリアルタイム動作が可能な応用に向く。SoC用途ではCPUコアの面積はできるだけ減らしたい。マルチコアはコアを4個必要とするが、マルチスレッドはコアが1個ですむためチップ面積は小さくなる。

マルチスレッドは4個のバーチャルプロセッサを搭載したものに近く、外部から見てそれぞれ独立した動作が可能である。各スレッドはRISCコアかDSPになり、それぞれ別々のOSで動くこともできるという。組み込みLinuxやNucleus、Imagination社独自のMeOS リアルタイムOSなどを各バーチャルプロセッサに組み込むことができる。このマルチスレッドプロセッサ実現のカギは、ハードウエアスケジューラにある。クロックごとにタスクを自動的に振り分けている。

性能的にはパイプラインの長さを変えられるような柔軟性があり、単純な演算はすぐに終わらせるようにしている。またパイプラインの中で、桁上げセーブ演算を利用できることも高速化に貢献している。DSP部分は、1クロックあたり16ビットMAC演算を4個あるいは32ビットMAC演算を2個並列に処理できる。複雑なDSP演算に対しては、1サイクルあたり4つの命令を発行する仕組みを利用してVLIW的な命令を実行する。

新しいMETA2は、これまでのMETA1のコード互換性を持ちながら、クロックの高速化に対応している。またMETA1では32ビット命令だけだったが、META2では16ビット命令も追加した。32ビット命令はDSPによく使い、CPUには16ビットを多用することで、ARMのThumbアーキテクチャのようにコード効率を上げた。

クロック速度は、プロセスに依存する。TSMCの130nmプロセスでは360MHz、90nmプロセスでは500MHzで動作する。低消費電力版だと、同一プロセスで周波数は1/2〜1/3に低下する。METAアーキテクチャは合成可能であるため、レイアウトツールを手動で調整しなくても高いクロック速度を得られる。すでにデバッグツールも入手できる。