未来車載コンピュータ向けLPDDRのNORフラッシュ、Infineonがサンプル出荷

クロックの立ち上がりと降下でトリガーをかけるLPDDR(Low Power Double Data Rate)技術は、これまでDRAMの高速化技術であった。これを高速アクセスに使ったNORフラッシュメモリをInfineon Technologiesが開発、サンプル出荷を開始した。狙いは車載コンピュータのリアルタイム動作である。LPDDR4のDRAMと比べ読み出しアクセス時間が10nsと5倍速いという。

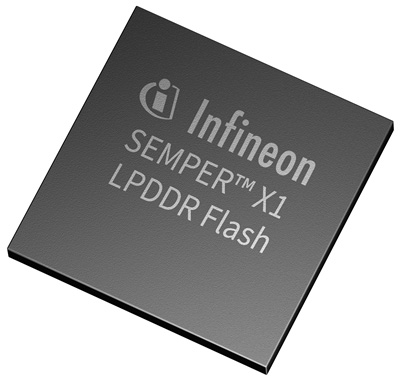

図1 Infineonが出荷したLPDDRインターフェイスのNORフラッシュ 出典:Infineon Technologies

InfineonのNORフラッシュは、買収したCypressが持っていた製品ポートフォリオ。Cypressの前は、AMDと富士通の合弁会社Spansionが開発していたが、今回のSEMPERシリーズはCypressが開発してきた。

NORフラッシュはもともと携帯電話のBIOSやデータストレージとして使われていたが、微細化しにくく集積度を向上させられなかったため、大容量ストレージ用途ではNANDフラッシュの後塵を拝した。しかし、動作速度はNORの方がNANDよりも速く、しかもDRAMと違って不揮発性である。このためNORフラッシュの位置づけは、高速で不揮発性、すなわち超低消費電力だった。NANDと比べ十二分に速いため、メモリセルは並列のNORでありながら、読み出しにはSPIなどのシリアル方式を使っていた。

図2 リアルタイムプロセッサにはNORフラッシュのLPDDR方式は最適 出典:Infineon Technologies

ここにきて、ソフトウエア定義(Software-Defined Vehicle)の未来のクルマや、ADAS(先進ドライバー支援システム)、自動運転などリアルタイム動作がクルマに求められるようになってきたため、今回のLPDDR NORフラッシュの開発となった。クルマ用途では、フラッシュマイコンがよく使われているが、容量増加には限界がある。そこで、組み込みフラッシュを1チップに集積せず、リアルタイムプロセッサと別チップでLPDDRインターフェイス接続する方式に移行するとInfineonは見ている(図2)。

開発されたSEMPER X1は、フラッシュマイコンのチップ内に集積するのではなく、外部メモリとしてLPDDRインターフェイスを通してメモリをアクセスする。今回のサンプル出荷には288Mビットと576Mビットの製品がある。×9構成なので、誤り訂正用のビットを追加した構造になっている。しかも、読み出しのアクセスは従来の200ns以上あった従来のSPIインターフェイスと比べ、わずか10nsと20倍も高速になった(図3)。また、バンド幅は3.2Gbytes/sと従来のxSPI NORと比べて8倍速い。

図3 読み出しアクセスはSPIインターフェイスより格段に高速 出典:Infineon Technologies

DRAMと比べてもリフレッシュやプリチャージするための時間が不要なため、5倍高速だとしている(図4)。従来のLPDDR4 SDRAMでは50nsの読み出しに対して10nsしかないからである。リフレッシュが不要であることはデータバスの利用効率も上がる。LPDDR4では87%のデータバス効率を99%にまで高めた。

図4 LPDDR DRAMと比べてもNORフラッシュの読み出しは速い 出典:Infineon Technologies

メモリアーキテクチャとしては、8バンク方式のセルアレイにLPDDRインターフェイスを付けた×16ビット出力方式。メモリセルは従来の電子トラッピングを利用するMNOS構造のMirrorBit方式(生まれながらに2ビット/セル)を使いながら、選択トランジスタを1トランジスタではなくスプリットゲート方式で1.5トランジスタを使うとしている。セルの規模はやや大きくなるが、速度は上がるとしている。メモリチップは45nm CMOSプロセスで、ファウンドリUMCのシンガポール工場で製造している。