高NA EUVリソグラフィ装置第1号をIntelオレゴン工場に導入、組み立てた

Intelは1.8nmプロセスノードに相当するIntel 18Aに向け、オランダASML社製の高NAのEUVリソグラフィ装置「TWINSCAN EXE:5000」(図1)をプロセス開発拠点のあるオレゴン工場に導入した。まずIntel 18Aプロセスノードから導入し、Intel 14Aノードへと拡張していく予定だ。Intelのファウンドリ事業部が導入しTSMCに追いつき追い越す計画を進める。

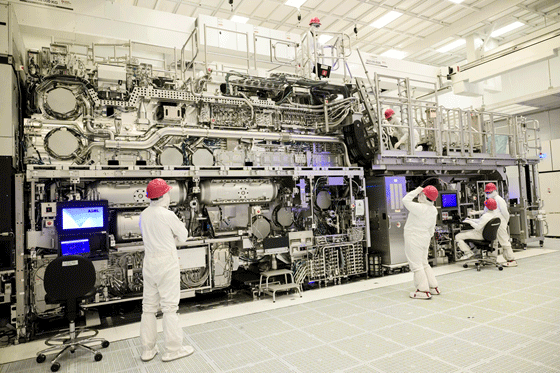

図1 ASML最新の高NA EUV装置「TWINSCAN EXE:5000」 出典:ASML

これまでのEUV露光装置としては、2017年にNA(開口数:Numerical Aperture)が0.33の第1世代の量産機「NXE:3400」と2020年に「NXE:3600」をIntelは導入してきた。EUV開発責任者で、Intelのフェローであり、Intel Foundry Logic Technology DevelopmentのLithography , Hardware and SolutionのディレクタであるMark Philips氏(図2)は、EUVのような短波長の軟X線リソグラフィを27年間開発してきたという。IntelはEUVの実績が20年以上あると強調する。

図2 Intelフェロー兼、Intel Foundry Logic Technology DevelopmentのLithography , Hardware and SolutionのディレクタMark Philips氏

今回の新製品はNA0.55となり、シングル露光で8nmハーフピッチのパターンを加工できる。現在、3nm、2nmノードといっても実寸法は12nm程度のままである。さらにEUVを使っても3nmくらいになると、ダブルパターニング露光が必要になりつつある。NAが0.55となるとシングル露光が可能になるため、マスク数を減らすことができるようになる、とPhilips氏は語っている。

現実にASMLはフルフィールドで10nmサイズのパターンを実現しており、NA0.55の道筋をつけたと同氏は述べている。ASMLはパートナーであるZeissと一緒に高NA EUV装置の光学系を設計したという。

ただ、10nmパターンをこの第2世代のEUVリソグラフィ装置で切るといってもミッションクリティカルなスイートスポットで高NA装置を使うことになるだろうとPhilips氏は述べている。10nmのパターンとなれば、フォトレジストも10nm以下に薄くする必要がある。レジストと欲しいパターンとのアスペクト比が高くなることを考えれば、メトロロジー技術での正確な寸法を測定する技術も重要になる。2nmプロセスノードは、露光装置だけではなく、レジスト、塗布装置、現像、エッチングを含めたリソグラフィ総合力が問われるようになりそうだ。

米オレゴン州ポートランド近郊のヒルズボローにあるIntelのオレゴン工場では、オランダから空輸で高NA EUV装置を搬入してきており、その様子をYouTubeで公開している(参考資料1)。オランダで製造しているEUV装置を250木箱に分解し、43個のコンテナを貨物専用機に搭載してオランダからシアトル空港まで運んだ。大型トラック20台分に分けて空港からIntelのオレゴン工場まで搬入した。

図3 個々のモジュールに分解、それぞれをテスト可能にしてオランダから搬送したブロックをオレゴンで組み立てた 出典:Intel

各モジュールはオレゴン工場内で組み立てた(図3)。それぞれのサブシステムはテスト可能なモジュールに分解され、それぞれをテストできるようにしている。主要なモジュールとしてはレチクルモジュール、光学系モジュール、ウェーハを搭載するウェーハモジュール、レーザー駆動装置、光源モジュールなどがある。さらにスループットを上げるためのTWINSCANステージ技術や、微細加工に不可欠で焦点深度を深くするアナモフィックな反射系光学モジュールなどを組み立てていく。

参考資料

1. "Intel Adds ASML’s First High NA EUV Tool to Oregon Factory", YouTube