Western Digital、ライセンスフリーのCPUコアRISC-Vへ全面切り替え

Western Digitalが自社で設計しているICに集積されているCPUコアを従来のコアから、ライセンスフリーのRISC-Vコア(参考資料1)に全面的に切り替えていく、と同社CTOのMartin Fink氏(図1)が語った。従来のArmやMIPSなどのCPUコアはライセンス料およびロイヤルティ料がかかる。RISC-VはUC Berkeleyが開発したコア。

図1 Western Digital CTOのMartin Fink氏

Western Digitalは東芝メモリのプロセス協力会社として有名だが、元々はHDD(ハードディスクドライブ)を生産販売してきた。2016年に東芝と共同でNANDフラッシュメモリを開発していたSanDiskを買収し、日本の半導体業界で一躍有名になった。今はSSD(半導体ディスク)も生産しており、HDDとSSDの両方でビジネスを展開している。HDDやSSDでは、読み出しチャンネル用のASICやNANDフラッシュコントローラなどの専用のICが必要で、WDはこれまで10億個のCPUコアを搭載したICを出荷してきたという。今後もストレージデバイスは、ますます伸びてゆき、時期は明確に言わなかったが、いずれ20億個に達するだろうとFink氏は述べている。

WDがRISC-Vコアに切り替えようとしている背景には、大量のデータを扱う時代が来ることを想定していることがある。これまでの紙ベースの記録データから、電子メールの通信データに代わり、これからはデータを活用して生産や生活の効率を上げたり、データをビジネスとしてマネタイズしたりすることになる。ストレージやメモリは今後もますます必要になることは間違いない。WDのストレージデバイス用コントローラASICはあくまでも社内向けのチップであり、IPコアもチップも外販しない。製造はTSMCとGlobalFoundriesに委託している。

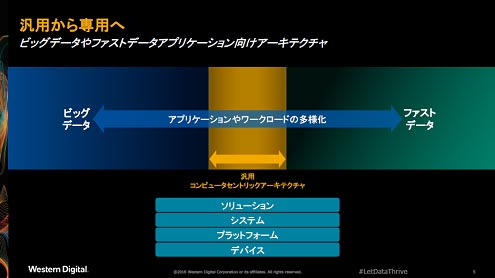

WDはデータを2種類に分け、大量のビッグデータと、高速にアクセスしたいファストデータ(Fast data)に展開していくとした。これまでは、コンピュータシステムのメモリ階層から構成されるコンピュータセントリックなアーキテクチャであったが、これからは二つの両極端のメモリ応用へと広がっていくとする(図2)。

図2 データは汎用から、大規模・高速の両極端に展開されていく 出典:Western Digital

これをFink氏は、乗り物に例えて、汎用アーキテクチャだと4ドアセダンのようなもので、ビッグデータは大型貨物輸送船や貨物列車だとし、ファストデータはロケットやパーソナルジェット機、新幹線のようなものだとした。つまりさまざまな乗り物が共存しているようにストレージデバイスも従来の専用のHDDやSSDからビッグデータやファストデータに向いたストレージへと展開されていくとしている。確かに、金融市場ではHDDでは遅すぎて高速取引に向かないからとしてSSDへ向かっているが、全てSSDの代わるわけではない。大量のデータはHDDやデジタルテープの方が保存に向いている。

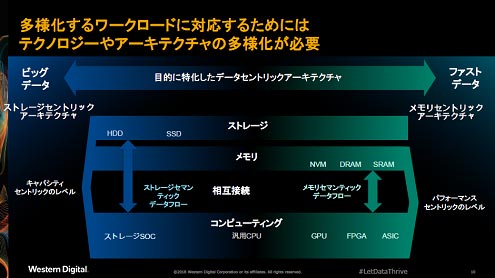

ファストデータは、ストレージ半導体ではなくメモリとして、絶えず書き換えるRAMを想定している。DRAM、SRAM、不揮発性RAMなどがファストデータを支える(図3)。こういった広い範囲の「データセントリックなアーキテクチャ」がこれからの新しいコンピュータシステムを作るだろうとみている。

図3 ストレージはビッグデータへ、メモリはファストデータへ 出典:Western Digital

当面の応用として、ビッグデータには分析や機械学習に使われ、ファストデータはブロックチェーンやセキュリティ検出、イベント相関などの応用を想定している。コンピュータシステムをこれから拡張していくうえで、「オープン性」が必要とみており、CPUコアとしては汎用のIntelやArmではない、第3のコアで育てていく、と考えている。RISC-Vのパートナーシップの組織として、LinuxやTensorFlow、Hadoopなどの団体がいる。

ライセンスフリーのRISC-Vは大量・高速の専用的なCPUアーキテクチャとして使われるものであり、汎用のアーキテクチャにとって代わるものではない、とFink氏は見ている。例えば、機械学習や分析ではプロセッサをデータの近くに置く。これまではデータをプロセッサの近くに置くようにしてきた。ディープラーニング向けのAIチップでは、1チップ内に多数のAIブロックを構成し、その各AIブロックはCPUとメモリを近くに配置するレイアウトが多い。ニューラルネットワークでは、データ×重みの計算を並列にマッシブコアで行うことが多いからだ。今後のAI普及に向けた専用チップにはRISC-Vが向くとみている。

UC BerkeleyがRISC-Vを開発した意図は、Armと対抗するためではなく、CPUでもIntelのx86系とArmのコアとではISA(命令セットアーキテクチャ)が異なるため、一緒に乗せられないことに対する不満を解決するためであった、と2017年12月に来日したUC BerkeleyのKrste Asanovic教授は語っている(参考資料2)。これからは、1チップSoC上にCPUもGPUもDSP、ISPなど様々なプロセッサを集積する半導体チップが増えていくため、そのためにも一つの共通となるISAが必要となると述べていた。

図4 RISC-V Foundation加盟社数は2年前の3倍に 出典:Western Digital

RISC-Vコアを普及させるための団体、RISC-V Foundationの参加メンバーは2016年9月時点での40社から現在129社に増え、その数は増加中だという(参考資料1)。代表的なメンバーには、GoogleやNvidia、IBM、Qualcomm、Tesla、NXP、Samsung、Micron、Siemensなどのビッグネームがズラリと並んでいる(図4)。

参考資料

1. 半導体のLinuxになるか、フリーのCPUコアRISC-V (2016/09/06)

2. 半導体プロセッサメーカーが集結した師走(IoT/セキュリティ編) (2017/12/22)