半導体プロセッサメーカーが集結した師走(IoT/セキュリティ編)

師走に代表的なプロセッサメーカーのイベントが続々開かれた。後半では、IoTの未来をQualcomm、Arm、そして無料のCPUコア、RISC-Vの動きを紹介する。QualcommはIoTの未来を単なるコネクティビティから賢さとセキュリティも加わるとし、Armはセキュアフレームワークを紹介した。無料のCPUコアRISC-Vのツールも揃いつつある。

図1 Qualcomm社IoT部門製品マネジメント担当SVPのRaj Talluri氏

Qualcommは、IoT部門製品マネジメント担当のVPであるRaj Talluri氏(図1)が5G時代のIoTについて語り、今後のIoTには賢さが加わることでクラウドに頼るだけではなく、エッジも賢くすることにより、クラウドをストレージとして利用し、エッジで演算をするようになるとみている。それは次世代のモバイル通信技術5Gとも関係する。5Gでは信号の遅延(レイテンシ)を1ms以内に抑えるリアルタイム性能も要求仕様の一つである。5G時代のIoTシステムにはレイテンシを抑えるためにエッジで演算し賢くするというのである。さらにセキュリティの確保もある。

エッジのIoT端末が賢くなることをオンデバイスインテリジェンスと呼び、スマートホームをはじめとする民生IoTから工業用IoT、ネットワーキング、コンピューティング、クルマへとさまざまな業界へと広がるとして、クルマやスマートホームでの利用シーンを紹介した。例えばクルマでは、ドライバー個人ごとの設定を行い、ドライバーが眠らないように常にモニターしておく、自律運転の能力を高める、などの機能を持たせることができる。

スマートホームではすでにAIスピーカー(米国ではデジタルアシスタントと呼ばれている)が登場してきているが、さらに音声認識、顔認識、自然言語処理、音を検出して行動パターンを先読みするコンテクストアウェアネスなど新しい機能をエッジ側で加えることで、リアルタイム応答が可能になる。AIスピーカーだけではなく、ウェアラブルデバイスやスマートフォンなど他のIoTとの連携が可能になると予想する。

図2 IoTのセキュリティもスマホで使ってきた技術を盛り込む 出典:Qualcomm

セキュリティに関しても、起動時のセキュアブートをはじめとして、セキュリティをかなり確保した環境を作るとする(図2)。データを暗号化し、解読するためのカギにも暗号をかけ、スマホで行ってきたセキュアな手段はすべて盛り込むとしている。

こういった将来のIoTに関してもSnapdragonでデバイスを揃えていく。オンデバイスインテリジェンスを実現するために必要なヘテロジニアスコンピューティング(CPUやGPU、DSP、IS、デジタルモデムなど各種各様のプロセッサを集積したSoC)技術の性能や効率を上げていく。

Armはセキュリティに指針

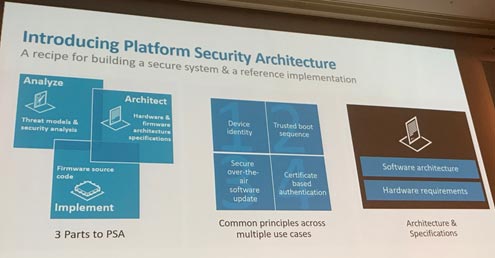

QualcommのSoCに使われるCPUコアはArm Cortex Aシリーズが多い。Armは汎用のコアのセキュリティを確保するために、新しいセキュリティの仕組みとなる「PSA(Platform Security Architecture)」を発表した。IoTのように全てのものがクラウドにつながるようになると、サイバー攻撃に対するセキュリティを確保することがマストになる。PSAはArmが提唱したIoT向けのセキュアなプラットフォーム仕様で、クラウド業界や電子機器、半導体などの業界で支持されているという。

Armはこれまで、セキュアな部屋(コンテナ)とセキュアではない部屋を分けるTrustZoneを10年以上前に発表したあと、CryptoIslandや、CryptoCellなどのセキュリティIPを2015年以降に発表していた。CryptoIslandは、演算エンジンや暗号機能、暗号鍵などの管理と、ICカードレベルのセキュリティを1チップ上に実現する目的のIPで、CryptoCellはハードウエアアクセラレータやハードのRoots-of-Trust制御(暗号化処理の一つ)と、豊富なセキュリティソフトウエアやツールを組み合わせたもの。今後、IoTが1兆個つながるような世界を見据えると、オプション的にセキュリティIPをリリースしていくことではもはや対応できなくなるとArmは考えた。

そこで1兆個のIoTをつなげても対応できるような新しい仕組みとして、PSAを発表した(図3)。ここでは、バリューチェーン全体に渡るセキュリティや、最小の大きさで低コストのデバイスにも広げられること、デバイスのセキュアな接続と管理、に関して基本的に見直した。その結果、小型になってもIoT接続のセキュリティを確保できる共通フレームワーク、業界リーダーからの広いエコシステムのサポート、Trusted Firmware-Mと呼ぶオープンソースのリファレンスファームウェア、の三つを基本機能とする。また、セキュアなシステムを構築するうえでの新しいシリコンIPとして、分離されるArm CryptoIsland-300とセキュアなデバッグチャンネルを通すArm SDC-600も発表している。

図3 PSAの基本3パーツ

PSAの基本パーツは3つあり、それぞれ分析、構築、実装からなる。分析では脅威となるモデルを構築しセキュリティに分析を行う。構築(アーキテクト)では、ハードウエアとファームウエアのアーキテクチャの仕様を定める。実装(インプリメント)では、ファームウエアのソースコードが提供される。さまざまな利用シーンに対して共通の原理は、デバイスのID(同定)や、信頼のおけるブートシーケンス、セキュアな無線通信によるソフトウエアの更新、3者間による認証だとしている。

Trusted Firmware-Mの特長は、PSA仕様に準じるArm認証のファームウエアであること、早い採用ができるようなオープンソースなライセンス、無料で入手可能なリファレンスの実装などであり、当初の目標をArmv8-MベースのSoCにしている。組み込み系のArm Mbed OSは、すべてのCortex-Mデバイスに対してPSA実装を提供する。

RISC-VはISAを標準化することが狙い

ライセンス料無料のCPUコアであるRISC-V(リスクファイブと発音)の現状を伝える日本で初めての会議「RISC-V Day 2017 Tokyo」が12月18日に開催された。これまで、CPUコアのライセンス料金は高いという声をマイコンやSoCの小規模な開発企業から聞かれた。このため、Armとの対抗策、あるいは無料のOSであるLinuxのCPUコア版という位置づけでRISC-Vを見る向きが多かった。

図4 UCバークレイのKrste Asanovic教授

ところが、RISC-Vアーキテクチャを考案した米UCB(カリフォルニア大学バークレイ校)のKrste Asanovic教授(図4)は、考案した意義を、最近のSoCがCPUやGPU、DSP、ISPなどさまざまなプロセッサコアを集積するようになり、異なるISA(命令セットアーキテクチャ)を使うようになったためだと説明している。これまでArmアーキテクチャもIntelのX86アーキテクチャもそれぞれ異なり、共通のISAは存在しなかった。

RISC-Vでは、複雑なSoCには単純で共通に使えるISAで統一しよう、という発想が基本にある。まずCPUのISAを簡単にしてGPUやDSPにも使えるように共通化しようとしている。これまでのISAよりもずっと小さく、マイクロアーキテクチャやテクノロジーに依存する特長を設けない。しかも拡張できるいくつかの標準仕様を用意する。基本ISAや拡張標準は固定され、追加やオプションは用意しない。

Asanovic教授が掲げるRISC-Vの特長は4つある;

1)UCバークレイが開発した、高品質・ライセンスフリー・ロイヤリティフリーのRISC ISA仕様

2)非営利団体のRISC-V基金によって標準化が維持される

3)マイコンからスーパーコンピュータまで全てのコンピュータに向く

4)数々の独自でオープンソースのコアがある

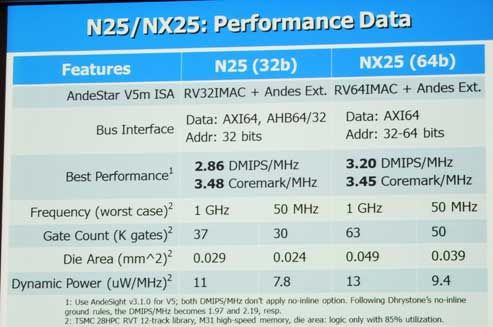

図5 Andesの64ビットCPUコアの性能

RISC-Vコアを使ったSoCはすでに3社が試作している。中でもSiFive(サイファイブと発音)は2016年11月に「FE310」SoCを提供すると共に、命令セットシミュレータ・エミュレータやEclipseベースの開発環境、リファレンスデザインボードなどを提供する。2005年に創立された台湾のAndes TechnologyのNX25チップは64ビットアーキテクチャながら、TSMCの28nmプロセスで1GHz周波数で動作する63kゲートのSoCで、そのチップ面積は0.049mm2しかない(図5)。ダイナミック電力は13μW/MHzと小さい。1GHzで13mWに相当する。

また、Asanovic教授がCTOを務めるEsperanto Technologies社は、7nmプロセスを使った高性能64ビットRISCチップを開発中だとしている。Esperantoは、かつてTransmeta社を設立し日本でもなじみ深いDave Ditzel氏がCEOを務めている。