Lattice、センサ信号処理を見越しFPGAにもDSPを4個搭載

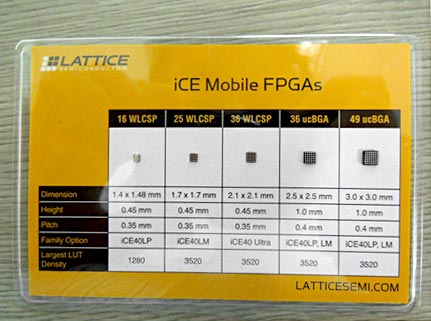

Lattice Semiconductorは、スマートフォンやタブレットなどの機能を簡単に増強するためのFPGAを開発してきた。今後のスマホに搭載するセンサの数が爆発的に増えることを見越して、センサ信号処理用DSPを4個集積したFPGAであるiCE40 Ultra(図1)を製品化した。

図1 Latticeの小規模FPGA、iCE40シリーズ 新製品は真ん中のUltra

Samsung Galaxyシリーズなどで代表されるように、Samsungが1年に数機種ものスマホを製品化できるのは、Latticeなどの小規模なFPGAを用いて新機能を追加しているからだ。アプリケーションプロセッサを作り直すのなら3〜4年かかるため、アプリケーションプロセッサは既存のまま、新機能だけをFPGAのロジックで実現する。Latticeはやはり小規模なFPGAメーカーのSilicon Blue社(参考資料1)を2011年に買収したが、このSilicon Blueこそ、Samsungが次々と新機種を出すための原動力となっていた。

今回、Latticeは、このiCE40 Ultraを単なるLUT(ルックアップテーブル)とSRAMだけのFPGAではなく、これまでの経験から必要とされた機能をハードマクロでも集積した。乗算器・加算器、大電流シンク、中電流シンク、オシレータ、標準I/Oインタフェースなどである(図2)。FPGAのロジック規模は最大3520個のLUT。

図2 多彩なハードマクロを搭載したFPGA 特に4個のDSPはセンサ時代に備えた 出典:Lattice Semiconductor

図2の24mA定電流シンクはR(赤)G(緑)B(青)3つのLEDをドライブするための回路であり、1本の500mAという大きな定電流のシンクは赤外線リモコンに使うための電流源だ。500mAで駆動すれば10m程度の距離も赤外線を飛ばせるとしている。

特筆すべきは、4個の16ビット×16ビット乗算器と32ビットの加算器を、集積したこと。DSPとしての積和演算はもちろん、乗算、加算別々でも計算できる。この機能は特にセンサからの出力信号を処理した後に演算することが目的。信号処理に従来のLUTを使うなら回路規模が大きくなりすぎるため、専用の乗算・加算器を集積した。次世代のスマホに搭載される機能にはヘルスケアや位置検出などがあり、そのためのセンサを多数使うと言われており、それに対応したもの。センサ情報を処理している時にアプリケーションプロセッサは休止させ消費電力を削減できる。

さらに、スマホやタブレットの消費電力を削減するため、48MHzの内部発振器に加え、10kHzという低周波の発振器も備えており、クロックゲーティングに対応する。シリコンに集積された発振器であるため、精度はそれほど高くはないが、外部回路のクロックとして使い、システム全体の電力を減らすこともできる。

図3 加速度計をウェアラブル機器(開発ボード)に搭載して歩数計に応用した例

歩数計を身に着けながら、スマホで歩数を観測するデモを示した。実際に、開発ボードを携帯用の機器に取り付け、スマホへBluetooth Smartでデータを送る。図3の開発者が左手に持つ開発ボードに歩数計を組み込み、右手のスマホでデータを受け取る。左手を縦に振ると歩数をカウントする。このスマホでは見づらいが59歩を示している。この歩数計の精度を上げるため、加速度センサは上下方向には感知するが、横方向の動きには反応しない。誤った動きを歩数としてカウントしないように設計しているという。

iCE40 Ultraは、同じようなロジック規模で従来のiCE40 LP(図1の右から2番目)と比べると消費電流は360µAから1/4の90µAに削減している。プロセスノードは40nm、ウェーハレベルCSPパッケージ封止。ロジック回路や乗算器の係数プログラミングなどの開発ツール、iCE Cube2 ver.2-14-04最新版を無料でダウンロードできる。

参考資料

1. スマホやタブレットの新機能追加をFPGAでサポートするシリコンブルー (2011/07/19)