2極化するFPGA業界、ザイリンクスとアルテラの2強はハイエンドへ

FPGA業界は2極化が顕著になりつつある。2強と言われる米国のザイリンクスとアルテラは大規模化を追求すると共に下位の用途にも広げつつある。一方で、ゲート数の少ないローエンド市場が意外と大きいことがわかり、この市場に目を向ける動きが顕著になってきた。マーケット指向に徹すれば日本の半導体メーカーが入り込める余地は十分にある。

図1 Xilinxの共通プラットフォーム

FPGA市場のトップを行くザイリンクス社は、2大製品シリーズであるSpartanとVirtexを共通のプラットフォームで設計する手法を進めているが、これまでは6シリーズの製品に適用していた(参考資料1)。このほど28nmプロセスをベースにする7シリーズをリリースし、ハイエンドのVirtexからミッドレンジのKintex、ローパワーのArtixという三つのシリーズを揃えた。プログラム可能な論理回路やソフトウエアサポート、IPサポート、プロセス技術は共通で、違いは規模や回路構成だけだ(図1)。共通化することで開発スケジュールは33%短縮し、開発コストは20%低減した。

Virtex-7は400Gbpsという超高速のネットワーク機器や高度なビデオ機器や軍用レーダーなどの分野、Kintex-7はマルチモードのLTEや医用画像、通信インフラなどの分野、Artix-7は小型超音波診断装置やモーター制御などの分野を狙う。FPGAはさまざまな分野に使えるとはいうものの単体で使うほど安くはない。FPGAはSoCやシステムLSIを設計した後に論理を検証するブレッドボード代わりのロジックを組むのに使われることが多い。そのようなシステムLSIの分野が上で述べた分野である。FPGAをデバイスとして用いられることはあまりない。デバイス単価が高いからである。

そこで、ザイリンクスはARMのCortex-A9のデュアルコアやいくつかのIPと7シリーズのFPGAを集積したSoCとも言えるZynq-7シリーズも発表した。これはカスタムSoCという位置付けでASICあるいはASSP的な製品といっても差し支えない。カスタマイズしたいロジック部分だけをFPGAとして載せており、これまでのブレッドボード代わりのFPGAではなく、そのまま装置に組み込むSoCになる。量産時の単価は15ドルからを予定しており、100万個程度の車載ドライバ支援システムやサーベイランスシステム、50万個程度のファクトリーオートメーションなどの用途に使えると見ている。

ザイリンクスはさらに微細化すべき20nmプロセスの7シリーズの開発を開始した、と同社WWマーケティング担当シニアVPのVincent Ratford氏は言う(図2)。

図2 Xilinx社WWマーケティング担当シニアVPのVincent Ratford氏

FPGAはSoCのブレッドボード代わりではない用途では、SerDes(直並列変換:シリアルデータをパラレルデータに変換、あるいはその逆)として使われることが多い。特に最近では装置から装置への接続には何百本、何千本というケーブルを嫌い、1本のケーブルで大量のデータを送受信する高速シリアルインターフェースがさまざまな機器に使われるようになってきた。そのためのインターフェースで使われるのがSerDes(サーディスと発音)回路である。

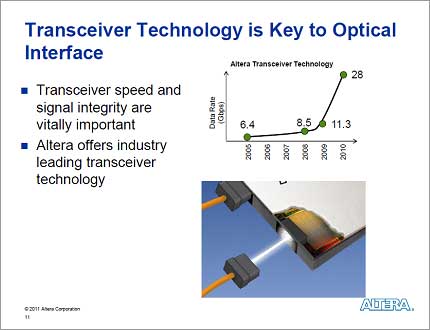

アルテラは、SerDesを通った後の伝送ケーブルとして、従来の銅線ではなく光ファイバを使えるようにしたFPGAに力を入れている。同社ICエンジニアリング担当VPのBradley Howe氏(図3)には、「28Gbpsを超えるような高速の要求にはバックプレーン上の銅線で高速伝送を実現することはDFE(differential feedback equalization)を使っても難しくなる」と述べている。

図3 アルテラ社ICエンジニアリング担当VPのBradley Howe氏

このためアルテラは、従来の11Gbps製品では銅線コネクタの製品を設計してきた。ユーザーはFPGAによる11GbpsのSerDesを束ねて100Gbpsのシステムを作っていた。近年の通信トラフィックの増大に対処するため通信インフラを手掛けるユーザーは、次世代の通信インフラ装置として400Gbpsのデータレートを要求するようになってきた。米シスコシステムズ社の予測によると、2009年から2014年までのインターネットバンド幅は年率平均(CAGR)36%で高速になる。

400Gbpsシステムを実現するために1チップのSerDesは28Gbpsというデータレートが必要になるとして、光コネクタを利用することをアルテラは決めた。光伝送だと数百メートルはカバーできる。光伝送の媒体としてはプラスチックやガラスがあるが、顧客の要求によって媒体を決めるとしている。

このFPGAには光回路も1パッケージ内に集積している。例えば、送信側はTOSA(transceiver optical sub-assembly)、受信側にはROSA(receiver optical sub-assembly)のような光回路を1パッケージ内、あるいは1チップ上に集積していれば個別部品によるモジュールがなくても装置間を接続できる。IC間は光ファイバだけでつなぐことができる。もちろん、この光回路はシリコンではなく化合物半導体を利用している。

図4 高速SerDes間の伝送には光ファイバがカギとなる 出典:Altera

Howe氏によると、40Gbpsでも光を使えば実現は近い。プロセス技術としては28nm製品を2010年第4四半期にテープアウトし、2011年第1四半期に出荷している。さらにその先の20nmプロセスのテストチップも設計に入っている。

参考資料

1. ザイリンクス、Spirit仕様をベースにした共通開発プラットフォームを開発中 (2009/02/16)