IBMと東京エレクトロンが共同開発した3D-ICウェーハスタック技術

IBM Researchは、東京エレクトロンとパートナーシップを結び、米ニューヨーク州のアルバニーにおいて共同で300mmウェーハ同士を接着するための3D-ICスタック技術を開発したとブログで明らかにした。3D-ICは、TSV(through silicon via)技術で2枚以上のウェーハ同士を接続して3次元的に集積する技術。薄いウェーハを容易に取り扱えるようにした。

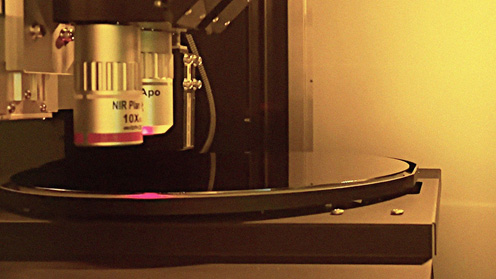

図1 薄いウェーハを容易に取り扱えるようにした 出典:IBM Researchブログ

TSVは、チップ同士(ウェーハ同士)を重ねて配線をつなぐ技術であるが、配線距離を短くするために裏面を薄く削っている。その厚さは100µmにも満たない。生産工程で薄く削ってしまうと、ハンドリングが難しく割れやすくなってしまう。このため、キャリアウェーハに接着させて取り扱う。これまでキャリアウェーハは、シリコンウェーハを扱うためにガラスウェーハに一時的に張り付けて使っていた。ウェーハ処理が終了すると、紫外線レーザーを照射しガラスとウェーハを外していた。

キャリアウェーハとしてシリコンを用いる場合もあったが、機械的な力を加えて2枚のウェーハを切り離していたため、欠陥が発生し歩留まりを低下させる原因になっていた。

そこで、IBMと東京エレクトロンは、従来のガラスウェーハに代わり標準的なシリコンウェーハを用いても簡単に2枚のウェーハを分離できる方法を共同開発した。シリコンには透明な赤外線レーザーを使って、300mmウェーハを分離する方法だという。この方法を使えば、装置の互換性や真空チャックの問題がなくなり、欠陥を減らし、異なるウェーハ同士に関係するプロセス上の問題もなくなるとしている。今回の技術は、FOWL(Fan out wafer level packaging)や3Dチップレットなどの先端パッケージ技術に使える技術だという。

IBM Researchは2018年以来東京エレクトロンと共同開発してきており、レーザーによるウェーハ分離技術を完成させることを目的としてきた。新しいチップ製造のために必要な製造装置を開発してきた東京エレクトロンは、量産向け300mm用の装置を設計してきた。今後は、このプロセスが半導体の全製造工程に使えることを実証し、3Dチップのスタックを示すことになる。

参考資料

1. "The breakthrough that could simplify the 3D chipmaking supply chain", IBM (2022/07/07)