EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(3)〜レジスト

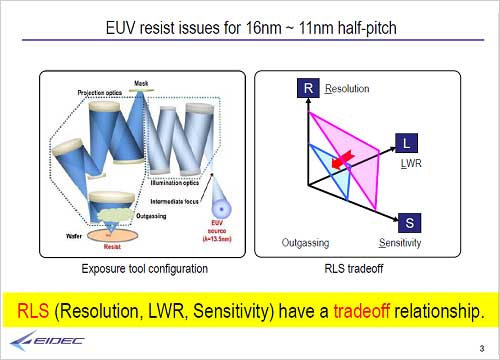

フォトレジストでは、昨年まではポジ型レジストを使い、解像度16nm以下、LWR(線幅の粗さ:line width roughness)1.3nm以下、感度10mJ/cm2以下、という数値を得ていた。解像度とLWR、感度の三つのパラメータはトレードオフの関係にあるため、三つのパラメータを最適化させる必要がある(図8)。今年は、ネガ型レジストを使ってどこまでいけるかの実験である。

図8 レジストのトレードオフ 出典:EIDEC

ネガ型レジストでは、パターンが崩れるという問題が起きた。どうやら原因は基板との密着性が乏しいことだった。このためまずは下地との密着性を上げた。トップデータとしてはL/Sとして18nmが得られている。

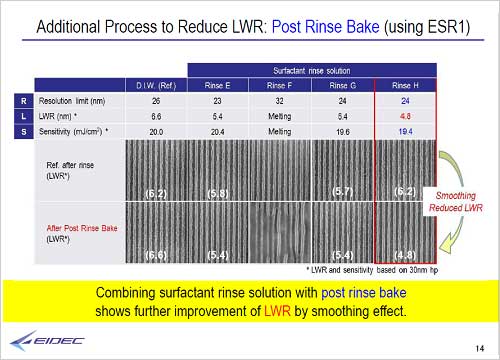

次に、現像後のリンス工程を見直した。露光→ベーク→現像→リンス→乾燥、という一連のフォトリソ工程の最後のリンス工程に注目した。ここでは、純水だけではなく界面活性剤の導入も試みた。さらにリンスと感想との間に、ベーク工程を入れるとLWRは改善された。実験ではLWRが6.2nmだったのが4.8nmに減少した(図9)。

図9 リンス後のベークによってLWRを減らした 出典:EIDEC

さらにLWRを減らすために、レジストのパターンがどのように現像によって溶けていくかをAFM(atomic force microscope)を使って調べた。AFMは細い針と試料表面との原子間力を一定にしながら、試料表面をその針でなぞることで凹凸をビジュアル化する手法であるが、現像液中で針を高速に振動させながらスキャンした。試料と針との間には現像液を注入、さらに純水を注入してリンスすることで描いて行く。レジストが感光し、現像液に溶けない保護基がどう作用するのか、このメカニズムをきちんと理解できればLWRを減らすことができると見ている。AFMを利用する手法はSelete時代に開発されたものだという。

レジストからのアウトガスは10年前から問題が出ていたという。Selete時代はガス相で捉えようとして、ガスクロマトグラフィで分析していた。しかし、ASMLは、ガスが発生して吸着されてもデバイスに悪影響を及ぼすのだろうか、という疑問を呈したという。このためにはアウトガスを直接観測する必要がある。さもなければデバイスメーカーに保証できなくなる。

これまでASMLは、電子ビームをレジストフィルムに照射してアウトガスによるコンタミネーション膜ができるとして、それをエリプソメータで膜厚を測ることでアウトガスの量を見積もっていた。さらにH2ラジカルによってカーボンに汚染された膜を洗浄した後、XPSによって成分を分析する(図10の左上)。

図10 アウトガス評価法の検討始まる 出典:EIDEC

ただし、電子ビームを照射することで実態を表しているといえるだろうか、とEIDECは疑問を投げかけ、評価手法を確立しようとした。EIDECは電子ビームではなくEUV光を直接当てることで、アウトガスが発生すると考えている(図10の左下)。やはりコンタミ膜の厚さ測定、H2ラジカル洗浄、XPS分析と同様に行う方法を進めている。基礎データが集まりつつある。

今年の4月から始まったDSAは、これから本格的に追求していくプロジェクトであるが、EIDECで扱うテーマとなったのは、リソグラフィとは独立に微細パターンを作ることができる技術の一つだからである。それもガイドパターンを形成しておき、ポリマーがそれに沿って自動的にアセンブリするという技術だ(図11)。EUVとDSAは相補うことで微細化が可能になる。EUVリソグラフィはASML1社しかプレイヤーはいないため、材料だけでパターニング出来る技術を日本が押さえておくべきだという意見も根強い。

図11 EUVとDSAの両方で10nm未満のパターンを加工する 出典:EIDEC

コンタクトやスルーホールのパターンにDSAの膜を付け熱処理すると膜は縮小するため、LWRは低減するだろうとしている。サブ10nmのL/Sを狙い、材料開発、寸法計測技術、シミュレーション、配線のオープン・ショート検査まで行う計画だ。

EUV開発では、露光機はASMLとIMEC、マスクやレジストの問題はEIDECとSEMATECHと、日欧米の3地域が共同して取り組むテーマとなった。この国際コラボレーションそのものも、その中心にコンソーシアムが3者入っているのも、初めての世界的なコラボレーションの試みである。成功させた暁には日本は再度、世界レベルの製造力を示すことができるだろう。

(このシリーズ終了)

参考資料

1. EUV時代が見えてきたか、IntelがASMLと歩調を合わせ10nmに照準 (2013/05/22)

2. EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(1)〜概要 (2013/05/31)

2. EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(2)〜マスク検査 (2013/05/31)