EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(1)〜概要

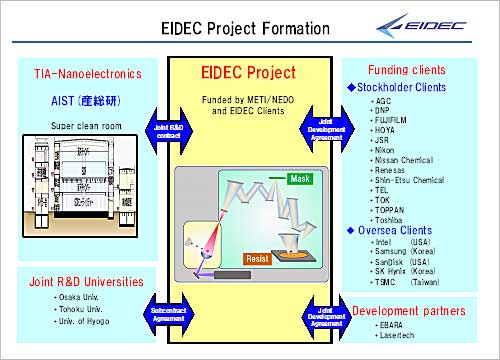

EUVのマスク、レジスト技術開発のコンソーシアムである、EUVL基盤開発センター(EIDEC)が最近の活動報告を行った(図1)。波長13.4nmのX線を使うEUVリソグラフィでは、ASMLだけが露光装置を開発しているが、EIDECは露光装置以外のEUV基本技術を受け持つ。出資は国内13社で、海外5社も共同研究で参加、荏原製作所とレーザーテックは装置開発パートナーとして参加、3大学と産業技術総合研究所も参加する一大コンソーシアムだ(図2)。

図1 EIDEC Symposium会場

図2 EIDECの開発プロジェクト構成 産官学+海外という世界規模のコラボになった

出典:EIDEC

これまで、ArFエキシマレーザー(波長193nm)を使って28nm、20nmと波長よりも狭い幅のパターンを加工してきた。光の波長よりも短いパターンを加工するためには、縦波と横波のどちらか一方だけを通すようにパターンを一方向に揃えなければならない。加えて、28nm以下の微細加工となると、ダブルパターニング技術を使わざるを得ない。微細なパターンでなければリソグラフィ工程は1度で済んだが、ダブルパターニングは1回加工したパターンの間をぬってL/S(線幅/線間隔)を半分にするため、もう一度加工する。このためプロセスマージンが減る。10nm以下の微細加工ではトリプルパターンは考えにくい、という意見も多い。3回の加工プロセスで一つのパターンを形成する訳だから、スループットも大きく低下する。

10数nmまではダブルパターン技術で何とかしのいできたが、10nmを切るような加工だとやはりEUVが必要とされる可能性は大いにある。EIDEC Symposium 2013では、IntelとASMLが10nm以下から液浸ArFレーザーとEUVとの併用という考えを明らかにしたが(参考資料1)、EUVの実現なしで微細化は難しくなってきた。EIDECプロジェクトは2011年度に始まり2015年度に終了する時限プロジェクトだ。終了までにEUVのマスクブランクおよびパターン付きマスクの外観検査と、EUVレジストとそのプロセスのメドを付けることが目標となっている。

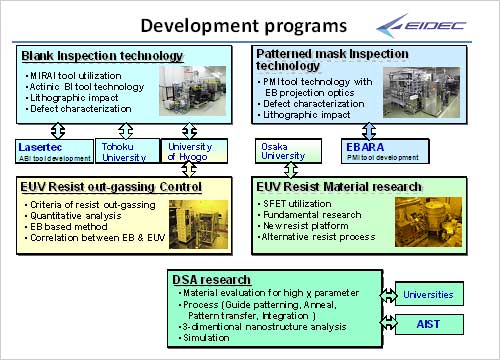

図3 EIDECの開発プログラム 出典EIDEC

図3に示すように、EIDECはこのシンポジウムにおいて、マスクブランクスの製造と検査の基本データが揃い、パターン付きのマスクはハードウエアが出来たことを報告した(参考資料2)。レジスト開発では、ネガ型レジストの進展、レジストのアウトガス検出評価技術を提案した(参考資料3)。さらに今回から、ジブロックコポリマーを利用して自動的に微細パターンを作るDSA(Directed self-assembly)技術もテーマに入れることを明らかにした。DSAとEUVを活用することで10nm未満のパターン形成を目指す。

(続く)

参考資料

1. EUV時代が見えてきたか、IntelがASMLと歩調を合わせ10nmに照準 (2013/05/22)

2. EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(2)〜マスク検査 (2013/05/31)

3. EIDEC、グローバル協力で10nm台の加工にEUV導入目指す(3)〜レジスト (2013/05/31)