TSMCがN2プロセスまでの戦略を発表、開発投資はますます巨額に

TSMCが8月30日に台湾でTechnology Symposiumを開催した後、今回は3年ぶりに日本に立ち寄りその概略を紹介、N2プロセスノードまでのロードマップを示した。ただ、1次元的な微細化寸法はもはや意味がなく、TSMCは1次元的なスケーリングから2次元的な面積スケーリングへとシフトしてきている。同社ビジネス開発のシニアVP、Kevin Zhang氏(図1)に同社の戦略を聞く。なお、9月28日に開催予定のセミコンポータル会員限定Free Webinarは「TSMC研究」がテーマである。

図1 TSMCビジネス開発担当SVPのKevin Zhang氏

微細化チップの実寸法が15nm前後で止まっていることは最近よく知られるようになった。例えばTSMCの7nmプロセスはIntelの10nmプロセスに近いといわれており、メタルピッチはいずれも40数nmである。特に16nmプロセスと称していたFinFETトランジスタを導入してからのプロセス技術がプロセスノードの数字と、実寸法との乖離が激しくなっている。もはや寸法の微細化(配線幅・配線間隔)はほぼ止まっており、1次元的な微細化スケーリングは、2次元的なエリア(面積)スケーリングへと変わった。

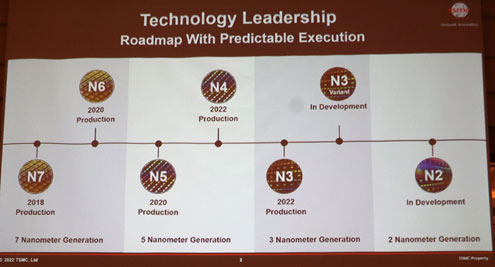

同社ビジネス開発のシニアVP、Kevin Zhang氏(図1)は、それでも微細化寸法を使ってプロセスの進展を表示している。ただ、さすがにIntelはnmプロセスとは言わず、7nmプロセス相当のPPA(Performance、Power、Area)であればIntel 7と呼び、TSMCはN7と呼ぶようになった(図2)。ただし、口頭では相変わらず7nm(ナノメートル)という言葉を使っている。

図2 TSMCが描く微細化の技術ロードマップ

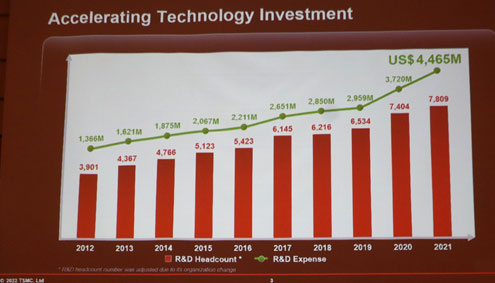

AppleのスマートフォンiPhone 13に使われているA14モバイルプロセッサはN5プロセスで生産されているが、2020年に生産開始したN5あたりから研究開発投資が急激に増えてきている。回路を作製した完成ウェーハ価格もN7の2倍近くに高騰しており(その分スマホの価格は高くなる)、2022年から生産が始まったN4、N5プロセスは、さらに高くなることが予想される。2021年には44.65億ドルを投資し(図3)、今年は40〜44億ドルを投資すると発表しており、2022年第2四半期決算時には、多分40億ドルに近い方になるだろうと述べている。

図3 TSMCの投資金額は増加の一途

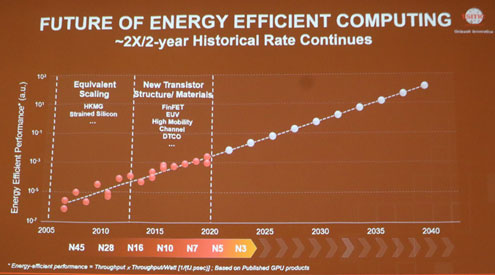

それでもTSMCは、2005年から2040年までエネルギー効率の良い性能指数を対数スケールで表現している(図4)。これは、ムーアの法則から、エネルギー効率の良いコンピューティング技術への転換を表現しており、今後もエネルギー効率を重視するコンピューティングが半導体技術の指導原理(Guiding principle)となる、とKevin氏は述べている。今の所、2年に2倍のペースでエネルギー効率の改善が続いている。

図4 エネルギー効率の良いコンピューティング技術をベースに半導体は進む

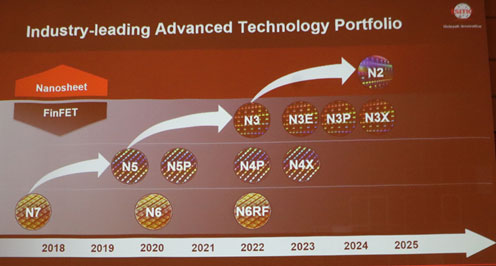

高騰する完成ウェーハ価格をユーザーがどこまで受け入れるだろうか。TSMCはメディア向けにはFinFETの次にナノシートを使ったGAA(Gate All Around)などの構造やカーボンナノシートなどのシリコンの次の半導体のイメージを見せるものの、現実的に厳しい投資に見合う価格をユーザーが受け入れてくれるかどうかはまだ見えていない。現在開発中のN2プロセスには、40〜44億ドルというCapexコストの内の7〜8割を占める、と同社広報スポークスパーソンのNina Kao氏は述べている。なおZhang氏は、ナノシートのN2プロセスの開発には非常にコストがかかり、大きなポケット(財源)が必要だと表現する。

N2プロセスノードが入手可能になるのは2024年以降になる見込みで(図5)、それまでの間はN3プロセスを伸ばしていく。

図5 N2プロセスは2024年以降を目標に

N3プロセスよりもエネルギー効率を上げたN3Eプロセスは、N5と比べて同じ消費電力なら速度は18%改善し、同じ速度なら消費電力は34%改善する。ロジック集積度は1.6倍になり、チップ上の集積度は1.3倍になると見積もっている。N3は2022年後半に量産を始め、N3Eは23年の後半に量産する予定である。

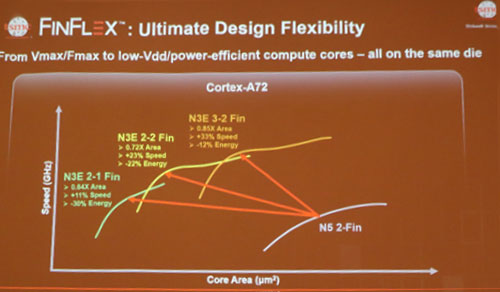

FinFETのFinの数をpチャネル、nチャネルで増やしたり減らしたりすることで、消費電力重視か速度重視かを使い分ける方針だ(図6)。例えば、ArmのCortex-72プロセッサコアに用いるFinFET構造で、2-1 Finでは、N5の2Finと比べ、面積は0.64にエネルギーは-30%、速度は+11%になり、3-2Finでは面積は0.85倍、速度は+33%、エネルギーは-12%となる。

図6 消費電力優先か速度優先かをFin数で選択

ナノシートを利用するN2プロセスはまだ開発の真っ最中で、量産時期を2025年に定めてはいるが、N3Eプロセスと比べて、同じ消費電力で10〜15%の速度改善、同じ速度なら25〜30%の消費電力改善、チップ集積度は1.1倍以上という目標を設定している。

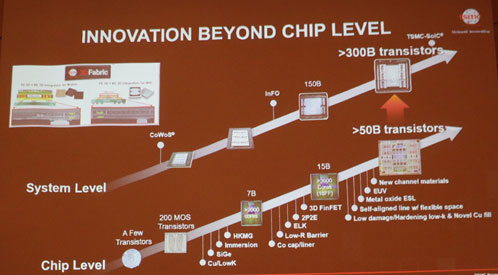

TSMCが3次元ICの開発センターをつくばに設立したが、やはりモノリシックだけでこれ以上突き進むにはコストがあまりにもかかりすぎる。N2プロセス以降は、コスト的に厳しくなる恐れが出てきた。そこで、チップレットやIPなど複数のダイをパッケージに実装するという3D-ICも同時に開発しておく必要がある。

同社のこれまでのチップの進展から見る限り、モノリシックなシリコンダイ上に集積するトランジスタ数は500億個以上にもなり(図7)、その進展が進むとしながらも、2.5D/3D-ICとなると、飛躍的に3000億トランジスタ以上を集積できることになる。

図7 チップレベルからパッケージによってシステムレベルに引き上げられる

現在は、モノリシックに集積度を高める方向で進んできたが、GAAやナノシート、グラフェンなどが使えるようにするための開発コストが下がらなければ、3D-ICの方向に行くことになる。しかし、もしナノシート、グラフェンなどの材料を安く安定的に製造できるようになると、モノリシックがさらに進展する可能性はある。今のところはまだどちらが優勢なのかは結論できない。TSMCの技術戦略を9月28日(予定)の会員限定Free Webinarで紹介する。