IBM研究所が2nmプロセスで500億トランジスタのICチップを試作

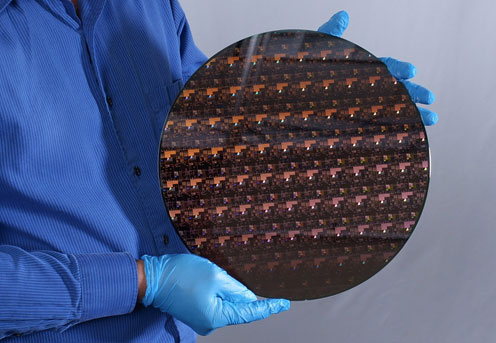

米ニューヨーク州アルバニーにおけるIBM研究所が2nmデザインのナノシート技術を使ったトランジスタを開発、このトランジスタを500億個集積したICテストチップを300mmウェーハ上に試作した(図1)。IBMは、PowerアーキテクチャのCPUを独自に開発しているが、今年後半に7nmプロセスのPower10をリリースするため、2nmチップが登場するのは2025年以降になりそうと見られている。

図1 IBMの2nmトランジスタ 出典:IBM Corp.

IBMはこれまで2015年に7nmのテストチップ、2017年に5nmのテストチップをそれぞれ開発しており、今回の2nmチップはその次に当たる。

今回業界初の2nmデザインICは、現在の7nmチップと比べ、性能が45%高く、消費電力は75%低いと見積もっている。IBMのプレスリリースに掲載されている「見積もっている」という表現は、まだ実測値ではなさそうだ。

2nmまで微細にすると、携帯電話のバッテリ寿命は4倍に長くなり、地球全体のエネルギーの1%を消費しているデータセンターではCO2排出が激減するとしている。さらに、ノートPCは翻訳が簡単にできるようになり、ブラウジングの速度も速くなるという。自動運転車のような自律システムの応答も高速になるとしている。

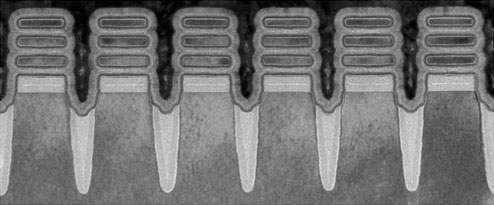

このトランジスタはGAA(Gate All Around)構造に見えるが(図2)、トランジスタ部分にナノシート技術を使っている、と記者会見に出席したSemiconductor Digest編集長のPete Singer氏は述べている(参考資料1)。図2には6個のトランジスタの断面を示しており、トランジスタ1個に3枚のナノシートを含んでおり、各ナノシートの幅は14nm、高さは5nmだという。トランジスタのゲート長は12nmで、トランジスタ間の分離にはバルクの誘電体分離を使っている。EUVリソグラフィでナノシートの幅を15~70nmに加工することができるという。各トランジスタのピッチは44nm。

図2 ナノシートトランジスタ断面 6トランジスタを示す 出典:IBM Corp.

IBMは7nmプロセスの時からEVUを使ってきたが、配線工程や多層配線工程に適用されてきた。今回は初めてトランジスタ工程でEUVを使ったとしている。今回の試作では、スタックトCMOS構成を取らなかったが、将来はありうるとしている。

将来の量産工程では、IBMはIntelおよびSamsungとは業務提携を結んでおり、彼らとエコシステムを形成しているため、2nmチップの製造はおそらくSamsungになるだろう。

参考資料

1. IBM Unveils World’s First 2 nm Chip Technology (2021/05/06)