28nmの次のプロセスノードは、14nm FINFETか20nmプレーナか

Mooreの法則のテクノロジーノードをスキップする動きが顕著になってきた。Alteraは、ハイエンドのFPGA SoC製品Stratix、ミッドレンジのArria製品を現在最先端の28nmプロセスで生産しているが、この次のプロセスノードをそれぞれ14nm FINFET、20nmプレーナCMOSと、変更する方針を発表した。製品名はいずれも10シリーズと命名している(図1)。

図1 Alteraの新SoC

UMCが汎用PDK(プロセス開発キット)を提供する製造技術として、28nmから20nmをスキップして14nm FINFETプロセスへ飛ぶことをすでに発表している(参考資料1)。今回のAlteraのハイエンド製品Stratixも28nmから14nm FINFETへ飛ぶ。この14nm FINFETプロセスは、Intelが製造するが(参考資料2)、正確には汎用のファウンドリではなく、Intelとの独占契約の製造委託(exclusive partnership)になる、とAltera製品マーケティング担当シニアディレクタのPatrick Dorsey氏は述べている。

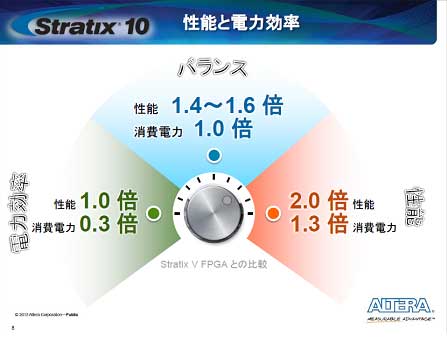

14nm FINFETプロセスを使うStratix 10の性能は、28nmの前世代Stratix 5ではクロック周波数が最大500MHzだったが、14nm FINFETプロセスのシミュレーションでは2倍の1GHzを示したという。この時の消費電力は1.3倍に高くなった。性能をStratix 5と同じ500MHzに設定すると消費電力は0.3倍となり、消費電力を前世代と同じに設定すると性能は1.4〜1.6倍に向上する(図2)。

図2 性能・消費電力を前世代Stratix 5と比較する 出典:Altera

Stratix 10には、CPUコアに加え、DSPコア、FPGAロジックエレメントなどを集積している。FPGA部分を入出力のトランシーバ回路として使うことが多いが、二重送受信の性能として56Gbpsの性能を得ている。FPGA部分は前世代の4倍の400万ロジックエレメントの集積度を持つ。DSPは、単精度の場合に10 TFLOPSと前世代の10倍の浮動小数点演算性能を得ている。

また、SRAMやDRAMを一つのパッケージ内に2.5次元あるいは3次元で実装する技術も準備しているという。いわばワイドI/Oのメモリによって、ロジック(Stratix 10)と高速にやり取りすることでシステム処理速度を向上させようという手法だ。

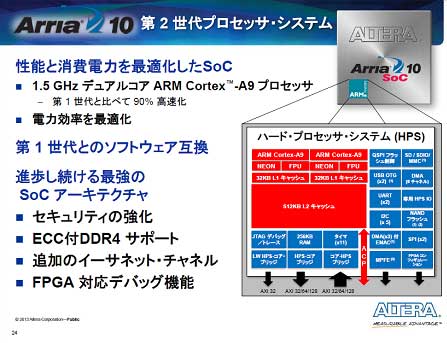

Arria 10シリーズもStratix 10と同様、フルFPGA半導体ではなく、CPUコアやキャッシュメモリ、浮動小数点ユニット回路などにFPGAを集積したSoCである(図3)。ただし、さまざまなインターフェース回路を集積し、プログラマブルなFPGA回路は少ない。演算用CPUにはデュアルコアのARM Cortex-A9 MP coreを集積、1.5GHzで動作する。TSMCの20nmLPプロセスを利用する。性能と低消費電力を兼ね備えた最良のプロセスだとDorsey氏は言う。

図3 Arria 10、FPGAというよりはSoC 出典:Altera

いずれのFPGAあるいはSoCについてもAlteraは開発ツールを用意している。ハードウエア設計者には、コンパイル時間を1/8に短縮できるQuartus II、MathWorksのSimuLinkのモデルベース設計とシミュレーションを利用するDSP Designer、ソフトウエア開発者には、Altera SDK for OpenCLを提供する。これにより設計の生産性が向上する。

参考資料

1. 台湾UMC、20nmをスキップ、14nmFINFETプロセスで巻き返し狙う (2013/05/30)

2. Altera、14nmのIntelファウンドリ、55nmフラッシュ、ロードマップを語る (2013/05/02)