インベンサス、新生テセラの半導体パッケージ企業として革新技術で再稼働

2012年はじめに日本オフィスを閉じたテセラ(Tessera)社。今は持ち株会社としての存在で、事業会社として半導体パッケージング技術会社のInvensasと、カメラモジュール会社のDigital Opticsを傘下に持つ新生テセラとして生まれ変わった。インベンサス(Invensas)は新型パッケージのソリューションを提供する研究開発会社として再稼働し始めた。

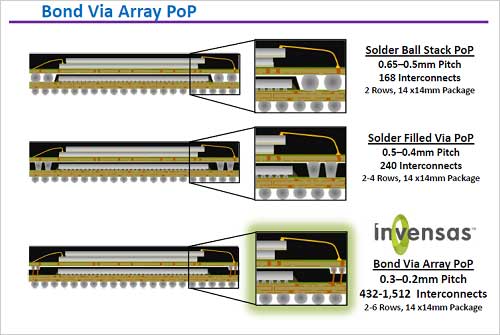

図1 立てたボンディングワイヤをPoPの接続に利用 出典:Invensas

再稼働の狙いは、「テセラのイメージを変えたい」、「日本市場でのインベンサスの認知度を高めたい」(インベンサス社の佐藤広陽氏)ことにある。米国に本社拠点を持ち、社員数は現在50名強。この内、1/3がPh.D(理学博士号)を持つ。インベンサスは、重要なパッケージング技術として、材料やメモリモジュール、3Dアーキテクチャに加え、設計も行う。設計を強化するため、メモリIPをMosys社から買い、TSVファウンドリのAllvia社のIPも購入した。このことでシミュレーション能力が高まり、ウェーハ工程も使えるようになった。

次世代パッケージング技術といえばすぐにTSV(through silicon via)を使う3D ICパッケージを思い浮かべるだろうが、3D ICを今すぐビジネスにつなげることは難しい。ファインピッチのパッケージを低コストでまだ作れないからだ。

そこで、インベンサスは今すぐ使える二つの新しい技術を開発した。一つは、パッケージサイズ14mm×14mmの標準パッケージにPoP(package on package)によって0.20mmピッチで6コラムだと、最大1440ピンを実現できる多ピン化技術である(図1)。広いバンド幅を使う用途に向く。例えばスパコンのような高性能コンピュータやビデオ伝送機器など、プロセッサとメモリ間のやり取りを高速で行うシステムの用途である。12.8Gbps以上の高速伝送に使えると見ており、TSVまでのつなぎ技術としても性能的には極めて高い。もう一つは、DRAMモジュールを低コストでしかも小さな面積でウルトラブックなどマザーボードに直付けしなければならない用途向けの技術である。

最初の多ピン化技術はBVA(bond via array)と呼ばれており、一つのパッケージともう一つのパッケージを向かい合わせに接着させるPoP技術に向く。従来のPoP技術だと半田ボール同士を接合するとボールがつぶれて隣接端子がくっつきそうになるため、ピッチの幅を十分広くとっておく必要がある。14mm×14mmパッケージだと0.65〜0.50mmピッチが最小であった。このためピン数を増やしたくても最大168ピンしか実現できない。最近では、アムコア(Amkor)社の持つTMV(through mold via)と呼ばれる、モールドに穴 開けして半田を接続する技術が登場し、より微細なピッチを実現しようとしてきた。アムコアはこの技術を新光電気工業にライセンス供与した。しかし、この技術でも0.5〜0.4mmくらいのピッチまでが限界で、240ピン程度までだとインベンサスの佐藤広陽氏は見る。

BVAは0.3〜0.2mmピッチと狭ピッチが可能なため、1000ピン以上が可能であるとする。このBVA技術では、ボンディングワイヤを立てて配置し、モールド(ワイヤ間のアンダーフィルの役割)でワイヤを固定した後、接続端子として使う。直径50μm程度のCuワイヤを使い、この上に半田ボールの端子を持つもう一つのパッケージを載せる。半田はCuワイヤ頂点でやや膨らむものの、その量を減らすことで狭ピッチに対応する。

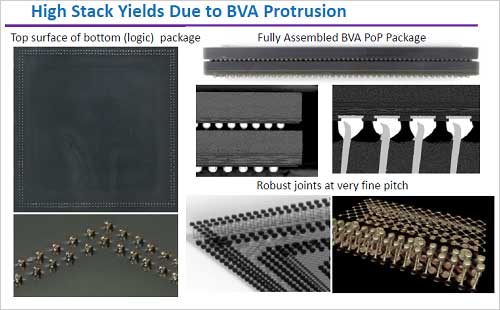

図2 Cuワイヤを接続パッドに使う 出典:Invensas

Cu ボンディングはすでに実績のある技術になっており、既存のボンダを使えるため新たな設備投資は要らない。接続する半田ボールに対して、Cuワイヤがモールド樹脂から顔を出している部分の高さはわずか0.1mm(図2)。これを実現するために、フィルムアシストのモールディング技術を使っている(参考資料1)。これは樹脂でモールディングする時に離型性を良くするためにフィルムを金型側に張った後に樹脂でチップの周りを満たそうというもの。モールディング時にはCuワイヤがフィルムを突き刺す形になり、フィルムを除去した後、図2のように一部が付き出るようになる。

このパッケージを使った高速メモリとロジックのPoPパッケージは2014年ごろから登場し、TSVによるワイドIOパッケージは2016年以降になるとインベンサスはみている。

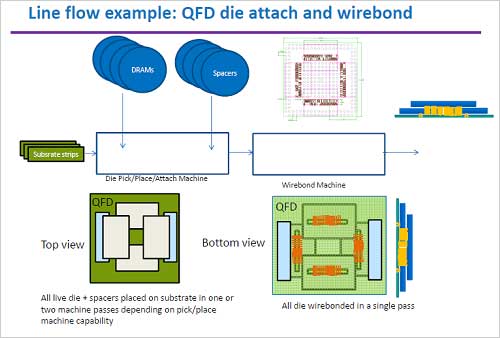

もう一つの技術であるDRAMモジュールの低コスト・小実装面積の技術では、QFD(Quad Face Down)と呼ばれ、17mm×17mm×1mm(厚)のパッケージに4個のDRAMを封止する。従来のスタック技術で4枚のDRAMチップを重ねる場合には、DRAMチップ+スペーサにワイヤボンディングして基板と接続した後、2枚目以降もDRAMチップ+スペーサを次々に重ね、ワイヤーボンド、という手順をシーケンシャルに行わなければならなかった。工程は長くならざるを得ない。ワイヤボンディングだけでも4回行う。

図3 DRAMチップ4枚をワイヤボンディング1回ですませる 出典:Invensas

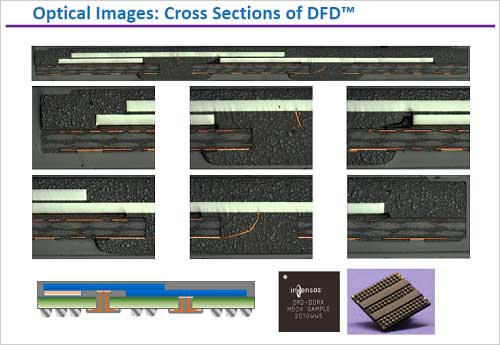

今回のQFDでは、DRAMチップをフェースダウンにして基板上に2枚離して置き、チップと同じ高さに揃えるためのスペーサも2枚置く。その上に別のDRAMチップをやはりフェースダウンで2枚、図3のように配置する。ワイヤボンディングはその後にまとめて行い、一度で済む。基板の穴を通して反対面のパッドにワイヤを接続する。断面は図4のようになる。工程が短く単純なためコストは安い。また、チップの重なりは2枚だけであるため、パッケージ全体を薄くでき、熱放散が良い。さらにボンディングワイヤは短くて済むため、高速性能は落ちない。

図4 QFD技術の断面図 出典:Invensas

パッケージコストは従来の4枚DRAMスタックの場合だと1.56〜1.67ドルであるのに対して、QFDは0.66ドルで済む、とインベンサスは見積っている。ちなみに1枚のシングルダイパッケージは0.2ドルだという。4枚分よりも安い。

ウルトラブックのようにメモリモジュールをマザーボードに直付けしなければならない用途では実装上のメリットも大きい。基板配線の引き回しを含めた実装面積が従来よりも27%程度小さくなるため、電池容量を大きくできPCの電池動作時間を伸ばすことができる。佐藤氏によると、このQFDパッケージだと12層のビルドアップ基板ではなく、安価な従来の12層基板を使えるという。

参考資料

1. 弱いLow-k材料や細い金ワイヤを守る低応力の新しいモールド技術2008/07/14)