TSMCが20nmのプロセスを来年第3四半期にリリース、14nmにも開発着手

最先端のIC開発では28nmの量産が始まったが、早くも20nmプロセスを2012年の第3四半期にリリースする、と台湾TSMC社のCTOであるJack Sun氏(図1)は語った。Sun氏は次の14nm以降についてもその見通しを語り、ここからはリソグラフィもデバイス構造も大きく変わることを示唆している。しかし、自信に充ち溢れている。なぜか。

図1 TSMCのCTOであるJack Sun氏

これまで130nm、90nm、65nm、40/45nm、28nmとやってきて、開発の着手から量産の立ち上がりまでの期間が実は、どんどん短くなっていることがその自信の裏にある。歩留まりに直接関係するパターンの欠陥密度は、130nmから40nmと微細になるにつれ、許容値以下になる期間が短くなっている。例えば、90nmプロセスでは生産量がピーク時の50%になるのに12四半期(3年)かかったが、28nmプロセスは4四半期(1年)しかかかっていない。ただし、この期間の裏付けとなる具体的なデータは講演で見せただけに留まり、予稿集にも掲載していない。Sun氏によると、28nmを量産してからのテープアウトの数は、40nmプロセスの量産を始めてから立ちあがるまでの期間が同じとしてほぼ2倍にもなるとする。28nmの歩留まりは「very good」と言い、自信満々である。

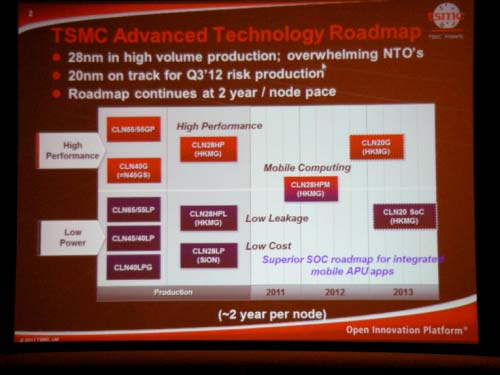

20nmについてはすでにSRAMの試作と動作確認を終えており、メモリだけではなくプロセッサやロジックICのレジスタなどにも使えるレベルに来ていることを実証した。英ARM社と提携しているTSMCは、ARMのCortex-A9デュアルコアをテープアウトしており、10月にも20nmプロセスで作るCortex-A15MPCoreをテープアウトしたことを発表している(参考資料1)。20nmのプロセス製品は性能を重視するCLN20G(HKMG)をまず提供し、次に低消費電力のCLN20 SoC(HKMG)を2013年から提供する(図2)。20Gは最新28nmプロセスの28HP、20SoCは28HPMとそれぞれ比べて、性能は2.1倍にスイッチング電力は0.75倍以下になると見積もっており、チップは35〜40%小さく、速度は20%以上速く、消費電力は30%以下に小さくなるとしている。

図2 2012後半から20nmプロセスをリリースする

20nmプロセスでは、ゲートラスト構造を使い、ゲート絶縁膜を密にしながら薄くすることで微細化にも対応し、配線部分は低抵抗のCu配線を使うなどの工夫を施している。Siの歪みに対してもGeの配分量を変え、SiNの部分にも工夫を凝らし、これまでのプロセスを進化させるといった微妙な工夫によって実現している。

20nmのリソグラフィでは、NA=1.35のArF液浸リソグラフィのダブルパターニングを本命として使い、マルチビームを使う電子ビームリソグラフィと、EUV(NA=0.25)も導入している。ダブルパターニングでは独自の設計ルールを作り上げ、カスタマが露光を2回に分けるためのマスクを作る必要はない。すべてTSMCがマスクを二つに分ける。

電子ビーム露光ではマルチビームのビーム本数を1万3000本に増やしウェーハ処理枚数として10 wph(wafers per hour)を計画しているが、現実のスループットはまだ1wphにも満たない。一方、EUV露光機としてオランダASML社のNXE3100を設置し27nmパターンをNA=0.25の反射光学系で4.5 wph以下という結果を得ている。

共に不十分ながらも14nmではどちらかの選択しかないとしている。マルチビームのEBではクラスタ構成で100 wph以上、EUVでもNA0.33の光学系で100 wph以上のスループットを目指している。

その次の14nmについても研究開発を始めており、MUGFET、FINFETなどのデバイス構造やGeをはじめとする高移動度材料を表面電子走行層に使うデバイスが検討に入っている。その実験として22nmのレイアウトで作ったFINFETを、昨年のIEDMで発表しているが、サブスレッショルド電流の傾きが70mV/decadeとプレーナ構造では得られない値を得ている。この値により、電圧を下げても動作できることを示し、逆にFINFETではなく従来のプレーナFETではもはやサブスレッショルド電流の傾きを下げられないため、トランジスタは使えないとしている。ちなみに14nmでFINFET構造だと0.75〜0.7V動作になりそうだとSun氏は予測する。14nmではSOIはもはや選択肢に入らない。SOIは相変わらずニッチ市場に使われるだろうが、メジャーにはなりえないと同氏は見ている。

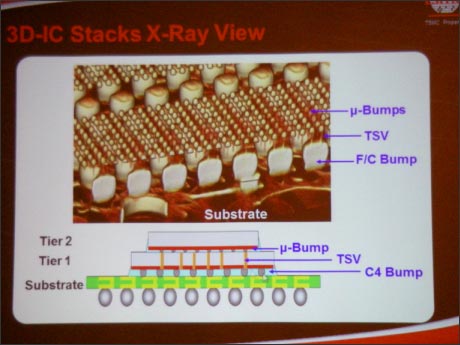

微細化とは別に高集積を達成する技術として3次元ICがある。TSMCはサブシステムインテグレーションとして、プリント配線基板上にDRAM8個とGPU1個のサブシステムを1パッケージに収めるSiインターポーザ技術を提案している。Siのインターポーザには多層配線を構成しておき、GPUとDRAMをその上にフェースダウンでマイクロバンプを通じ接続する(図3)。顧客名は語らないが、セミコンポータルで紹介したザイリンクスのVertex-7 FPGA4個をインターポーザ上に集積した技術と似ている(参考資料2)。

図3 Siインターポーザ上にTSVでチップと接続

450mmに関しては、もっとグリーンな工場を作ることを目指す。2013〜2014年には新竹市にあるFab12にパイロットラインを作り、生産は台中にあるFab15で2015〜2016年頃に始める予定だとしている。

参考資料

1. ARM and TSMC Tape Put First 20nm ARM Cortex-A15 Multicore Processor

2. 28nmのFPGAはインターポーザ利用でTbps実現、マルチコア内蔵で処理・解析用に (2011/10/26)