FD-SOI CMOSは20nm以降ではバルクよりも断然有利とSOIコンソーシアムが発表

完全空乏型(fully depleted)SOI CMOS技術は20nm以降のCMOS技術として性能、消費電力、コストの点でバルクCMOSと比べ有利になることをSOIインダストリコンソーシアムが発表した。このため携帯機器に使うべきSoCには向いていると同コンソーシアムの上級ディレクタを務めるHoracio Mendez氏は主張する。

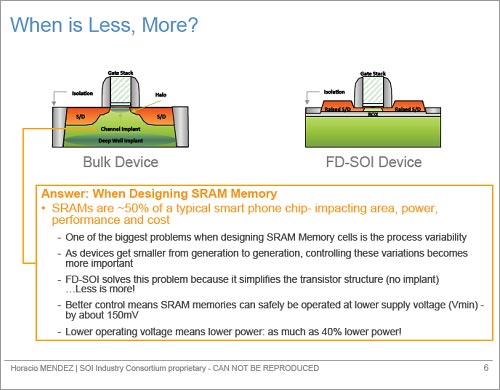

図1 完全空乏型SOI(右)とバルク型(左)のMOSトランジスタ構造

FD-SOI技術(図1)は、バルクCMOSと比べると短チャンネル効果が起きにくい。もちろん、MOSFETの動作原理から短チャンネル効果がない訳ではないが、ゲート長を短くしていくにつれ、ゲートしきい電圧Vthの低下が緩やかになる。このためバルクCMOSならVthの低下が急なゲート長でもまだフラットな状態を維持する。この特性は微細化する上で極めて有利である。電圧を下げても動作できるためだ。

短チャンネル効果が起きていないゲート長は、プロセスバラつきが少ないことを意味する。ゲート長がバラついてもVthはさほど変化しないためだ。この結果、SRAMセルの動作が安定になる。SRAMはプロセッサのレジスタやFIFO、キャッシュなどさまざまな所に使われる重要な回路である。これが安定にあればプロセスバラつきの少ないプロセッサを作ることができる。ARMのプロセッサをコアとするSoCなどに向く訳だ。

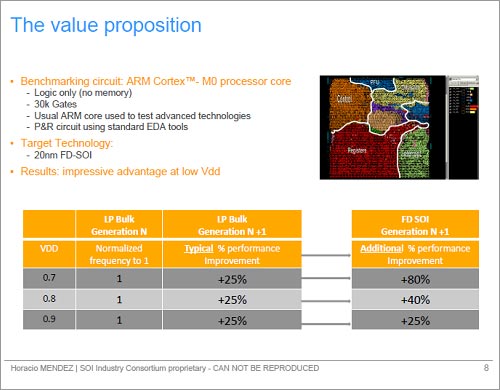

そこで、現実的なARMの低消費電力プロセッサコアの一つCortex-M0(ゲート換算で3万ゲート)を使い、シリコンベースのシミュレーションをバルクCMOSとFD-SOIのCMOSに適用し、比較した。その結果、ある世代の動作周波数を1とすると、バルクCMOSでは0.9Vから0.7Vにかけて25%向上した。これに対して、FD-SOI CMOSは0.9Vでは同じ25%改善だが、0.8Vで40%改善し、0.7Vだと80%も動作周波数が上がった(図2)。

図2 FD-SOI CMOSは電圧を下げられる点で断然有利になる

Mendez氏は、SRAMなどのメモリーには最適だとする。SRAMを安定に動かすためにはVthの揃ったフリップフロップが必要だ。同氏によるとバルクCMOSなら0.8~0.9V動作が現実的だが、FD-SOIなら0.65Vでも現実的だとしている。電圧が下がる分、性能よりも消費電力が大きく下がるため携帯機器に向く。複数の企業や大学の研究では150mV(0.15V)という低い電圧でもFD-SOIトランジスタは動作したことを確認している。

さらにプロセスコストも安くなるという。これはバルクシリコンと比べプロセスが簡単になるからだという。Mendez氏は、リーク電流やサブスレッショルド電流を抑えるため、バルクCMOSではVth用のチャンネルドーピングに加え、深いドーピングと、ドレイン・ソース接合近傍のハロードーピング(Halo doping)を行う。こういったプロセスステップがFD-SOIでは要らない。

さらにバルクCMOSでは微細になるとFINFETなど3次元構造のトランジスタが考案されているが、構造が複雑になり、コストは増大しリスクが大きい。これに対してFD-SOIだと、微細化と共にBOX(埋め込み酸化膜)も50nm程度と薄くなるため、基板バイアスをかけることができるようになる、というボーナス的なメリットも追加される。

次の段階ではFD-SOI CMOSを使うために現在、携帯機器メーカーと話をしており、さらに数ヵ月後には20nm以降の全てのバルクCMOSをFD-SOIに換えようと同氏は考えている。短チャンネル効果が少なくVthのバラつきが少ないということは、コンパレータや差動入力が豊富なアナログ回路にも有利である。

FD-SOIを進めるSOIコンソーシアムメンバーには、ARM、グローバルファウンドリーズ、IBM、STマイクロエレクトロニクス、Soitec、CEA-Letiがいる。さらに、SOIコンソーシアムとしては、プロセスファウンドリやIPプロバイダにも呼びかけ、微細なトランジスタのエコシステムを構築したいと考えている。