MIRAIプロジェクト、hp22nm以下時代のGeFETのデバイス指針を得る

MIRAIプロジェクトがhp22 nm時代に向けたMOSトランジスタの指針構築に向けてキャリヤ移動度の高いGe(ゲルマニウム)トランジスタの試作状況についてまとめた。これは12月中旬、茨城県つくば市で行われた「2009年半導体MIRAIプロジェクト成果報告会」で発表されたもの。このほど、スライドの使用許可をセミコンポータルにいただいた。

MIRAIプロジェクトがU-CMOS(新構造極限CMOSトランジスタ)と呼ぶトランジスタ技術の一環としてGeトランジスタは位置づけられる。今回の試作ではバルクのGeを用いたが、いずれGe on Silicon基板に集積されることをもくろむ。Geは最初にトランジスタが発明されたときに使われた材料。バンドギャップが小さく、安定な酸化膜ができないため、安定な酸化膜を形成できるシリコンにとって代わられた。

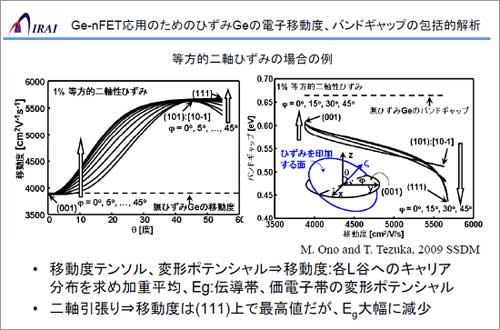

しかし、Geの高い移動度はやはり魅力的。理論的には4000〜5500cm2/Vsとシリコンの3倍以上の電子移動度を持つ。かつての弱点であった小さなバンドギャップに対しては、ひずみを加えて移動度を5500 cm2/Vsから4000 cm2/Vsに落としていくと理論的に広がっていく。現実に、Si上に薄いGe薄膜を形成するとGeはバルクよりもバンドギャップが大きくなる傾向があり、100℃くらいまで使える可能性はある、という。

さらに難題であった自然酸化膜形成には、Siの微細CMOSトランジスタがSiO2からhigh-k絶縁膜を用いるように代わってきていることがGeにとっての追い風となる。今でもGeO2やGeOは熱処理によってゲートリーク電流が増加するという欠点がある。

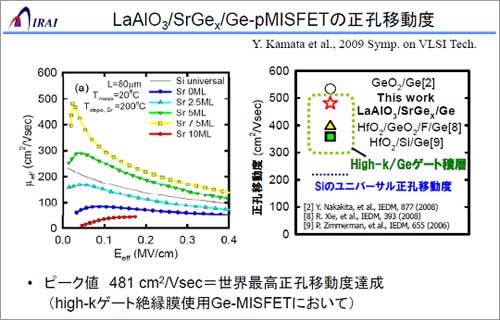

Geトランジスタの基本プロセスとして、high-kメタルゲート、Hf酸化膜系に代わるLaAlO3系をゲート絶縁膜に使い、チャンネルに歪を加えて格子散乱を減らす。ソースからの電子を加速するためのショットキーバリヤ接合、浅い接合のためのドーパントの拡散抑制など、をフル活用する。

試作したGeトランジスタは、Ge表面に原子層0〜10層のSr(ストロンチウム)をバッファとして堆積し、その上にLaAlO3を形成する。その後200〜800℃で熱処理してもhigh-k膜のLaAlO3からOが拡散することはなく、Ge表面のSrはSrGexという化合物が出来る。Srの量をゼロから10層まで増やすにつれ、ゲートリーク電流は激減する。しかもSrGex による等価酸化膜厚EOTは0.2nmしか増えない。

試作したpチャンネルMISFETの正孔移動度は、最大481 cm2/VsというシリコンのnチャンネルMOSFET並みの値を得た(下の図)。これは7.5原子層の時の値で、10原子層を堆積すると表面が荒れてしまい、移動度は却って減少してしまった。

ソース・ドレインの浅い接合に関しては、nチャンネルMISFETの試作ではP(燐)がGe中を速い速度で拡散するため、この拡散を止めるためB(ボロン)のストッパ領域を設けることで600℃で30分間、N2雰囲気中で熱処理してもPはほとんど拡散しないことがわかった。

ソースにショットキーバリヤ障壁を設けて、電子や正孔のエネルギーを持ち上げ、走行速度を上げるという試みを昨年、報告したが、ソース・ドレインのNiシリサイドの下にAsをイオン打ち込みすることでショットキーバリヤの高さを調整できることがわかった。Asの打ち込みドーパント量を2×10の14乗から4×10の14乗に変えることによってバリヤハイトは0.1eVから0.4eVへと変化した。

リソグラフィなど微細加工したゲート線幅がばらつくラインエッジラフネスによって、チャンネル長もばらつく傾向があったが、このAsの接合直下の偏析はむしろチャンネル長のバラつきを抑えるというありがたいボーナス効果もあった。ただし、トランジスタを多数試作してそのバラつきを調べるといったデータはまだ採っていない。