ARMの新IP、Cortex-R52は冗長構成でかつ高速化

ARMは冗長構成をとりやすくしたCPUコアである、Cortex-R52をリリースした。自動車のブレーキ機能や医療での投薬管理など、命に係わるミッションクリティカルなジョブに対して、冗長構成をとり、より安全性を高めたCPUコアである。Cortex-Rはリアルタイム性を実現しやすいコア製品シリーズ。

図1 ARM Cortex-R52は冗長構成のデュアルコアを2組備えられる

Cortex-Rシリーズは、ADAS(先進ドライバー支援システム)などクルマ用のプロセッサが演算や認識が終了した後に、クルマの次の動作を選択する「判断機能」などに使う。デュアルコアを用いて、二つのCPUコアに同期をとりながら同じ仕事をさせ、その処理結果が同じだった場合のみ実行する、という冗長構成を採る。この冗長構成を「デュアルコア・ロックステップ」と呼んでいる。

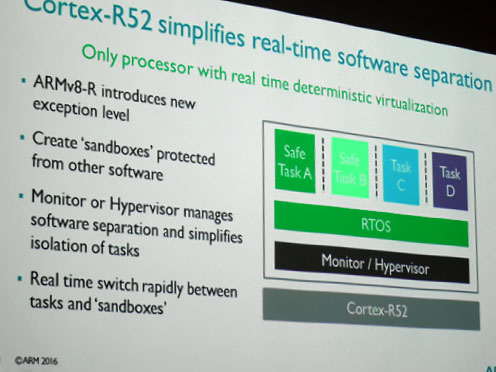

Cortex-R52では、図1のように、4つのコアとそれを制御するハイパーバイザとその動作をチェックするモニター回路を備えている。ハイパーバイザはソフトウエアの分離を管理しタスクの分離を簡単にする。モニターは単にその動作を確認する。

さらに、ハイパーバイザは、図1では一つのRTOSが4つのタスク(ソフトウエア)をカバーでしているが、RTOSを別の二つに分けてタスクA/Bと、タスクC/Dのグループに分けるという仮想化も行うことができる。クワッドコアの冗長構成であるため、冗長構成を仮想化によって二つ取ることができるようになる。ただし、これらは顧客のパートナーの要求によってARM側が構成を変える。

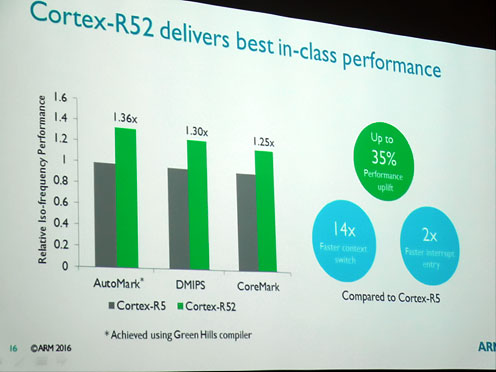

従来のCortex-R5では、同様な冗長構成だったが、デュアルコアであったために一つのジョブしかできなかった。Cortex-R52はこの冗長構成のデュアルコアを二つ備えた並列プロセッサ動作も可能であるため、性能はR5よりも向上している(図2)。ベンチマーク性能はR5の最大1.36倍、割り込みが2倍、コンテキストスイッチが14倍向上している。コンテキストスイッチとは、複数の処理を一つのCPUで共有できるようにするためにCPUの状態を保存したり復元したりする機能。マルチタスクや割り込み機能には欠かせない。

図2 Cortex-R52は従来のR5に比べ、ベンチマークでは高性能

Cortex-R52の機能安全はこれだけではない。もちろん、自動車の安全規格ISO26262に準拠し、冗長構成を活用して安全基準の最高峰(自動運転可能レベル)のASIL Dにも対応できる。バス配線の保護機能もある。これはメモリのECC(誤り検出・訂正機能)をバス配線にも拡張し、正しいデータが送受信されるようにデータを保護する機能。

SoCチップの開発時点では、ISO 26262準拠やASILの安全レベルをクリアするようにソフトウエアを構成しハードウエアを設計する。しかし、走行中のクルマがノイズなどで誤動作する場合には、冗長構成で対処する。Cortex-R52は、従来のR5よりも高速処理できるため、OSも含めてリアルタイムで判断とアクチュエータの動作を実行できるようになる。リアルタイム性を重視するパワートレインやシャシーに使う場合には、同じ種類のプロセッサコアを4個用い、並列動作の冗長構成によって、より早くより安全に動作する方式が向く。ADASのように演算性能を重視する場合には、Cortex-Aシリーズをマルチコアで使って高速演算を行いCortex-R52で安全設計を行う、というヘテロプロセッサコアのSoCが適している。