高集積は設計技術も困難に:設計技術編〜EuroAsia (3)

高集積ICへの要求は尽きない。しかもコスト上昇を抑え、高性能な独自機能を集積し、消費電力を上げない。高集積ICをどうやって設計するか。FPGAメーカーでさえ、ICの全機能をプログラミングすることが難しくなってきた。Alteraは一般的なC言語のOpenCLでプログラムすることを提案し、デザインハウスのSynapse Designは設計専用の計算機を開発した。

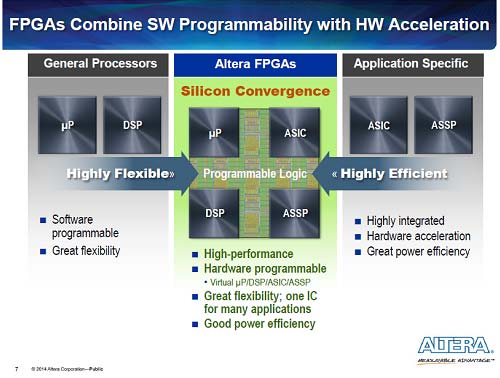

図1 SoCにはCPUやDSPのようなソフトウエアベースコアと、ASICやASSPのような専用コア、そしてプログラム可能なハードウエア回路であるFPGAを共存させる 出典:Altera

FPGAをOpenCLでプログラム

Alteraは昨年30周年を迎え、今や3000名の従業員を擁するFPGA企業になった。FPGA一筋でやってきた同社だが、FPGAのロジック規模があまりにも大きくなりすぎるとプログラミングに大変な時間がかかりもはや現実的ではなくなった。そこで、ソフトウエアベースのCPUやDSPと、専用IPコア、そしてハードウエアベースのプログラマブルロジックを共存させる方式のSoCへ代わりつつある(図1)。この方式だと、規格が絶えず代わるような回路はソフトウエアで、決まった回路を高速にしたい場合には専用IPを、高速回路をフレキシブルに変えたい場合はFPGAを使い分け、短い開発期間で設計できるようになる。

同社は、ハイエンドの応用としてデータセンターにおいて、一定の計算を高速に処理するために、FPGAの利用を提案している。検索アルゴリズムを最適化したり、CPUを並列動作させるためのアルゴリズムを実行したりする手段としてのFPGAである。その結果、検索機能では10倍、画像処理では9倍、そして金融関係の計算(ストックオプションの値付けやモンテカルロシミュレーションなど)では25倍も高速になったとしている。

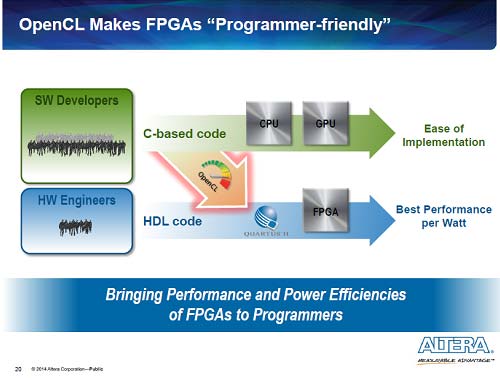

図2 CPUやDSP開発にC言語を使ってきたプログラマはFPGAの設計も可能に 出典:Altera

さらに高集積なアプローチにはOpenCLを導入する。これは、C言語をベースにしたプログラミング手法で、並列演算のマルチCPUコアや、GPUやDSPのコアが共存するヘテロジニアスなコアなどを利用した並列処理コンピュータに向くツールである。高集積のFPGAのプログラミングにOpenCLを使っていく。特に、クラウド検索のアクセラレータをAlteraは中国の検索サイト、百度(Baidu)と共同開発している。検索という決まった計算にFPGAで実行すると高速になるばかりではなく、CPUやGPUの負荷を減らすこともできる。これまでCPUなどのソフトウエア開発に携わってきたC言語プログラマは、今後OpenCLでハードウエア設計もできるようになる(図2)。

独自のクラウド計算機を持つSynapse

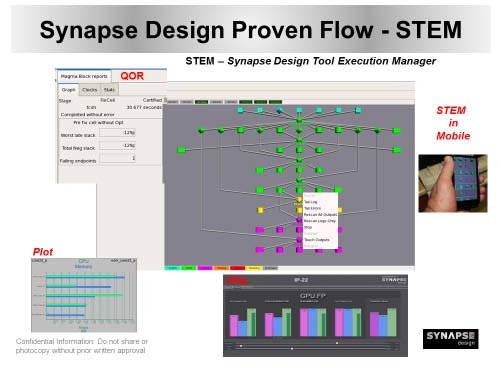

デジタルもアナログも設計できるデザインハウスのSynapse Designは、RTLに加え、Verlog-AとSPICEを持っており、ファーストシリコンで完全動作可能なチップを提供することを特長としている。独自開発したEDAツールのSTEM(Synapse Design Tool Execution Manager)を用い(図3)、正しい設計フローを管理している。最近の12ヵ月で33種類SoCを設計したという。このSoCには14nm FinFETや28nm FD-SOIに加え、28nmHPM/HPL/SLPなどの最先端のファウンドリプロセスも含んでいる。全て500mm2以上のチップサイズで、ファーストシリコンで動作したとしている。

図3 Synapseの設計管理ツールSTEM 出典:Synapse Design

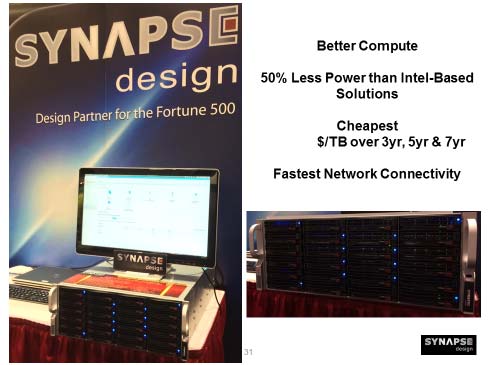

同社は、設計・検証に関する演算を高速にするため、専用のコンピュータ(プラットフォーム)をクラウド設計用に作った。Intelのプロセッサを使わずにFreescaleのT4240ネットワークプロセッサをCPUとして使い、消費電力を半減させたとしている。用いたOSは、オープンソースのクラウドOSであるOpenStackの最新版Icehouseである。SoC設計を、このクラウドコンピュータで実行する。このプラットフォームは、24個のプロセッシングスレッド、4チャンネルの10Gb Ethernet、8チャンネルの1Gb Ethernet、96TBのSSDを持つが、この構成を大きく変えられるコンフィギュアラブルなハードウエアでもあるという。データセンターの消費電力を減らしながら、演算速度を上げたためTCO(total cost of ownership)も削減できるという。

図4 開発したクラウド設計用専用コンピュータ 出典:Synapse Design

参考資料

1. 高集積は設計技術も困難に:設計ツール編〜EuroAsia(2) (2014/10/17)